LDO新手有简单问题急需求助

专题题目是2V~ to 1.8V LDO。因为只是要实作经验,教授完全没提供任何specifications!私自设定为

2~5V to 1.8V 50mA capacitorLESS LDO TSMC0.18um

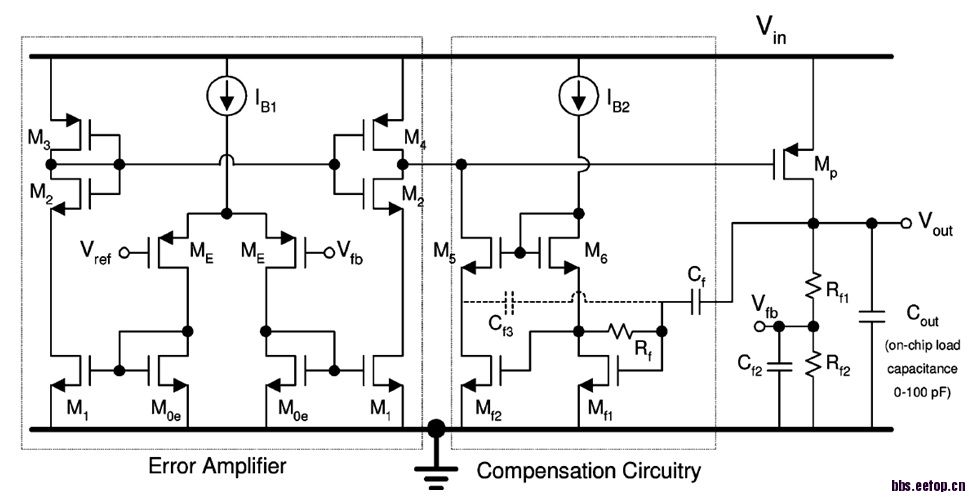

以下是采用架构: Full On-Chip CMOS Low-Dropout Voltage Regulator(2007) Robert J. Milliken

上图电路最早2007年提出,利用微分器當作动态补偿

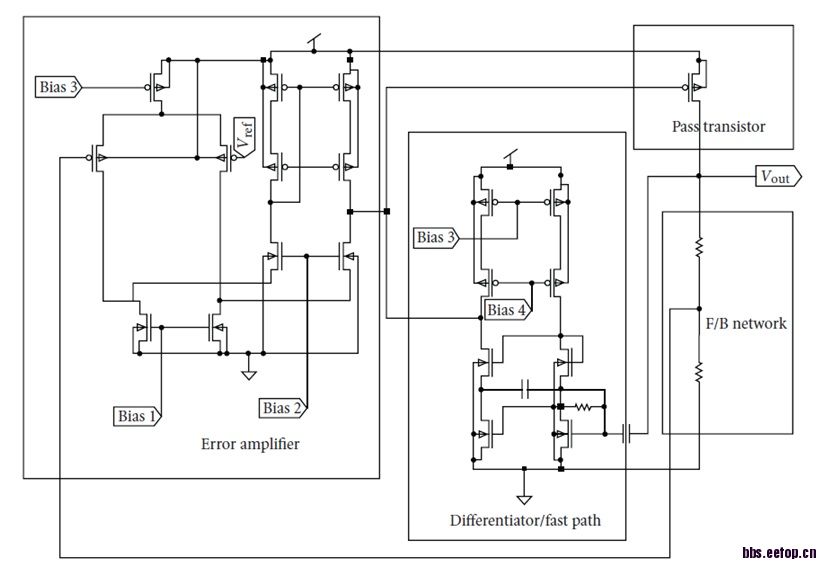

下图是2008年的另一种实践电路(原理一模一样) A Robust Low-Voltage On-Chip LDO Voltage Regulator in 180nm

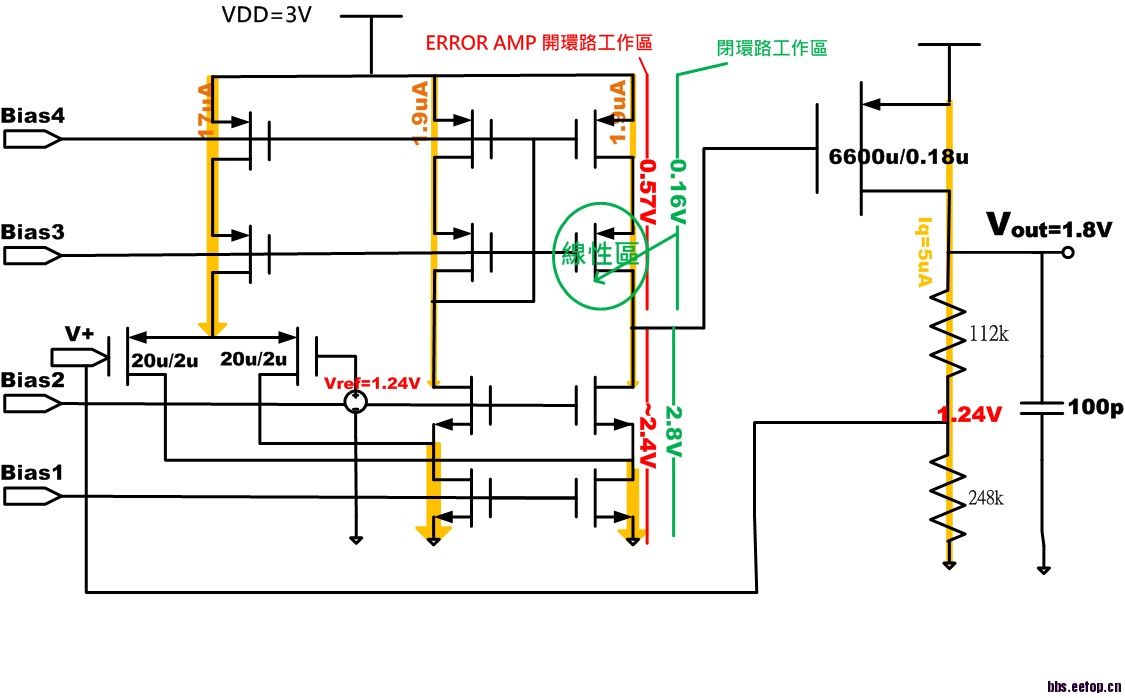

小弟首先设计未加入动态补偿下的稳态架构

问题一

ERROR AMPLIFIER 如下图所示有一颗在线性区,请问如何调整呢?

ERROR AMPLIFIER 规格:DC Gain 74db, 相位裕度85

GBW=2.25MHz

合理怀疑POWER MOS 在无负载下的电流因为只有5uA导致MOS位于Sub threshold 于是将电阻值减半(无负载电流加倍为10uA),但是Vgs也只能增加到0.18V

问题二

POWER MOS 管的DropOut电压由Vds,sat =sart(2*Imax/(KP*W/L))得到,KP经过精粹为288uA/V^2 得到W/L=6800um/0.18um 但参考的文件写出为W/L= 13000um/0.18um 请问该如何得到正确的KP

问题三

ERROR 的

slew rate特别差劲,就算是single stage OTA 也不至于如此,请问出了什么错误呢?

不知道你的偏置电流是多少.slew rate很差 可能造成的原因 我个人估计在于cascode两条支路电流没有配置好。你要保证cascade一路电流稍微大于folder的尾电流的一半。三森书上写的比较清楚。

另外,你的power 管子那么大,输出电流非常小,此时power管肯定处于亚阈值区。它的gate与source肯定只比vth低一丁点。如果此时EA的输出范围不够大,你所标识出的那个管子最先进入线性区。当负载电流增加时

,那个管子可以进入饱和区的。

另外,我对你的cascade负载的链接方式表示很怀疑。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:拉扎维习题求助

下一篇:求助:有人了解海思的信号完整性职位么