有关osc问题求助

录入:edatop.com 阅读:

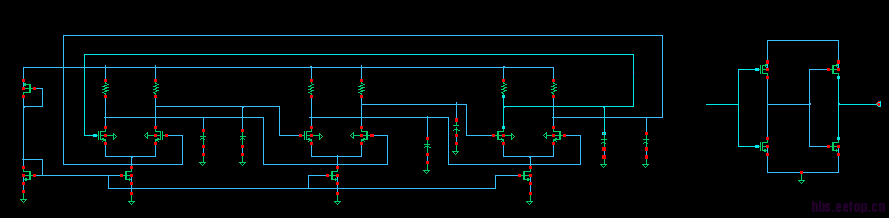

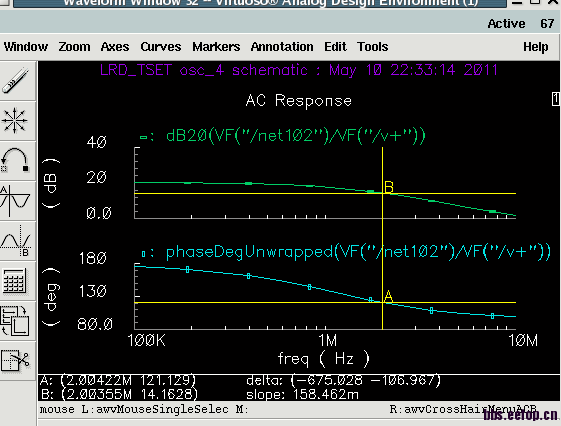

我对拉札维书上的osc进行仿真,设计指标vdd=1v,振荡频率2M,功耗小于1.5uw。

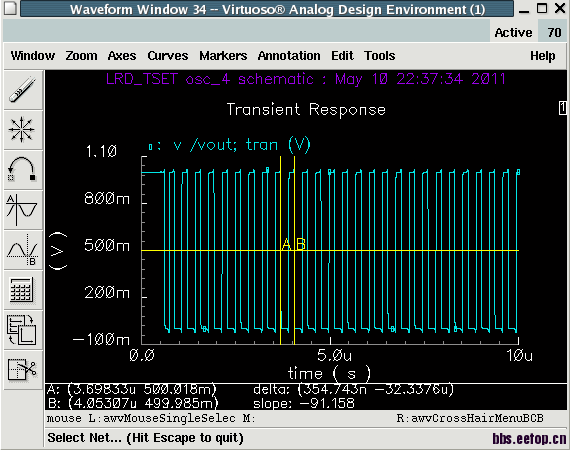

单级设计的话能够满足振荡频率2M的要求,并且总的功耗也满足要求,整体tran仿真后,输出后振荡频率变大了,并且占空比不为1:1,明显的低电平时间长,占空比将近2:1.

1 、为什么振荡频率会变大,问题出在了何处?

2、应该怎没去设计,使占空比为1:1?

仿真电路及仿真结果如下,供参考!

请教高手指导!

hi

好好阅读razavi的书啊。

沒錯

再多看幾本書

基本上你這樣duty非50%是很正常的

正常的 很好的啊

为什么单级设计的频率和仿真出来的频率不一致,仿真的频率要大,如果考虑非线性的话,书上说频率应该变小才对呀!谁能说明原因呀!

主要就是想知道手算和仿真存在差距的原因?

看看1/3M的相移很小的,这点误差很正常,没什么问题

对于ring osc,小信号的震荡频率跟大信号的震荡频率不一样,前者由loop gain和phase决定(RC),后者由大信号每级的delay决定(主要是I)。

duty cyle是因为你的CML delay DC点跟inverter的DC点不一致,你需要ac couple到inverter,或者极大的增大PMOS的size。

THANKS

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:VCO仿真

下一篇:ADS的momentum仿真问题