恳求帮忙分析一下我做的运放“启动时间”仿真结果

录入:edatop.com 阅读:

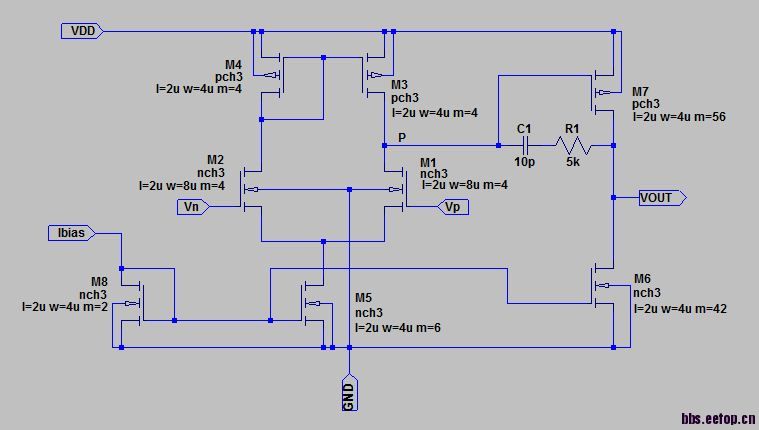

OP电路

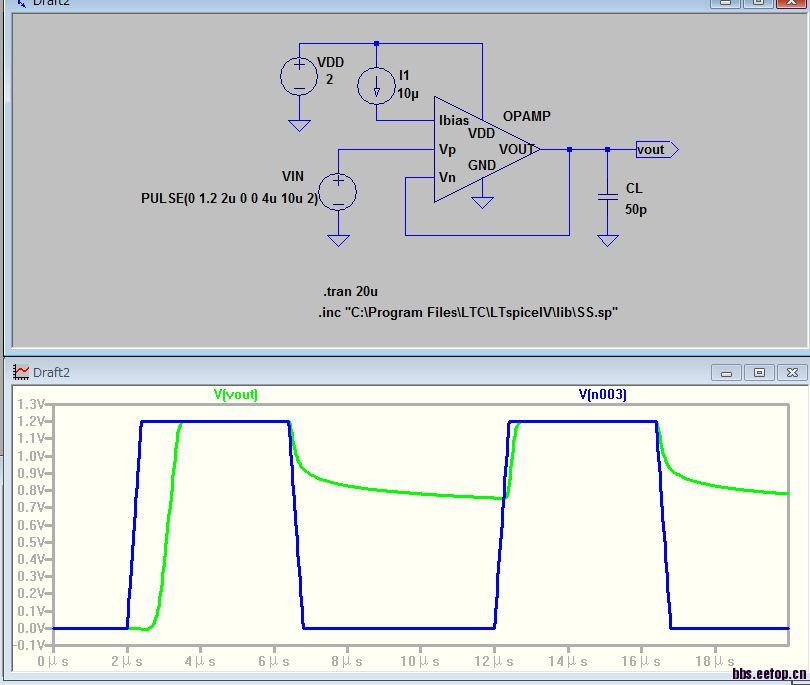

启动时间仿真

vout输出hold住了,不下降到0V,这种结果按道理可以解释,负载电容缓慢放电,所以hold住了。

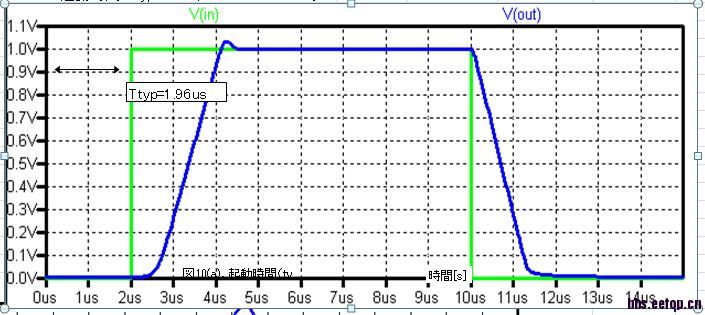

但是我看别人的仿真结果,不是这样的,是直接讲到0V,这是怎么回事,哪里出问题,恳求解答,不甚感激!

这是因为你的输入管是pmos,当输入为0v的时候,第一级输出不可能为vdd的,那么M7就不能关断,自然M6上得压降就不会为0v了,所以最后输出会固定在一个较高的电平上

输入共模范围不到0。所以当一端输入为0时,op已经不能正常工作,也就没有跟随功能。更仔细的分析应该就是p点不能达到高,最后一级不能被下拉

电路看着是正常的,还是把网表发出来吧

你的意思是别人的运放跟你一样,仿真曲线跟你不一样,还是说只是测试电路一样,运放不一样呢?

输入是NMOS,Vin=0时已经没有增益了

是lt-spice iv 用的是台积电0.18um的RF混合信号的库,应该支持吧,这个不大清楚,你网上搜搜吧

我刚用这个软件,而且也没有库,可否加我QQ:609890941 非常感谢!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:关于晶体振荡器精度问题

下一篇:求Abidi博士论文Effects of random & periodic excitations on relaxation