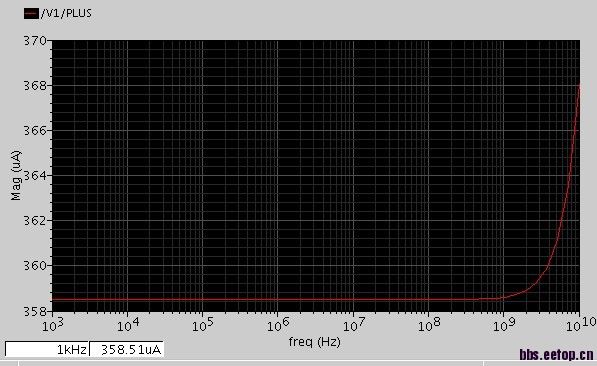

gm随频率的变化

录入:edatop.com 阅读:

我仿一个最基本的的MOS管的AC仿真特性,观察到MOS管漏端电流随着频率增加而增加,个人感觉不应该,不是应该变小的吗?

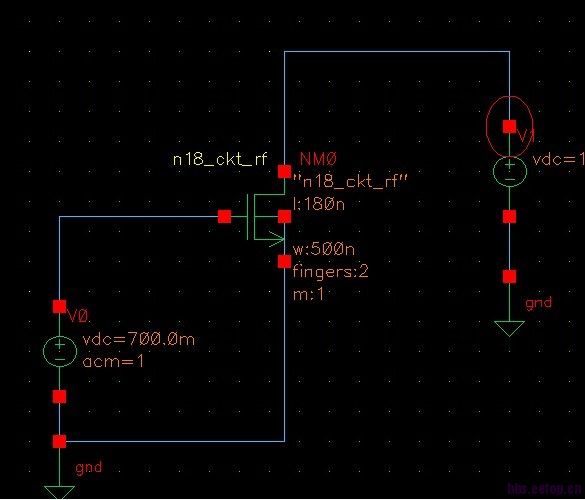

图片已上传,帮忙看看啊。电路栅极直流电压时0.7V漏极电压时1.2V,第一个图示做AC扫描获得漏极电流的值。

自己顶顶,希望有牛人回答下

输出阻抗减小。电流增加,嗯。我的理解。

你电路是怎么搭的?

应该是频率提高,gm下降。

请把电路图贴出来

无图无真相啊

图片已经上传了 又看看帮忙看看啊

我觉得不应该,如果这样的话,那MOS管的截止频率不没了吗?

我认为这是由于寄生电容引起的。当频率很高时,更多的电流将从寄生电容流过,所以AC仿真结果上电流增多了,我认为增多的部分主要由寄生电容引起。

我就是你这个观点。

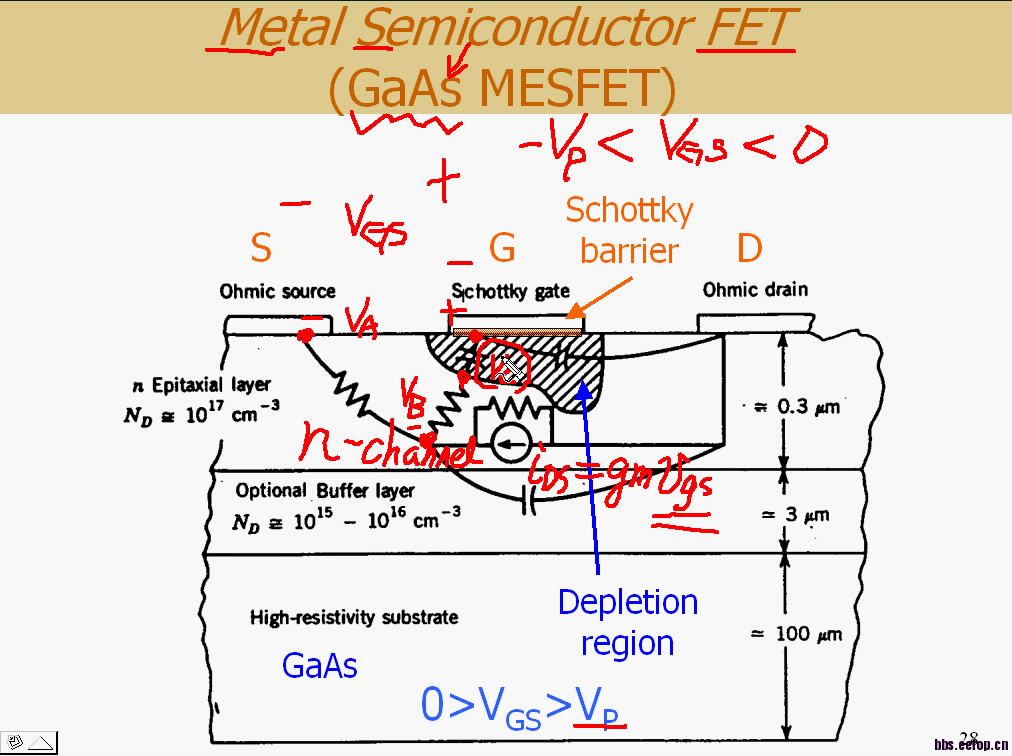

为什么会没呢?你的最高工作频率与低频跨导和寄生电容有关系哟。而你推导公式到最后你会看到你的最高工作频率与你的迁移率,过饱和电压,和沟道长度有关系的。每个mos管都有最高工作频率的。

还有就是,你可以写出你的MOS管的交流D端电流公式,你就看出了随着频率增加为什么你电流会增大了。

也就是9楼说的东西

可不可以当成当频率变高的时候,交流漏电流一部分是流过Cgd了,而且这部分还比较大,所以导致漏电流变大了

exactly

我认为,在一般的晶体管的分析过程中,没有考虑gm会随频率变化。

晶体管的极限频率:gm/(2π*Cgs)。在这里gm应该视为与频率无关的constant吧。

gm之所以会在Vgs信号为超高频时下降,是由于器件沟道的反型层跟不上Vgs的变化,Id自然也跟不上Vgs的变化。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。