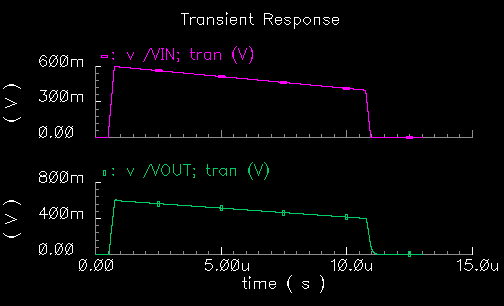

为什么我的Buffer的输入和输出之间有延迟啊,如图

我输入端加的从0到0.6V的斜坡信号,输入管是P管,为什么输出与输入不同时发生呢,是因为GBW不够吗

管子有寄生电容,应该会有延时呀

哪GBW和SR对这延迟的影响怎么样呢,我仿真了一下,把Iss增大了,延迟明显减少,而增大管子的尺寸却变化不明显,所以我觉得是SR也就是充放电的时间对延迟影响比较大,补充一下,这个延迟大约是20ns

ISS增大,充电时间加快,当然延迟减小,你增大管子尺寸,这个增大了电流同时也增大了电容,所以不明显。

还想问下,你增大MOS管时,你的ISS电流变化么?如果恒定,那么是增大延迟的哦。、

应该是SR的问题吧

增大输入管的尺寸肯定不会影响Iss啊,个人觉得还是SR的问题,与GBW没多大关系,但是还是有点不明白:GBW对运放的速度影响不是很大吗?为什么在这里我把gm增大了很多但是延迟还是很大啊,但是把Iss增大一点延迟就小了,难道SR对速度影响更多吗

单纯增大gm没用啊。在你增大gm的同时,你的其他参数也在跟着变,当你的gm达到一定阈值后,你增大了会很明显增大你的延迟的,而且你大信号的话,对SR限制着啊。不会有任何改善啊。

个人认为sr影响的更多点

看来sr影响很大啊

如果你的输入阶跃信号较小的时候,这时候是线性响应时间起主要作用,如果输入阶跃信号比较大的话,SR的会影响到建立时间

你这种情况应该是属于SR限制

没有延迟就不正常啦,设计delay单元的岂不要哭了 呵呵

没有延迟就不正常啦,设计delay单元的岂不要哭了 呵呵

学习!

GWB影响小信号,SR影响大信号,你图里面明显是算的大信号延时,当然SR占主导

分析一个电路有两种方法:小信号模型和大信号模型。都是电路在不同情况下的近似,带宽是小信号模型下得到的指标,而大信号下是要看SR的,也就是电容充放电的速度。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。