SFDR issues of single-ended and differential-ended

一个输出在芯片内部(通过内部电阻到内部的地,该电阻值与外部电阻大概相等),一个输出在芯片外部。测试SFDR时,发现二次谐波非常地高。

同一个电路,两个输出都在芯片外部,从同一输出上看频谱时,二次谐波非常小。

上述测试条件完全相同,输出信号频率也很低,时钟频率也不是很高。

请问,怎样解释这个现象?具体原因是什么?又该如何改善前者的SFDR特性?

非常感谢!

怎么没人理我呢!自己顶一下先

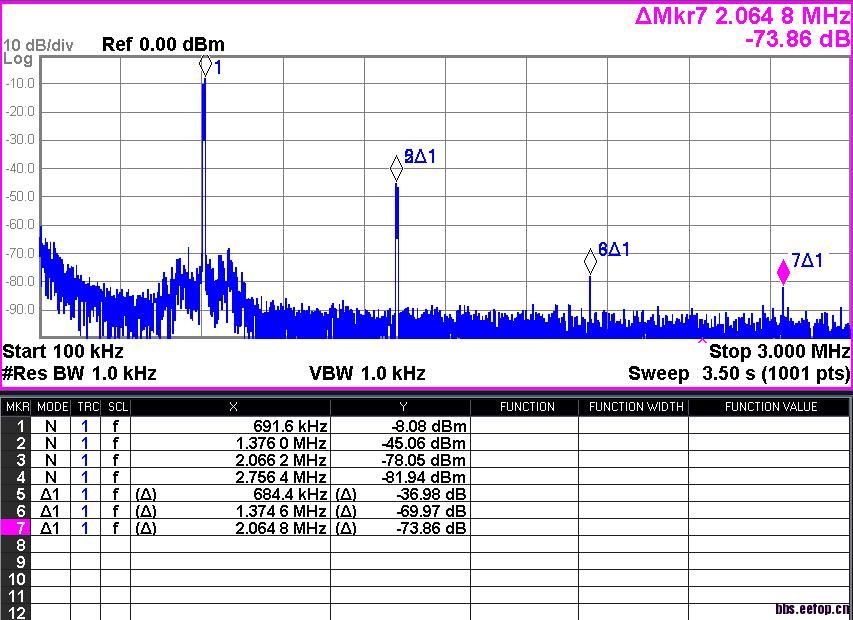

附一张单端输出时的频谱

还是没人理我:(

电路如果完全一样,结果应该是一样的啊。电阻接哪应该没啥影响吧

我也在做DAC,我很奇怪的是我的SFDR在输入频率为1M和20M时基本不变,时钟100M,SFDR大概有78dB,SNR有81dB

谢谢您的答复。

我刚开始也认为电阻接哪里是没影响的,事实上就是有差别,而且差别还很大。

你的SFDR在1M和20M输出时基本不变,不是挺好的吗?为什么会觉得奇怪?

还是没人答复呀!:(

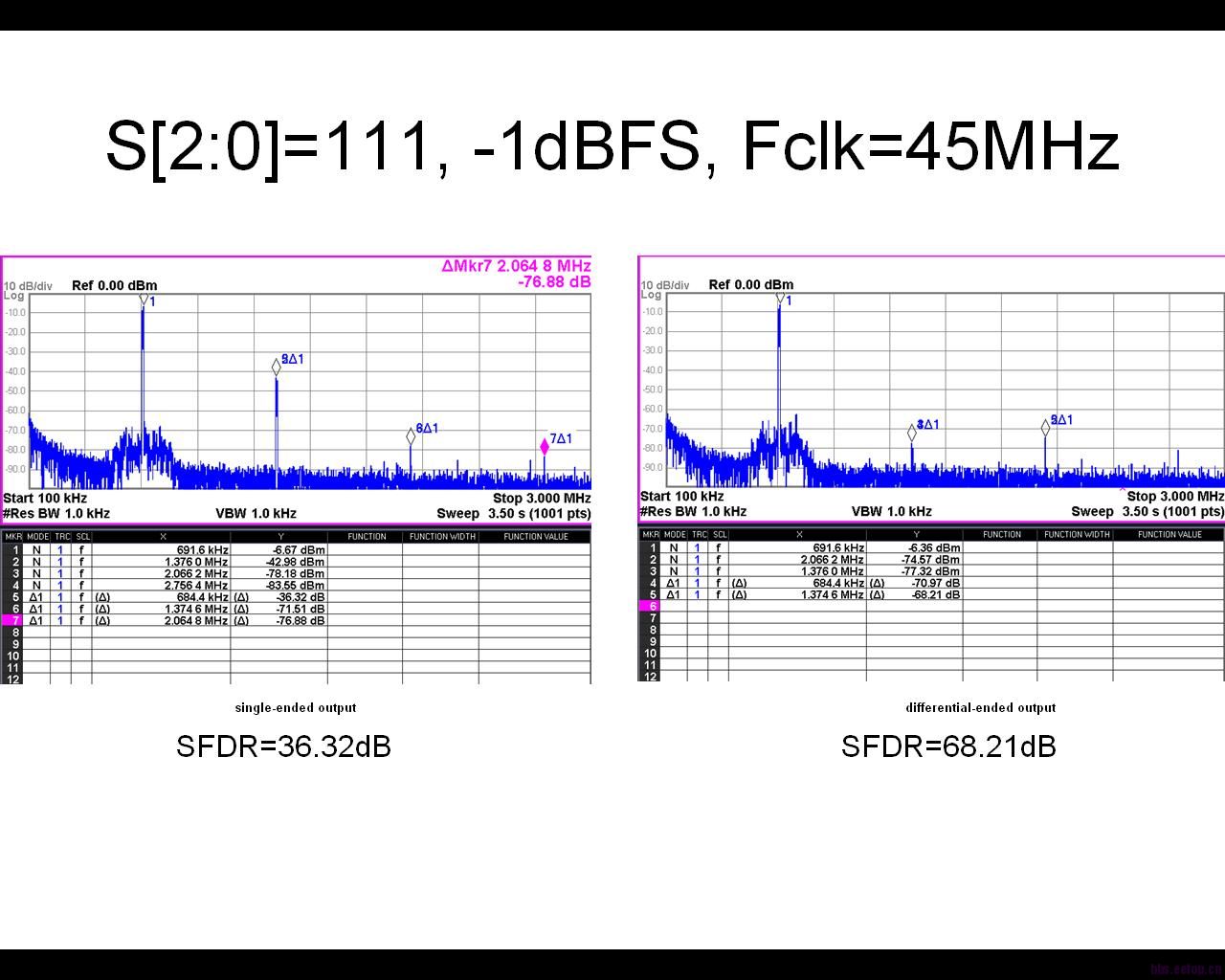

现在附上差分输出和单端输出的测试结果。

期待高人指点迷津!

一个输出在芯片内部(通过内部电阻到内部的地,该电阻值与外部电阻大概相等),一个输出在芯片外部。测试SFDR时,发现二次谐波非常地高。

---------你怎么保证输出是对称的?如果输出负载不对称,二次谐波应该就是会比较高吧

谢谢您的答复!

我在测试差分输出的电路时,曾经做过一个试验,把其中一个输出的负载电容给去掉(负载电容为10pF)。大概看了一下测试结果,没有明显变化。即使在这种输出并不匹配的情况下,二次谐波仍然比三次谐波低很多。

呵呵 不知道你的电路是否会是电容负载不敏感,但对电阻负载很敏感呢?

建议你对负载都在外面的电路,故意把两路的电阻负载做成20%。10%,5%,1%的mismatch来做一下测试,看看这时候的SFRD有明显变化吗?

非常感谢您的答复。

我倒从来没从这个角度想过这个问题。我会尝试一下您的建议。如果有新发现,我会及时更新。

祝你好运!及时找到问题

谢谢!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:chip assembly router

下一篇:请问比较器的分辨率怎么仿真?