LDO这个问题大家遇到过吗,是怎么解决的?

呢? 诚请高人解答,不胜感激!

呢? 诚请高人解答,不胜感激!

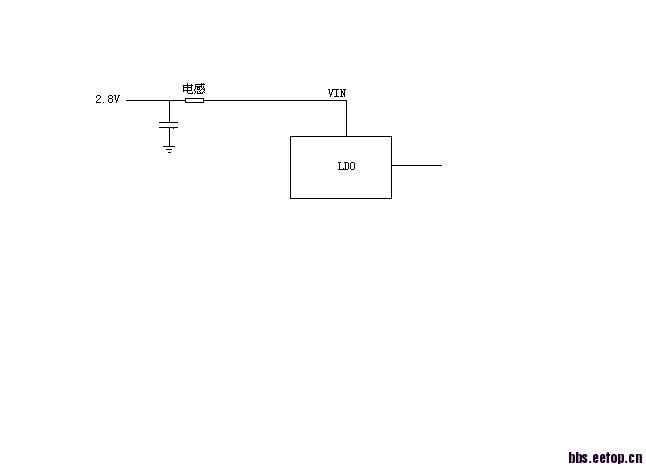

对了,另外由于金属长度不同造成的电阻不同对此没有任何影响,就是电感有影响,所以图中只画了电感

这也是一个系统稳定性问题阿,把ldo环路分析加入LC的影响,相当于芯片vdd没有等效接地。

在两个LDO spec上面找到的内容,看来就是说这个问题

Input Capacitor

An input capacitance of ≅ 1μF is required between the

device input pin and ground directly(the amount of the

capacitance may be increased without limit). The input

capacitor MUST be located less than 1 cm from the device

to assure input stability. A lower ESR capacitor allows the

use of less capacitance, while higher ESR type (like

aluminum electrolytic) require more capacitance.

Capacitor types (aluminum, ceramic and tantalum) can be

mixed in parallel, but the total equivalent input capacitance/

ESR must be defined as above to stable operation.

There are no requirements for the ESR on the input

capacitor, but tolerance and temperature coefficient must

be considered when selecting the capacitor to ensure the

capacitance will be ≅ 1μF over the entire operating

temperature range.

输入电容

1μF输入电容被连接在输入引脚和地之间(如果没

有限制,电容的值可以被增大)。这个电容必须放

在离输入引脚不超过1cm的位置,然后将其另一端

接到模拟地上。任何质量好的陶瓷电容、钽电容或

薄膜电容都可以作为输入电容。

个人感觉L4应该是正确答案,和我想的差不多。

不过我感觉是:离输入端远的时候是不是对输入的纹波没有起到过滤的作用?

都是高人啊,学习了

对于stability来说, pass transistor 看到的supply impedance 要越小越好,因为有那么大一个impedance,不管是inductance还是resistance,都会stabiliy产生影响。再退一步,就算没有影响,这个impedance也会让supply的transient response变坏。

应该是PSRR问题吧!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:请教Sansen书中1148图的轨到轨运放

下一篇:LDO的瞬态响应上不去