PLL Jitter过大

录入:edatop.com 阅读:

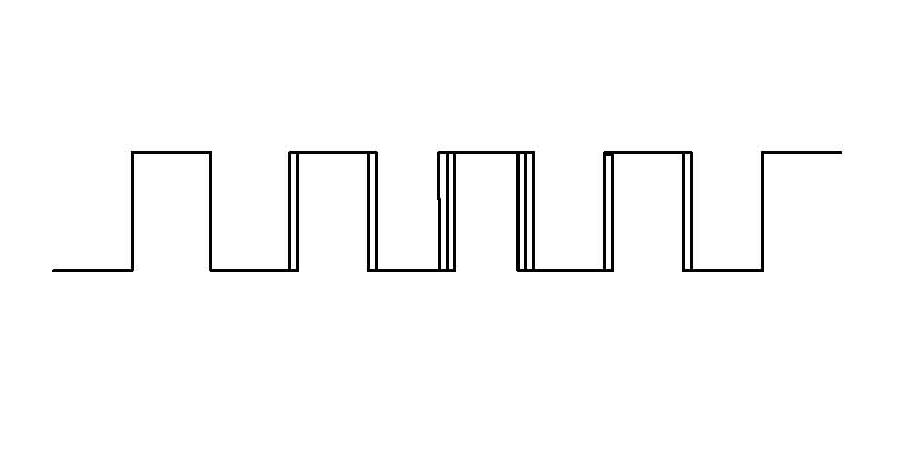

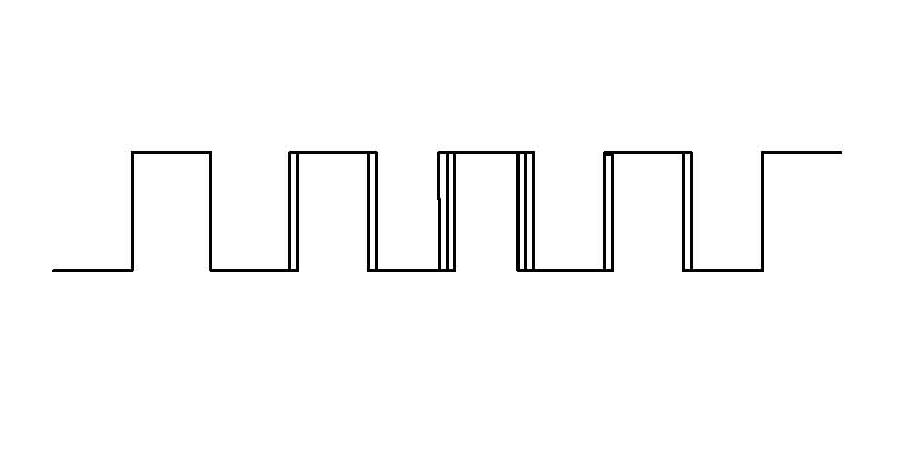

PLL输入27MHz, 输出108MHz, 输出波形如下

仿真的时候Jitter很小,只有几个ps,测试Jitter很大,Jitter_p-p达到200ps左右,

观察输出波形4个周期中,两边的对齐,中间的那几个在抖动,仿佛输出被输入调制了一样,

然而设计PLL带宽是远远小于27MHz的。各位有没有遇到过这种情况呢?

仿真的时候Jitter很小,只有几个ps,测试Jitter很大,Jitter_p-p达到200ps左右,

观察输出波形4个周期中,两边的对齐,中间的那几个在抖动,仿佛输出被输入调制了一样,

然而设计PLL带宽是远远小于27MHz的。各位有没有遇到过这种情况呢?

看看PLL的控制电压是什么样子?

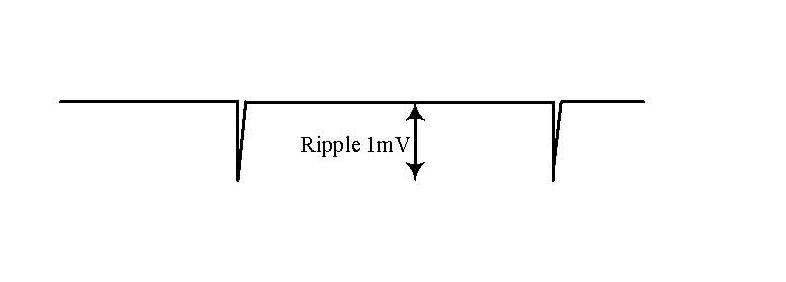

控制电压跟平常一样,在charge / discharge 的时候有一定的纹波, 1mV左右,应该不影响

如下图

你是用LDO供电吗?

另外,仿真PLL时,不要仿真抖动,而要仿真相位噪声。测试的时候也要测试相位噪声,测试抖动很难,也不准。

是用的LDO供电,

PLL仿真相噪不好做,要报错,测试仪器也还没熟练,就是示波器看到的那样的波形,两边好,中间抖,什么原因呢?

可以接频谱仪看看spur,感觉看起来输出抖动的频率和时钟一样。

小编仿真的时候拿什么和怎么仿的呢?

频谱在输入27MHz处肯定有spur,不用看都知道,现在就是找 造成这么大干扰的原因。

仿真用的spectre

你的LDO是片外还是片内的?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。