数字逻辑

录入:edatop.com 阅读:

各位大虾

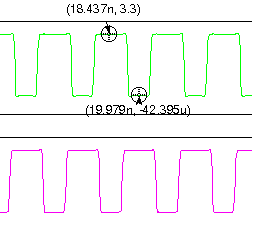

如图所示的上下两波形:波形A 产生高电平时,波形B 产生低电平,并且波形A 高电平的脉宽要比波形B此时低电平的脉宽大。

现在当出现这样的上下波形时,输出为0;

当波形A 和波形B 都为高电平时,输出为1, 请问这样的数字逻辑如何设计啊!

如图所示的上下两波形:波形A 产生高电平时,波形B 产生低电平,并且波形A 高电平的脉宽要比波形B此时低电平的脉宽大。

现在当出现这样的上下波形时,输出为0;

当波形A 和波形B 都为高电平时,输出为1, 请问这样的数字逻辑如何设计啊!

脉冲

顶起啊,求帮忙啊

求帮忙啊

从你的描述看,最简单的实现你的电路的方法是用滤波电路。

首先你要知道重叠边沿的长度,然后设计一个慢速的逻辑电路,用慢速的上升下降沿来屏蔽掉错误的边沿即可。

仅仅是用与非门和或非门的结构呢?有办法么?

我暂时想不出有什么简单又纯粹的逻辑电路可以实现这个目标

其实我说的方法也就是逻辑电路加一个电容而已

呵呵,应该是个好办法,非常感谢你!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:答疑 基准电压源的产生

下一篇:采样开关和MDAC的Matlab建模之愚见