做过VCO进来帮一下忙

录入:edatop.com 阅读:

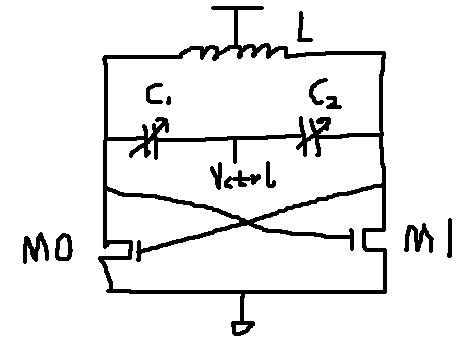

关于上图中的LC振荡器问几个问题

(1)振荡器的起振条件是M1和M2形成的负阻抵消L的寄生电阻么?

(2)M1和M2的尺寸越大,跨导就越大,负阻就越小,难道M1和M2的尺寸越大越不容易起振么?

(3)M1和M2的尺寸在设计VCO的时候应该怎么选取

(4)如何优化VCO的相位噪声,集成电感的Q值一般取多大呢,选电感值时,除了考虑振荡频率,还要考虑什么,是越大越好么

(1)振荡器的起振条件是M1和M2形成的负阻抵消L的寄生电阻么?

(2)M1和M2的尺寸越大,跨导就越大,负阻就越小,难道M1和M2的尺寸越大越不容易起振么?

(3)M1和M2的尺寸在设计VCO的时候应该怎么选取

(4)如何优化VCO的相位噪声,集成电感的Q值一般取多大呢,选电感值时,除了考虑振荡频率,还要考虑什么,是越大越好么

我没实际做过vco,试着回答下:

首先你这个结构PN在给定current consumption下,PN不可能很好,inductor的Q会被switching pair loaded.

M0,M1产生负阻来抵消inductor的loss,为了保证能启动,gm>3*gmin

电阻这里是并联的,尺寸越大,gm越大,一般越容易起阵,这个主要是对current biasing的来说,对你这种结构估计也是

取决于你phase noise要去,各个部分的Noise 的contribution,以及电路的线形度和寄生电容

电感值和tuning range有关,Q值一般是越大越好,如果你用集成电感的话

谢谢楼上的,有没有做过VCO的再给说说

?

自己顶一下,还有没有明白的给说说啊

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:IC战友们都来介绍下具有wifi频段低噪声放大器(LNA)成品芯片的半导体公司

下一篇:请教各位大侠如何仿真EMI?或者间接的通过什么得到EMI参数呢?