请教Verilog A的收敛问题。

把门电路中最后的赋值语句(transition语句)屏蔽掉就可以仿真,是不是赋值语句对收敛有影响?

可能是你替换了以后,没有对它的参数进行赋值吧。

请问怎么对其参数赋值?

下面是我写的一个带置位和复位的D触发器的代码,仿真时报出不收敛的错误。请帮忙查看一下。谢谢!

'include "discipline.h"

'include "constants.h"

module dff(D,CLK,NSET,NRST,PQ,NQ);

input D,CLK,NSET,NRST;

electrical D,CLK,NSET,NRST;

output PQ,NQ;

electrical PQ,NQ;

parameter real vth=1.65;

real PQdata,PQout,NQout;

analog begin

@(initial_step) begin //初始化

PQdata=0;

end

@(cross(V(NSET)-vth,-1)) begin //低电平置位

PQdata=1;

end

@(cross(V(NRST)-vth,-1)) begin //低电平复位

if(V(NSET)>vth) begin

PQdata=0;

end

end

@(cross(V(CLK)-vth,1)) begin //时钟上升沿到,跟随输入变化

if((V(NSET)>=vth) && (V(NRST)>=vth)) begin

if (V(D)>=vth) begin

PQdata=1;

end

else begin

PQdata=0;

end

end

end

if(PQdata=1) begin //给输出电平赋值

PQout=3.3;

NQout=0;

end

else begin

PQout=0;

NQout=3.3;

end

V(PQ)<+transiton(PQout,0.000000001,0.000000001,0.000000001); //电压输出

V(NQ)<+transiton(NQout,0.000000001,0.000000001,0.000000001);

end

endmodule

Here is a example from

http://www.designers-guide.org/VerilogAMS/functional-blocks/dff/dff.va

Just for your reference

//

// D-flip flop with clear or reset

//

module dff2 (q, qb, clk, d, s, r);

output q; voltage q; // Q output

output qb; voltage qb; // Q bar output

input clk; voltage clk; // Clock input (edge triggered)

input d; voltage d; // D input

input s; voltage s; // Set input (immediately forces Q output high) (active high)

input r; voltage r; // Reset input (immediately forces Q output low) (active high)

parameter real td = 0 from [0:inf); // delay from clock to q

parameter real tt = 0 from [0:inf); // transition time of output signals

parameter real vh = 1; // output voltage in high state

parameter real vl = -1; // output voltage in low state

parameter real vth = (vh + vl)/2; // threshold voltage at inputs

parameter integer dir = +1 from [-1:+1] exclude 0;

// if dir=+1, rising clock edge triggers flip flop

// if dir=-1, falling clock edge triggers flip flop

real out, outb;

analog begin

@(initial_step) begin

out = vl;

outb = vh;

end

@(cross(V(clk) - vth, dir)) begin

if (V(d) > vth) begin

out = vh;

outb = vl;

end else begin

out = vl;

outb = vh;

end

end

if (V(s) > vth) begin

out = vh;

outb = vl;

end

if (V(r) > vth) begin

out = vl;

outb = vh;

end

V(q) <+ transition( out, td, tt );

V(qb) <+ transition( outb, td, tt );

end

endmodule

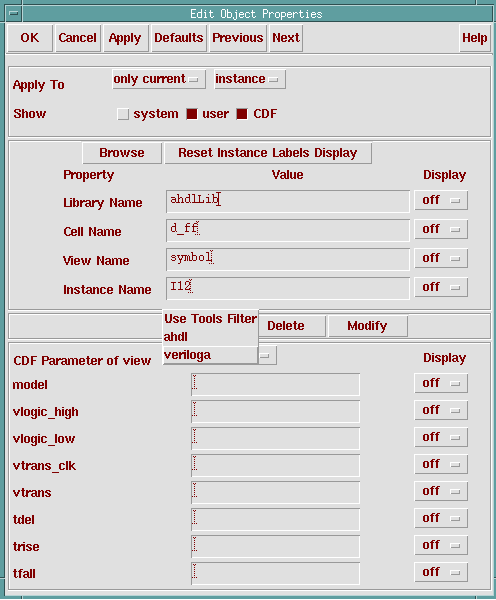

你在schematic里面添加dff 的 symbol后,用"q" 选择它的属性,最底下可以选择verilog-A 的,然后填入你的参数即可。

我按照_Ryu提供的例子输进去,仿真的时候还是会出现收敛问题,参数也按照iamxo说的那样设置了。具体得到的outlog文件如下;请帮忙看看:

Command line:

/root/cadence/tools.lnx86/spectre/bin/32bit/spectre -env \

artist5.1.0 +escchars +log ../psf/spectre.out +inter=mpsc \

+mpssession=spectre0_3041_20 -format sst2 -raw ../psf \

+lqtimeout 900 input.scs

spectre pid = 4459

Loading /root/cadence/tools.lnx86/cmi/lib/4.0/libinfineon_sh.so ...

Loading /root/cadence/tools.lnx86/cmi/lib/4.0/libnortel_sh.so ...

Loading /root/cadence/tools.lnx86/cmi/lib/4.0/libphilips_sh.so ...

Loading /root/cadence/tools.lnx86/cmi/lib/4.0/libsparam_sh.so ...

Loading /root/cadence/tools.lnx86/cmi/lib/4.0/libstmodels_sh.so ...

spectre (ver. 5.10.41_USR3.102405 -- 24 Oct 2005).

Includes RSA BSAFE(R) Cryptographic or Security Protocol Software from RSA

Security, Inc.

Simulating `input.scs' on localhost at 7:37:06 PM, Fri Jan 2, 2009.

Opening directory /root/Veriloga/dff/veriloga/veriloga.va.ahdlcmi/ (770)

Installed compiled interface for dff.

Notice from spectre during topology check.

Only one connection to the following 3 nodes:

vdd!

A

B

Circuit inventory:

nodes 6

equations 12

ahdl simulator 1

dff 1

vsource 4

Entering remote command mode using MPSC service (spectre, ipi, v0.0,

spectre0_3041_20, ).

************************************************

Transient Analysis `tran': time = (0 s -> 10 us)

************************************************

Matrix is singular (detected at `B' and `I12:NQ_flow').

Circuit has a nonisolated solution.

Trying `homotopy = gmin' for initial conditions.

Matrix is singular (detected at `B' and `I12:NQ_flow').

Circuit has a nonisolated solution.

Trying `homotopy = source' for initial conditions.

Trying `homotopy = dptran' for initial conditions.

Matrix is singular (detected at `B' and `I12:NQ_flow').

Circuit has a nonisolated solution.

Matrix is singular (detected at `B').

Circuit has a nonisolated solution.

Trying `homotopy = ptran' for initial conditions.

Matrix is singular (detected at `B').

Circuit has a nonisolated solution.

Trying `homotopy = arclength' for initial conditions.

Error found by spectre during IC analysis, during transient analysis `tran'.

Matrix is singular (detected at `B').

No DC solution found (no convergence).

The values for those nodes that did not converge on the last Newton iteration

are given below. Also given is the manner in which the convergence

criteria were not satisfied in the following form:

Failed test: | Value | > RelTol*Ref + AbsTol

The following set of suggestions may help you avoid these convergence

difficulties. Once you have a solution, write it to a nodeset file

using the `write' parameter, and read it back in on subsequent

simulations using the `readns' parameter.

1. Carefully evaluate and resolve any notice, warning or error messages.

2. Perform sanity checking on the parameter values using the parameter range

checker (use ``+param param-limits-file'' as a command line argument)

and heed any warnings. Print the minimum and maximum parameter value

using the `info' analysis. Assure that the bounds given for instance,

model, output, temperature-dependent, and operating-point (if possible)

parameters are reasonable.

3. Check the direction of both independent and dependent current sources.

Convergence problems can result if current sources are connected such

that they force current backward through diodes.

4. Enable diagnostic messages by setting option `diagnose=yes'.

5. Small floating resistors connected to high impedance nodes can cause

convergence difficulties. Avoid very small floating resistors,

particularly small parasitic resistors in semiconductors. Use voltage

sources or iprobes to measure current rather than small resistors.

6. If you have an estimate of what the solution should be, use nodeset

statements or a nodeset file and set as many nodes as possible.

7. Use realistic device models. Check all component parameters, particularly

nonlinear device model parameters, to assure that they are reasonable.

8. If simulating a bipolar analog circuit, assure the region parameter on all

transistors and diodes is set correctly.

9. Loosen tolerances, particularly absolute tolerances like `iabstol' (on

options statement). If tolerances are set too tight, they might

preclude convergence.

10. Increase the value of gmin (on options statement).

11. Use numeric pivoting in the sparse matrix factorization by setting

`pivotdc=yes' (on options statement). Sometimes it is also necessary

to increase the pivot threshold to somewhere in the range of 0.1 to 0.5

using `pivrel' (on options statement).

12. Try to simplify the nonlinear component models in order to avoid regions

in the model that may contribute to convergence problems.

13. Divide the circuit into smaller pieces and simulate them individually, but

be careful to assure that the results will be close to what they would

be if the rest of the circuit was present. Use the results to generate

nodesets for the whole circuit.

14. If all else fails, replace the DC analysis with a transient analysis and

modify all the independent sources to start at zero and ramp to their

DC values. Run the transient analysis well beyond the time when all

the sources have reached their final value (remember that transient

analysis is very cheap when all of the signals in the circuit are not

changing) and write the final point to a nodeset file. To make the

transient analysis more efficient set the integration method to

backward Euler (`method=euler') and loosen the local truncation error

criteria by increasing `lteratio', say to 50. Occasionally, this

approach will fail or be very slow because the circuit contains an

oscillator. Often times the oscillation can be eliminated for the sake

of finding the dc solution by setting the minimum capacitance from each

node to ground (`cmin') to a large value.

Analysis `tran' terminated prematurely due to error.

finalTimeOP: writing operating point information to rawfile.

Error found by spectre during DC analysis, during info `finalTimeOP'.

Analysis skipped due to inability to compute operating point.

Analysis `finalTimeOP' terminated prematurely due to error.

modelParameter: writing model parameter values to rawfile.

element: writing instance parameter values to rawfile.

outputParameter: writing output parameter values to rawfile.

designParamVals: writing netlist parameters to rawfile.

primitives: writing primitives to rawfile.

subckts: writing subcircuits to rawfile.

可能不是dff的问题。

注意到A,B都是浮空的,你可以试一试在A,B后接1k的电阻,看看是否收敛。

应该时diff的问题,我的也有相似的问题

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。