sc 仿真

录入:edatop.com 阅读:

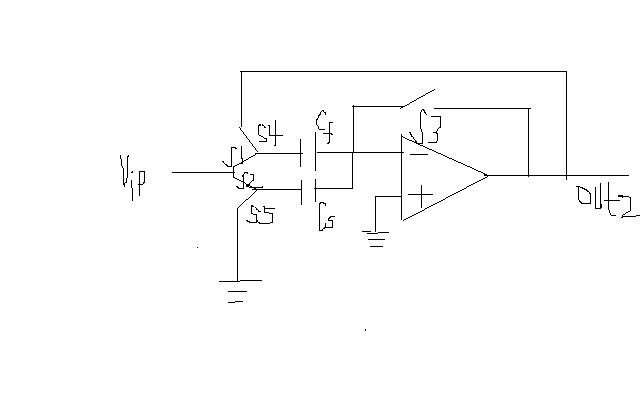

我按艾伦书 (中文版)356页设计了一个乘2电路,运放为折叠共源共栅,其开环工作正常,开环增益2000左右,0.18工艺,1.8----0电源电压,可是反复仿真了数遍,结果就是不对,麻烦帮我看一下。每次都是输出与输入基本是相同的,且改变电容的比例,结果也不变,还是与输入基本一样,

电路图基本描述

一个运放,两个电容,5个开关,s1 s2 为采样开关,s3为复位开关, s4 s5为放大的开关。

网表如下(hspice),麻烦大牛给看一下,是哪里不对,

*multi2

.options list node post

.lib 'F:\hspice\ms018_v1p4.lib' tt

.op

vdd vdd 0 1.8v

*out2 is output (single ended output)

m1 x in1 1 0 n18 l=0.2u w=1.2u

m2 y in2 1 0 n18 l=0.2u w=1.2u

m3 out1 b2 x vdd p18 l=0.4u w=3.2u

m4 out2 b2 y vdd p18 l=0.4u w=3.2u

m5 x 2 vdd vdd p18 l=0.2u w=1.4u

m6 y 2 vdd vdd p18 l=0.2u w=1.4u

m7 out1 b1 3 0 n18 l=0.2u w=0.2u

m8 out2 b1 4 0 n18 l=0.2u w=0.2u

m9 3 out1 0 0 n18 l=0.2u w=0.2u

m10 4 out1 0 0 n18 l=0.2u w=0.2u

m11 1 6 0 0 n18 l=0.2u w=0.2u

mb1 6 6 0 0 n18 l=0.2u w=0.2u

mb2 2 2 vdd vdd p18 l=0.2u w=0.2u

iref1 vdd 6 10ua

iref2 2 0 1ua

vin1 in1 0 0.9v

vb1 b1 0 0.75v

vb2 b2 0 1.05v

c1 out2 0 500ff

vip ip 0 0.8v

vg g 0 0.0v

mn11 i clk1 ip 0 n18 l=0.2u w=0.2u

mn12 h clk2 ip 0 n18 l=0.2u w=0.2u

mn13 out2 clk3 in2 0 n18 l=0.2u w=0.2u

mn14 out2 clk4 i 0 n18 l=0.2u w=0.2u

mn15 h clk5 g 0 n18 l=0.2u w=0.2u

cs h in2 200ff

cf i in2 200ff

vclk1 clk1 0 pulse(1.8v 0v 5ns 0.1ns 0.1ns 5ns 10ns)

vclk2 clk2 0 pulse(1.8v 0v 5ns 0.1ns 0.1ns 5ns 10ns)

vclk3 clk3 0 pulse(1.8v 0v 4ns 0.1ns 0.1ns 6ns 10ns)

vclk4 clk4 0 pulse(0v 1.8v 5ns 0.1ns 0.1ns 5ns 10ns)

vclk5 clk5 0 pulse(0v 1.8v 5ns 0.1ns 0.1ns 5ns 10ns)

.tran 0.1ns 20ns

.print tran v(out2)

.end

电路图基本描述

一个运放,两个电容,5个开关,s1 s2 为采样开关,s3为复位开关, s4 s5为放大的开关。

网表如下(hspice),麻烦大牛给看一下,是哪里不对,

*multi2

.options list node post

.lib 'F:\hspice\ms018_v1p4.lib' tt

.op

vdd vdd 0 1.8v

*out2 is output (single ended output)

m1 x in1 1 0 n18 l=0.2u w=1.2u

m2 y in2 1 0 n18 l=0.2u w=1.2u

m3 out1 b2 x vdd p18 l=0.4u w=3.2u

m4 out2 b2 y vdd p18 l=0.4u w=3.2u

m5 x 2 vdd vdd p18 l=0.2u w=1.4u

m6 y 2 vdd vdd p18 l=0.2u w=1.4u

m7 out1 b1 3 0 n18 l=0.2u w=0.2u

m8 out2 b1 4 0 n18 l=0.2u w=0.2u

m9 3 out1 0 0 n18 l=0.2u w=0.2u

m10 4 out1 0 0 n18 l=0.2u w=0.2u

m11 1 6 0 0 n18 l=0.2u w=0.2u

mb1 6 6 0 0 n18 l=0.2u w=0.2u

mb2 2 2 vdd vdd p18 l=0.2u w=0.2u

iref1 vdd 6 10ua

iref2 2 0 1ua

vin1 in1 0 0.9v

vb1 b1 0 0.75v

vb2 b2 0 1.05v

c1 out2 0 500ff

vip ip 0 0.8v

vg g 0 0.0v

mn11 i clk1 ip 0 n18 l=0.2u w=0.2u

mn12 h clk2 ip 0 n18 l=0.2u w=0.2u

mn13 out2 clk3 in2 0 n18 l=0.2u w=0.2u

mn14 out2 clk4 i 0 n18 l=0.2u w=0.2u

mn15 h clk5 g 0 n18 l=0.2u w=0.2u

cs h in2 200ff

cf i in2 200ff

vclk1 clk1 0 pulse(1.8v 0v 5ns 0.1ns 0.1ns 5ns 10ns)

vclk2 clk2 0 pulse(1.8v 0v 5ns 0.1ns 0.1ns 5ns 10ns)

vclk3 clk3 0 pulse(1.8v 0v 4ns 0.1ns 0.1ns 6ns 10ns)

vclk4 clk4 0 pulse(0v 1.8v 5ns 0.1ns 0.1ns 5ns 10ns)

vclk5 clk5 0 pulse(0v 1.8v 5ns 0.1ns 0.1ns 5ns 10ns)

.tran 0.1ns 20ns

.print tran v(out2)

.end

电路图please...

考验大家的眼力呀

电路图没有找到,自己画了一个

各位大牛,给回一下啊

很急 ,我是新手,小弟先谢过了

看网表那是没有时间的,电路图又是不清晰的

你的开关的相位,是不是全都都对?

先把自己搞清楚了,再来问问题。

附一个更清晰的电路图,一个时钟关系图

s1 s2 为采样开关,s3为复位开关, s4 s5为放大的开关。

采样与复位同时进行,即s1 s2 s3同时闭合;此后,s1 s2 s3同时断开,而s4 s5闭合,进行放大。

我实在是找不到清晰的电路图,请谅解,各位

麻烦给恢复一下,我很困惑

大牛们给小弟指点一下啊

用visio, powerpoint 之类的软件画一个原理图,opamp 另外画一个看看

问问题的态度要严谨才好啊

这样画图不好看

问题的态度要严谨才好

先把自己搞清楚了,再来问问题。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。