请教:为何pipeline中的SHA的SDDR随输入信号有明显的下降?

录入:edatop.com 阅读:

做了个14bit,100MHZ的pipeline的SHA,采样频率100MHz,当输入信号频率为10MHz时,SNDR=99.8db当输入信号频率为30MHz时,SNDR=83.5db,当输入信号频率为49MHz时,SNDR=76.5db

请教高手解答如何解决这个问题

你是测的还是仿的?

有没有calibration?

你看看ADI的datasheet,趋势都是这样子的,只是不知道你的值合不合理。

(99.8-1.76)/6.02=16.2857,难道你过采样后滤波了?

貌似你的SNDR计算方法有点问题。

这是用spice仿真后用matlab计算的SNDR的值,calibration还没有做

咋calibrate SHA 的非线性度?

应该是你的开关的线性度不好了吧

我觉得是:随输入频率增高,一是量化噪声增大,二是开关的线性度变差,造成谐波失真增大。

另外我想请问:为什么用spice而不用specture?。

建议加大和clock1e相连接的NMOS的宽长比,会有很大的改善。

谢谢 果然效果明显

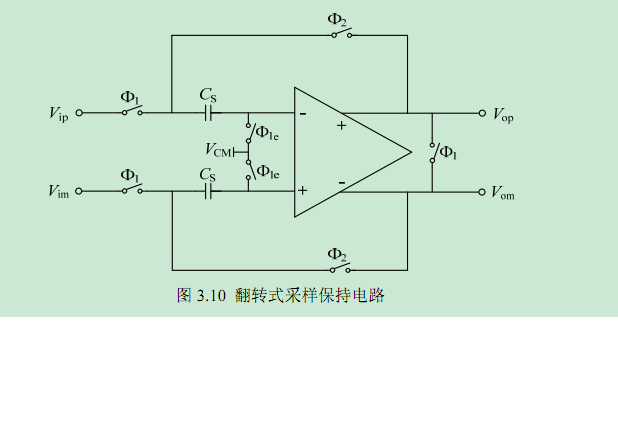

采用的SHA结构如图所示 在输入信号路径上的是采用bootstrape开关,和vcm1相连的开关

采用的是1000um/0.18um的NMOS(这个比例是不是不合理,看别的论文都是100//0.18),这个是不是证明我的bootstrape的线性度不够啊?

谢谢啦!

不能简单这样说。如果论文上的工作频率也是相近的,就不是这个原因。

自举开关中的电容大小也会影响开关性能。

论文中的采样频率 100MHZ 里边的开关从2p~4p 结果都一样啊?

2pF~4pF我觉得有点过大了啊,会占很大面积,而且速度也会受影响,1p应该足够用了。

另外你的运放性能可能不如论文中的,所以整体结果有差异。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。