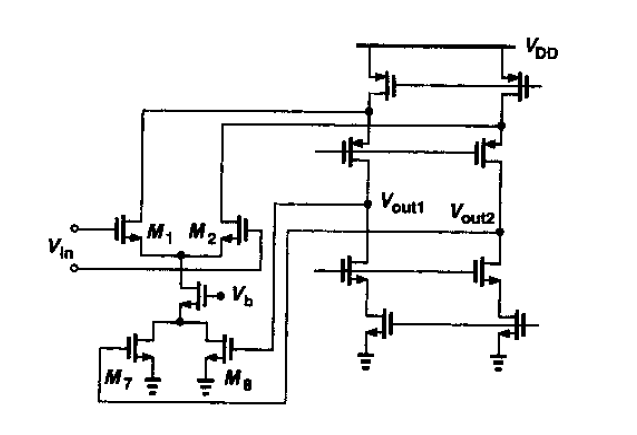

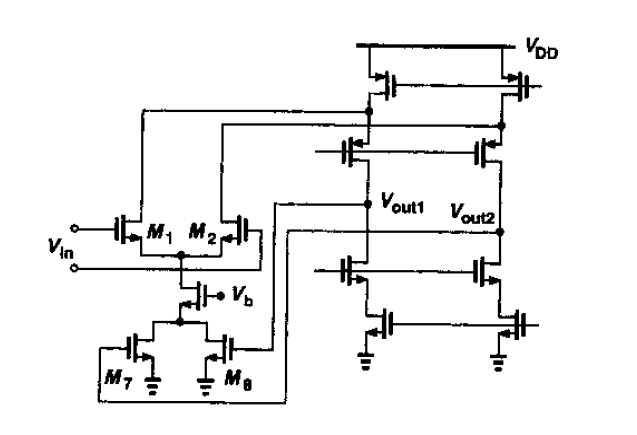

请教 这个电路图中的 vout1 vout2的变化趋势

对如下这个电路图1,当Vb高于所希望的值时,M1和M2的尾电流将增加,

那么共源共栅支路的电路将降低啊,那么vout1和vout2将提高,那么共模电平将增加啊。

图1

但是书上怎么说是:当Vb高于所希望的值时,M1和M2的尾电流将增加,输出共模电平将下降呢?

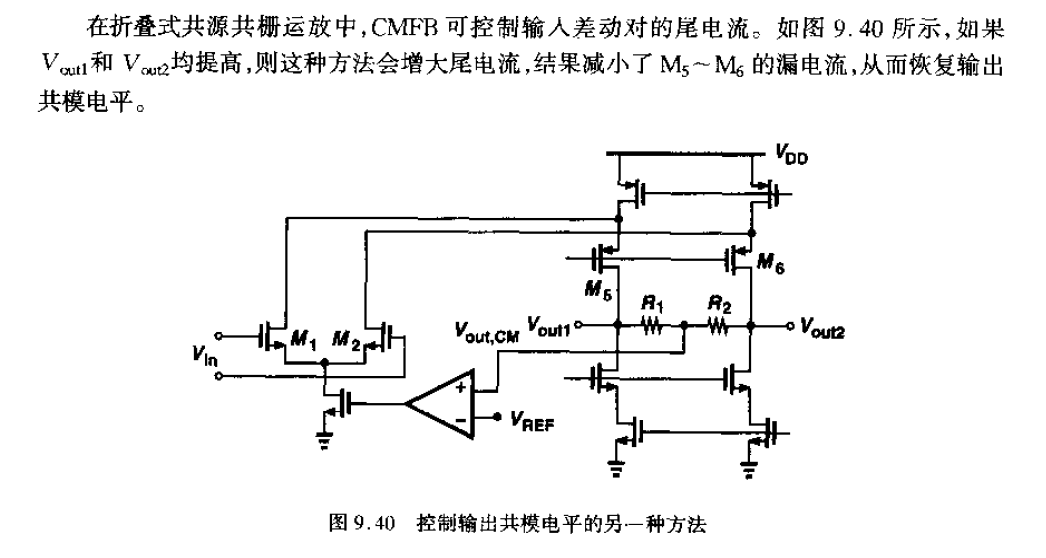

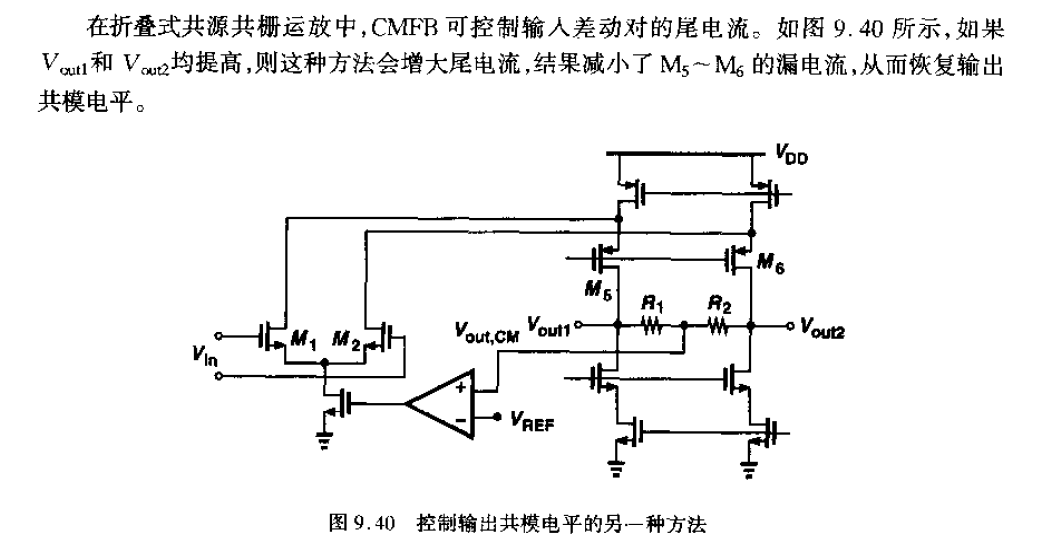

对于如下图2,所说的恢复共模电平又该怎么理解呢?

图2

大哥,图呢?怎么看不见

啊 不好意思 我重新发一张

图1

图2

我感觉这两个电路说的都是同一个原理吧。

第一个图,VB上升,M1和M2的尾电流将增加,和VDD较近电流源的电流更地分到了M1,M2支路,输出共源共栅支路电流减小,所以共模电压减小,使得M7,M8电流减小,VB控制的管子电流减小,可能会进入线性区,再反馈到输出支路这边,使输出共模电压上升。

第二个图,若Vout共模电压上升过高,使输入对管尾电流上升,从而输出支路电流减小,使得输出共模电压Vout有所下降。

这两个变化都是在一个动态过程。

折叠点处,根据基尔霍夫定律,当M1,M2电流增大时,另外两路总电流肯定是减少的。当所有管正常工作时,折叠点处上面的两管的电流本身因为其他两路电流之和(甚至大于这个值,一般为尾流的1.2~1.5倍)

所以,减小的应该是折叠点向下的电流。我是这么理解的。

我发现一个很有意思的推论,

1。针对上面的PMOS而言: M5 和 M6的漏电流减小,那么M5 M6管的Vsd将减小,那么Vout1 Vout2将增大;

2。 针对下面的NMOS而言:M5 和 M6的漏电流减小,那么NMOS两端的Vds减小,最总Vout1 Vout2将减小;

这两者怎么是矛盾的啊

照你这么一说,我仔细算了下,感觉确实存在你所指出的矛盾:共源共栅支路电流减小时,PMOS会将VOUT上拉,NMOS会把VOUT下拉。我感觉有没有可能是因为下面两个NMOS的下拉能力明显强于上面一个PMOS的上拉能力(通过计算是这样),而导致VOUT最终体现出下降的现象呢?

下面的NMOS是电流源,而M5 , M6的源端电压不是固定的,M5 M6的电流减少,M5的源极电压下降,漏极电压也同时下降

如果Vout1和Vout2都上升,那么NMOS输入对的尾电流增加,那么单个NMOS对的漏电流也增加,再进一步NMOS对的漏电压即M5 M6的源电压上升啊。

不明白到底该怎么解释?你要是继续往深的推,会发现更多的问题。因为NMOS对的尾电流增加,那么单个NMOS的漏电流增加,那么NMOS对的源端(假设为P点)Vp就会下降(根据Id=1/2*Un*Cox*(W/L)(Vin-VP-Vthn)2)

n管有自己的偏置电路吧 根据偏置电路形式不同 对电流有不同的依赖性 还有之路电流小,导致的输出电压应该低

下面那个共源共栅是一个定值,也就是输出电阻是恒定的.故V=IRoutnmos由于电流减小,故Vout1,Vout2减小

上面那个共源共栅是存在多个变量(>=2个)输出电阻是一个变量,做V=IRoutpmos不能确定.

note:这两个电路中,直流工作点不是固定的哦,这个是前提哦!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:正负电源模拟电路设计

下一篇:急问:VerilogAMS能仿S参数么?