folded cascode slew rate limit

录入:edatop.com 阅读:

麻烦高手指教一下,最近在仿真一个two stage运放的时候遇到一点问题。怎么去计算slew rate? 我用差分输入的偏置电流除以补偿电容的出来的结果和我用cadence仿真出来的结果差很多......这里要考虑miller effect吗?

怎么才能提高slew rate和频响的带宽?

怎么才能提高slew rate和频响的带宽?

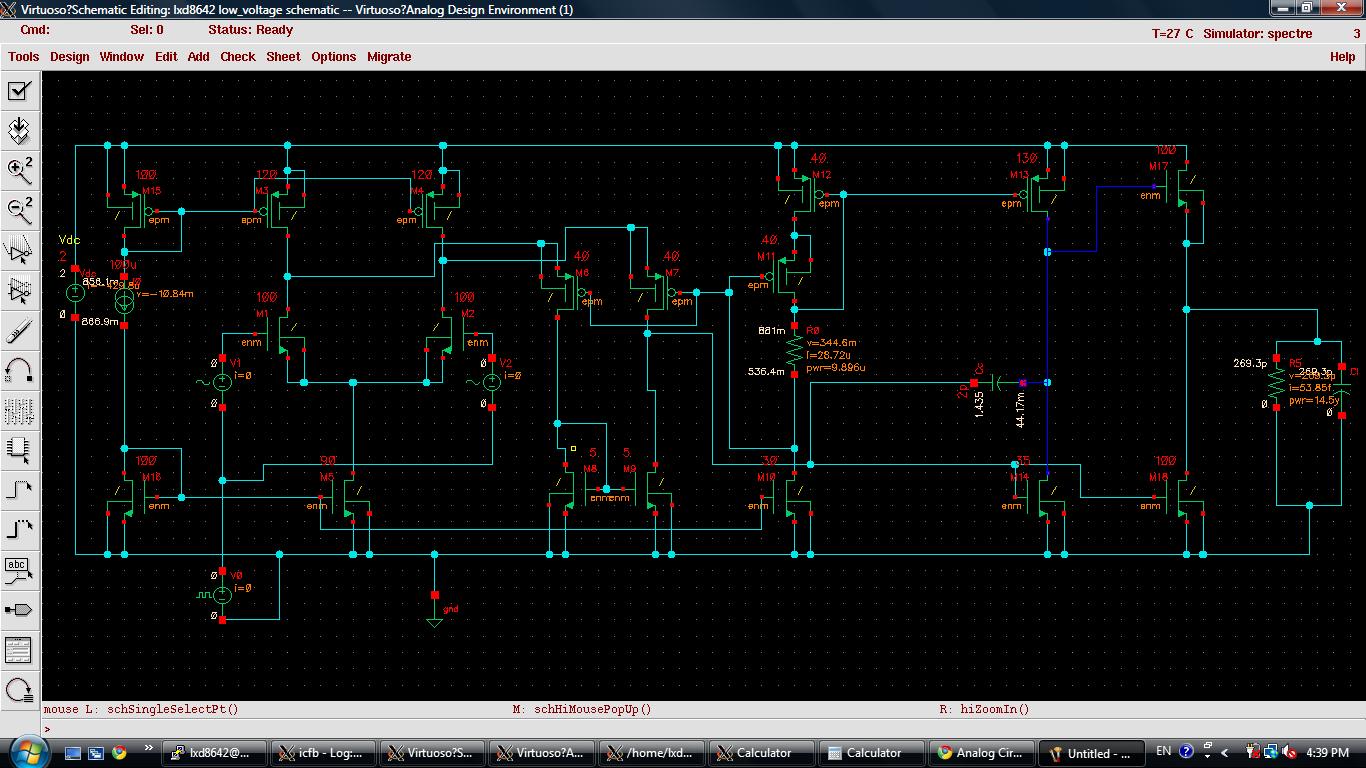

电路图

给的信息太少了,电容到地输出是多少?miller的又是多少?他们的电流是多少?你确定miller的那个slew小?slew 你怎么仿真的?

电路是看懂了你问的问题也懂 就是啥具体的SPEC也没提供!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。