pll 锁定后的ripple 分析请教

录入:edatop.com 阅读:

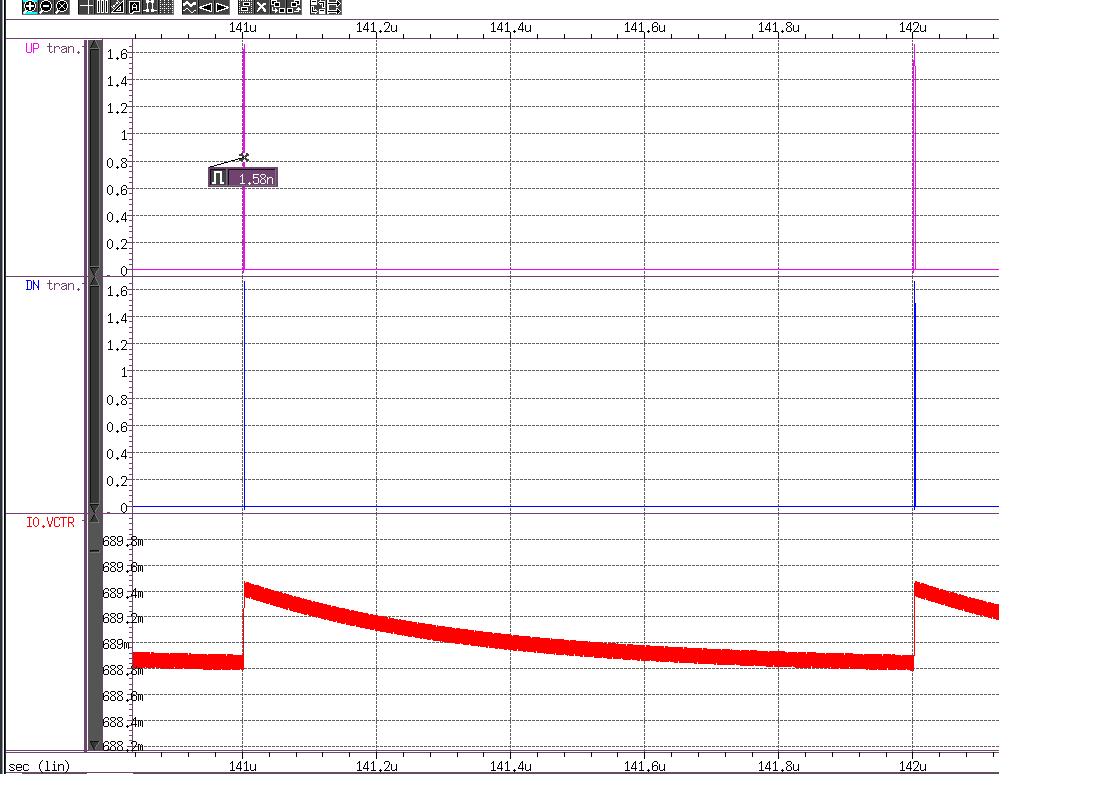

上图是一个PLL 锁定后的电压 ripple 比较大,

输入频率1Mhz, 输出300Mhz, 带宽 65K。

因为M很大,所以VCO的accumulation噪声比较大,所以ripple大一点也是说的通的。但是上图的ripple 表现出来时一直给Cap充电,我怀疑是不是有漏电啊?或者别的什么原因?

跟大牛们请教。

charge pump 的电流mismatch比较小 用的是cascade电流源。

Up Dn 的mismatch 为 1ns。 温度为125C

ripple 大约0.6mv,pk-pkjitter simulatin结果是85ps。

觉得没什么问题

呵呵,谢谢啦,

不过VCO控制信号上面的ripple不是random的,而是有规律的,有什么办法减小点么,

HAO!

0.6mv不是很大吧。

看上去怎么像charge sharing?

其实你的带宽很小了,Ripple应该比较小吧。其实Cascode 电流源

的DC很好,Transition应该比较麻烦,可能是开关的问题。还有你那

Jitter是什么Jitter饿,怎么Run出来的?

Jitter 是用wv算出来的, 后来想了想,觉得可能是R带来的噪声,我为了追求小的面积,把C减小了,R增大了。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。