关于PLL稳定性和jitter的问题

录入:edatop.com 阅读:

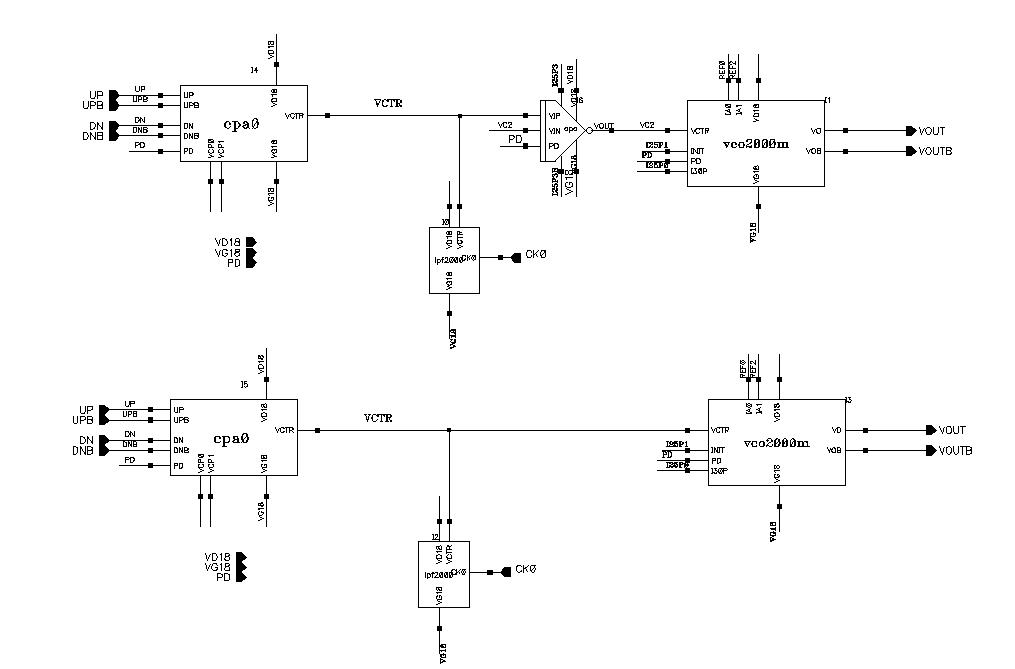

大家好,下图是我画的一个PLL的结构,开始没有加上buffer的时候Vcon上面的噪声比较大,大约0.6mv,仿真的jitters大约12ps,后来我想了想加上了buffer,结果晕死,Vcon上面的噪声是小了,只有0.08mv,但是jitters大道理140ps,结构如下图,谢谢啦

大家好,下图是我画的一个PLL的结构,开始没有加上buffer的时候Vcon上面的噪声比较大,大约0.6mv,仿真的jitters大约12ps,后来我想了想加上了buffer,结果晕死,Vcon上面的噪声是小了,只有0.08mv,但是jitters大道理140ps,结构如下图,谢谢啦以前采用的是下面的结构,后来改用上面的结构瘤

小编的上图不成功,方法不对,看不到啊

如图,,,,,

是不是buffer带来的噪声啊?

你用analogLib里面的理想vcvs设置gain=1当buffer试试看呢?

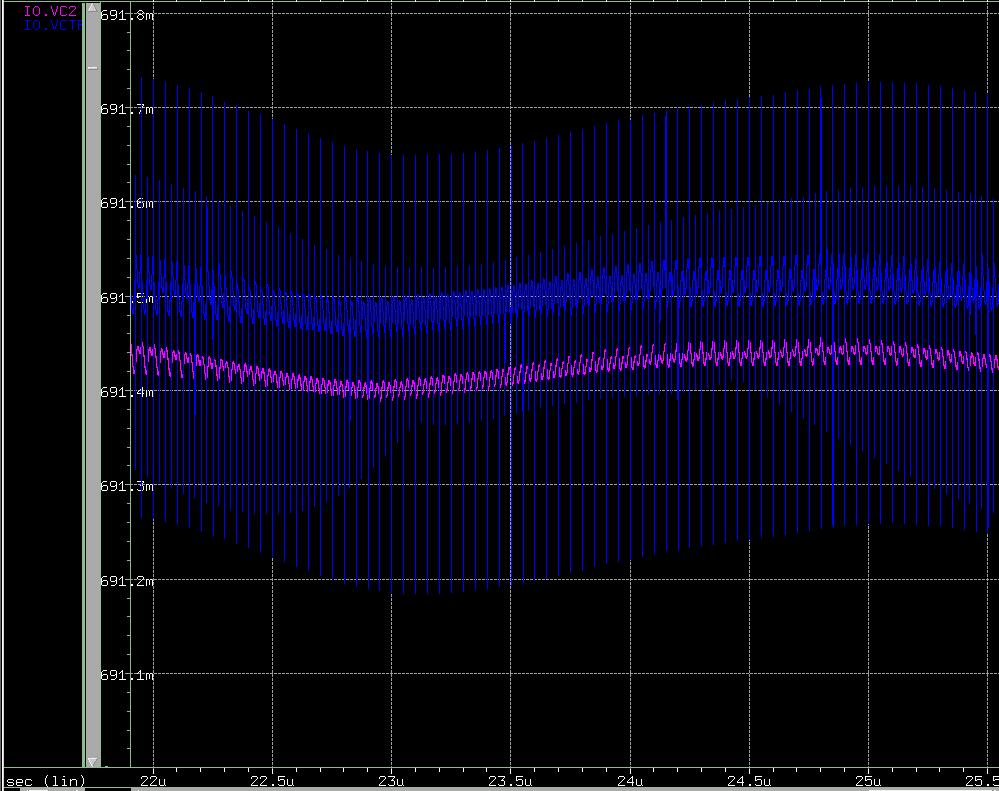

其实buffer以后的噪声小多了,VC2是buffer后的波形,VCTR是buffer前面的波形

buffer带来的噪声应该会表现在VCO的控制电压上的,仿真结果应该能看出来

你是怎么仿真jitter的?

如何加的noise?还是用PSS什么仿真的?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:how to simulate mismatch using spice or cadence?

下一篇:ic610里怎么选择使用APS仿真器呢