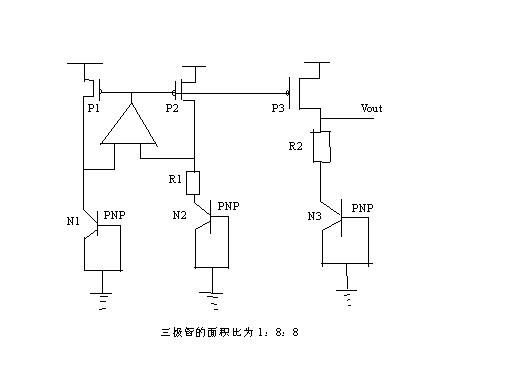

关于带隙基准设计中PSRR和电路启动问题

Vbg图!

pmos管可以采用级联形式,PSRR提高不少!就是不知道你的工艺在1。5V电源下还能正常工作?

还有一点,即使PMOS不采用两个串联的结构,一般也不止30dB啊,是不是你的PMOS的L太小了,把L相应调大,PSRR会好一些!

1、请说说 启动是怎么仿真出来的 ?

2、关于电源抑制比的方法有好几种。不知道你对电路参数有什么具体要求。

前面兄弟 提到的cascode结构对于低电压工作比较困难。采用preregulator会增大功耗和面积。最简单的方法就是 从数学公式上推到,引入和电源相关的反馈环路。

我对你第一个问题比较感兴趣,启动的仿真问题是否准确呢?

你那是否是看启动电路的启动瞬态响应?

提供一个思路:假设vdd变化一个小量,可以计算电流镜电流的变化,这个变化delta(i)*R2就等于输出变化

要提高psrr可以考虑换结构,比如三电阻+二级op的结构

板上高手真多

受教了!

请问“PSRR>60dB”是指多高的频率下的?比如100Hz或1kHz甚至1MHz?

还有一点采用1。5V电源,工艺是0。18um还是0。13um?

针对你的要求,采用运放构成反馈环路就可以满足PSRR>60db(应该是直流增益)的要求。

我所说的都是对于很高的PSRR要求。

有什么问题,我们可以qq留言联系。

我上网不方便。

怎么调好的,输出基准不在反馈环路里,psrr不会太好,直接是R和ro的分压。除非R很大才行吧。

很好!很强大!

你的电源电压是多少,op是什么样的?

先看看图再说

还是没懂

频率是100?

那是低频了吧

..............

学习学习

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。