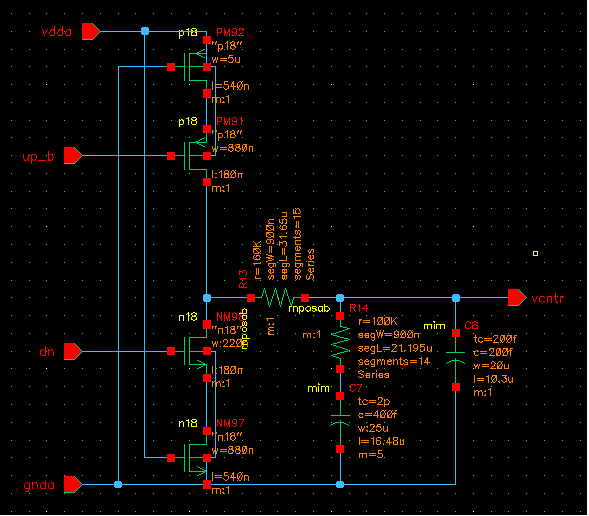

CPPLL的滤波器设计问题

首先你的思路很好,结构很新颖,这样的确可以锁定,任何电路都可以,只要是低通滤波器,并且带宽足够窄就可以锁定。

但是一般不推荐添加横向电阻,这个电阻横在那里会产生大的热噪声,对于VCO输入信号不利。

另外你的CP似乎结构很简洁,我没有用过,呵呵,不知道你是不是故意这样做的,这样的结构太有创意了。

锁定应该没有问题吧,添加电阻电容是为了增加PLL环路的相位裕度,关于电阻的热噪声真的那么严重吗?

至少应该和MOS 的热噪声差不多把!

不知道楼上的在那里看到的这个结论呢?

呵呵,你不用怀疑这个结论,这个结论是一个干了三十多年analog的外国人告诉我的。

当然这种结论我们早就应该想到,只是不敢想而已,这就是高手与菜鸟的差异吧。

正是因为这个原因,三阶滤波器在使用的时候会很慎重(因为三阶滤波器有一个串联电阻,不过是在滤波器的输出,这样其实更可怕),而且正是因为这个原因有源滤波器早已经退出了环路滤波器的历史舞台(很多low jitter pll都不用有源滤波器)。

我只是告诉你这个电阻的弊端,但是并没有说这样不可以。

你可以参考Dean和R.Best的书籍看一看,具体好像也只是简单的说了一句这种影响,好久以前看过的了。

模拟电路设计最重要的是tradeoff,而不是绝对的正确与错误。

所以根据指标进行设计,最终达到你的指标才是目的,而不是做到多么好的指标,这个太难了,而且做几十年的人都不能保证的,需要对于工艺很好了解,以及很多其它因素,比如layout的布局,电源分配等。

不要在lpf上耽误太多时间,CP和VCO才是设计的难点,呵呵。

一个好的锁相环很多因素都要考虑的,加油吧。

有什么问题多多交流啊!

谢谢ilikeeatingcake大侠的指教阿!

一直在作DCDC ADC之类的模拟,一年前才接手一个同事留下的CP PLL,还在PLL的入门阶段,看了几篇paper,对于CP VCO的还不是很了解,通过仿真好像也不能看出不同结构CP的性能指标的优劣,对PLL仅仅了解一些皮毛,还差很远阿!

就象你说的

“所以根据指标进行设计,最终达到你的指标才是目的,而不是做到多么好的指标,这个太难了,而且做几十年的人都不能保证的,需要对于工艺很好了解,以及很多其它因素,比如layout的布局,电源分配等。”

我们的PLL要求不高 100~200M,只是作frequency synthesizer。具体的测试结果p-p jitter 30ps。

再次感谢 你的回复,有机会还要向你请教阿!

不客气。

ps,100MHz~200MHz? synthesizer?p-p jitter 30ps?

这三个概念的关系好像有问题。

1、没有听说过100MHz~200MHz的synthesizer的可能性

2、p-p jitter 30ps 你不用设计了,肯定设计不出来的。

3、对于100MHz左右的频率为啥jitter30ps?干什么用?卫星用?

今年是鼠年,就不跟你咬文嚼字了,看来你有很多地方不明白,不过不要紧,加油吧!

嗯,赞,说的这么详细

小编对pll很熟悉啊,我才刚开始研究锁相环,看了许多论文都是从结构上的改进。在设计电荷泵电路时要考虑哪些因素,怎么仿真还是不清楚,能不能推荐一些CP设计的资料呢。我的邮箱hustyiqi@yahoo.com.cn

期待与你多交流下啊~

说的很明白

小编的结构很简单

看看拉扎维的书,基本的电荷泵锁相环的结构里面有讲。

最常用的CPPLL的LPF里面是没有前面那个电阻的。

环路带宽近似为Icp×Kvco×R/N,你要把环路带宽放到环路滤波器的零点与极点的中间才能保证环路具有较好的相位域度,否则环路有可能振荡。

你的电荷泵电流还是用电流源实现的好,已保证电流的准确度,如果要求性能较好还要用cascode结构。具体要考虑的问题参见拉扎维书的第15章。你这个电荷泵做的太简单了,并不实用。

设计整体电路之前你要先把CP,LPF,VCO的各项参数确定好,如CP的电流,LPF电容、电阻的大小,VCO的中心频率与Kvco。要考虑的问题很多,先看看拉扎维的书吧,理解一下里面讲的传递函数概念。

30p的jitter不知道你指的是c-c jitter 还是phase jitter。c-cjitter容易做到,phase jitter 是不可能做到的。对于不同的系统,所关注的jitter 是不一样的。

阿卡大家看到的空姐没法

学到了很多东西啊,我还有一个很弱的问题:CPPLL与一般的PLL相比有什么优点?

受益非浅

讨论不错...

小编的p-p jitter应该是period-period jitter吧?对于100M-200MHz的输出,30ps p-p jitter其实不需要怎么关注了。

我能想到你用的是Ring VCO,只要环路不做的太差,没什么问题。

可参看National semiconductor的An Analysis andPerformance Evaluationof a Passive FilterDesign Technique forCharge PumpPhase-Locked Loops,有详尽的环路设计介绍。

说的这么详细

各位大侠,请问CPLL带宽一般怎么设计?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:DC仿真的问题!

下一篇:两个VerilogA模块之间连接的错误