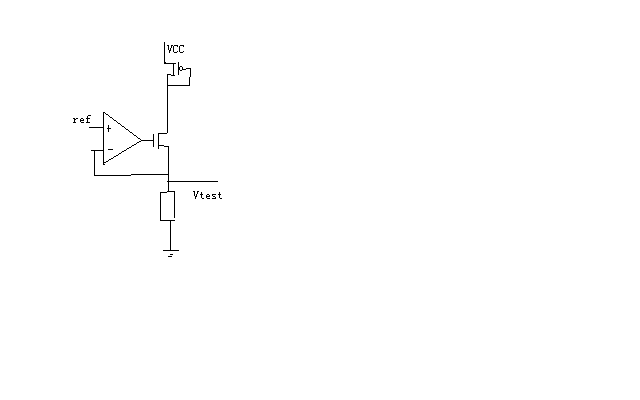

LDO测试

顶起来,学习下

确认 Vref随温度不变?

上面的PMOS为什么用Diode接法,防范ESD完全可以把栅接地啊,上面的PMOS电压随温度变化如何,有没有可能让下面的NMOS进入线性区?

ref是恒定的,电阻上的电压就是ref电压,那电流怎么会变化的?

PMOS接法是为了给其他电路提供镜像电流,基准电压我没有测到。

但是根据测试当电阻较大时,Vtest的电压随温度变化不大,但是当电阻较小时时,Vtest随温度下降了100mV左右,

如果确定基准没有问题,则两者的区别就是电流的大小不同,怀疑是电压裕度不够,建议察看或仿真在高温大电流下不同corner需要的最低电源电压

个人觉得那个应该是两个电阻接成负反馈的的,比值就可以了。

精彩!加油的!加油!

学习楼住的这的种精神TMD~太牛

传统的营销手段-效率低逐渐被淘汰 以速度慢,

想我们的go Good敬爱的非常厉害战士们敬礼!

上海搬场-有口皆碑的上海企事业单位

wet etching-wet etching help you to power

注册香港公司-注册香港公司优势主要有选择企业名称自由

massage guangzhou-service for massage in guangzhou

气动阀-气动阀权威行业厂家

个人觉得是N管驱动能力有限,这个电路实际上就是一个带缓冲的运算放大器(驱动小电阻负载)用作跟随,当电流达到一定程度后,图中负载大到一定程度(电阻很小)时,就可能跟随不上,一方面选择高增益的运放,另一方面增大N管和P管的宽长比应该就可以了

支持楼上的观点!

可以先做个直流扫描,把电阻换成电流源,扫描输出电流,测量输出电压,看看驱动能力

是仿真呢还是测试,小编设计LDO的经验可不可以分享一下

测量LDO的vbg从某种程度是要考虑测量短对整个电路可能会造成的影响,如果测量表的输入内阻不够高,可能会增加vbg的驱动负载,引起vbg电路特性的变化,另一方面,测量表存在容性,可能会引起vbg输出端极点的偏移,从而可能会发生震荡,因此添加一个buffer一方面是为了增加驱动能力,另一方面是提供较高的输入阻抗。尽管如此,如果buffer的驱动能力设计有问题或者op的输入阻抗不够高,依然会引起问题,因此在这里建议选择更高的输入阻抗的buffer和增大后面驱动管的W/L,此外在后面的驱动管那里存在一个极点,原则来讲这样的电路如果稳定工作需要一定的补偿,在你的表笔那里并上一个电容,或者做米勒补偿比较好,你最好用示波器实时的检测电路是否已经发生了震荡。

可能是6mA时运放进入线型工作区了

有道理

re

First, u should make sure system is stable.

Second, u can caculate the max current Imax which it could drive:

Vmax: the max op output

Imax = 1/2 * K * W/L ( Vmax - Vref - Vth ) ( Vmax - Vref - Vth )

Or u can scan and get Imax

同问,,希望是芯片测试,,,,

你LDO的反馈网络接的不对吧 没有电阻分压?

这个LDO电阻反馈接法有问题吧

ref是恒定的,电阻上的电压就是ref电压,那电流怎么会变化的?

改變電阻~

NMOS的驱动能力不够!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:向高人求教下发展道路问题

下一篇:请问模拟设计与射频设计有什么区别