流片出来栅极击穿了!

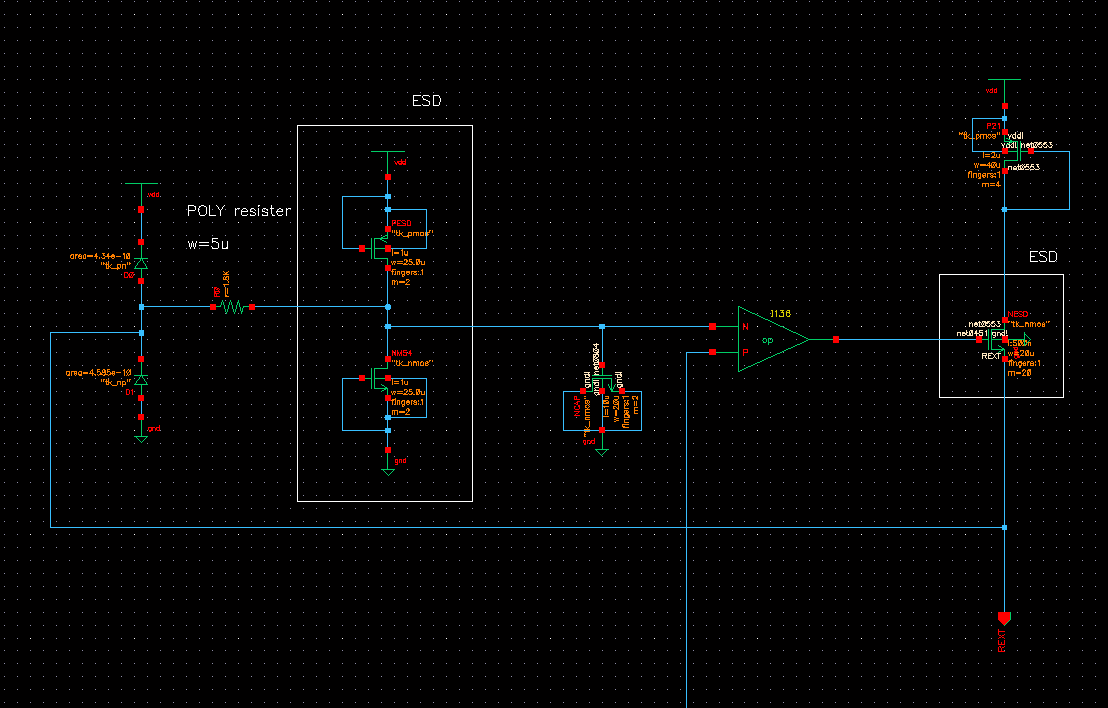

击穿的电路是一个调节外接电阻的电流源。运放的栅极输入a接到芯片外,电路上没有做esd二级保护电路,但是这个栅极同时也有接到其他的管子的漏极,测试的时候发现芯片的成品率基本上只有一半,坏掉的芯片测试的时候pad端电压已经没有跟随内部的那个固定的电压了,估计是a端的栅极被击穿。不知自己的猜测是否正确,或者是有别的原因?有没有高手帮忙告诉下,感激不尽!这个问题再次流片的时候要怎么解决呀?谢谢了!

运放的栅极输入a 到 PAD之间有没有电阻啊?

很可能是栅极击穿了,建议在a与pad间加一个几k的电阻,最重要的pad的esd要设计好

测试:

1,无电源时,测量PAD到地的电阻。如果是短路,就很可能是a的GATE oxide击穿了。

2,有电源时,用scope观察PAD的波形。如果看到震荡波形,说明反馈环路不稳定。

建议:

1,如果a是连GATE ox,通常的ESD在PAD并不能保护内部GATE,需要2-5K电阻加上secondary ESD (Gate grounded NMOS with 10-40u/Lmin)或者diode到低压supply。

2,为什么运放的输出是PMOS?PMOS有两个问题:增益太高而且可能有两个主极点(一个在运放里,一个在PAD);head room可能有问题(两个PMOS)。运放输出用NMOS,而且运放只要是一级的OTA,让输出为主极点。

测试:

1,无电源时,测量PAD到地的电阻。如果是短路,就很可能是a的GATE oxide击穿了。

2,有电源时,用scope观察PAD的波形。如果看到震荡波形,说明反馈环路不稳定。

建议:

1,如果a是连GATE ox,通常的ESD在PAD并不能保护内部GATE,需要2-5K电阻加上secondary ESD (Gate grounded NMOS with 10-40u/Lmin)或者diode到低压supply。

2,为什么运放的输出是PMOS?PMOS有两个问题:增益太高而且可能有两个主极点(一个在运放里,一个在PAD);head room可能有问题(两个PMOS)。运放输出用NMOS,而且运放只要是一级的OTA,让输出为主极点

good article!

that's very funny!

谢谢。

1.有裸片测试,pad到地的电阻差不多只有十几k吧

2。没有震荡波形的存在,运放有外接补偿电容。

3。2-5k的电阻需要这么大吗?200欧姆的够不够?

够了,不过大点有坏处吗?

8# 纯白雾隐

200的话,20um/Lmin的NMOS 作secondary ESD可能不够大;也就是说你要200um/Lmin。不过这样的话,面积要大些。

不一定是栅极击穿。

1、测量对地电阻有十几K,说明对地有过大漏电流。如果运放输入端是PMOS,那肯定不会是栅极打坏了。应该是PAD上的ESD保护电路出了问题;

2、如果运放的输入端是NMOS,那么运放的输入级MOSFET的源和漏都不会接地。所以除非栅极一直被打穿到衬底了,否则不会对地有大漏电流。如果真是这样那么a端的NMOS应该等效于开路(源漏间将不会有电流)。所以试着去掉a端的NMOS做分析,看看PAD上的电压和测出来的是否相符。

其实如果NMOS的源漏端都不接地,那么栅极的打坏不是非常容易的,因为沟道N和衬底P之间会形成比较厚的耗尽层,会吸收掉不少ESD电压。剩下加在栅极氧化层上的电压就不一定很大了。

如果栅极没坏,那么就是ESD保护电路的问题。

没有人发表点其他的意见么?

这些结论有依据吗?还是你自己想的?

贴个电路图,连基本的ESD也没做好,一般都不会把gate直接连PAD

栅极没有那么容易击穿,呵呵.

你们的片子出厂以后做过测试么?如果没有 就更加不可能了。一半的被击穿,那还的了啊

貌似你这个东西只是整个片子的一部分,原因可能很复杂,不好说

汗一下楼上的这位!

"但是这个栅极同时也有接到其他的管子的漏极" ,说明PAD是直接连到某个管子的漏端的。不是大管子的话要按照ESD的管子规则设计。不然PAD上的ESD会没用的。

hi, this risk must pay more attention to.

A:you should add esd protection between the Gate of AMP and PAD.

没有专门去试过。只是根据一点经验和半导体知识推论的。

貌似不是ESD打坏的

ESD 打坏的几率没有真么高的

14# guang3000 Hi, guang3000. Could you pls explain your concern about the ESD protection of this V2I circuit. It seems strange to me. For this kind of circuit, we usually put a ESD near the pad, and put a ESD res near the gate and source.

谢谢各位了,流片结果可能会在7月底出来,到时候看被击穿情况了

不知道呢,别人芯片里面的电路。

pad到a之间加一个1~10K的电阻,然后在a上加一个5V的mini ESD。长个教训,以后pad不能直接接到栅极。

用作ESD保护的电阻好像一般50,100欧的样子就可以了,楼上说要用上K的电阻是否过大

反正运放输入阻抗高, 多点ESD 隔离电阻也是不错的

yes, 太大。

通常PAD接栅极的中间都会有一个限流电阻

大点有坏处

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。