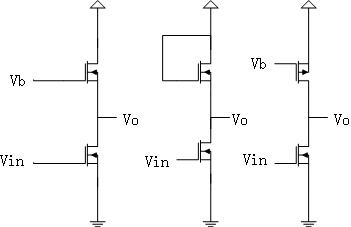

共源管接不同负载的三个电路的区别

上图是三个类似的电路,输入管均是NMOS管,第一个负载是NMOS,第二个是二极管连接的NMOS,第三个是PMOS,Vb是栅极偏压,若Vin都为0时,第一个Vo=Vb-VTHN,第二个Vo=Vdd-VTHN,第三个Vo=Vdd,请问这个如何解释?谢谢!

这是共源共栅电路吗?

这个是共源共栅么?

不是。

If Vin=0, the lower NMOS is off,

first one, Vo=Vb

2nd one, Vo=Vdd

3rd one, Vo =Vdd

这个的确不是共源共栅,发贴的时候估计NC了下,现改回来了

ls的能说说理由么

VIN和VB偏向于器件的那一端就是S段么

首先这个电路图中,VIN不该只有交流信号,还包括直流分量。这个直流分量决定了输出点VO的静态工作点。

从静态工作点来看,第1图为VB-VTH,2图为VDD-VTH,3图由NMOS和PMOS的沟道调制效应共同决定,介于0和VDD之间的任意值。

从电压增益来看。第1、2图相等,负载同为从源端看进去的电阻为1/GM。第3图最大,负载为电流源的输出阻抗R0。

这3种电路结构在普通的运放中都可以见到,1、2图的组合就是一个差分输入级的交流小信号通路。3图多作为驱动容性负载的输出级。

前面两个我能看明白,最后一个V0=VDD没有看明白,高手指教。

虽然你的英语很好,但只有3rd one是正确的

If the lower NMOs is off and there is no output current at the Vo, there is no drain current at the upper transistor.

First one: if there is no drain currrent, the Vgs =0V, therefore, the Vo = Vb-Vgs = Vb if Vgs=0V.

Similiar for the second one. Now, the Vb=VDD.

Third one: the upper transistor is pulled up resistor. Vo=VDD.

The result will be same as the first post by shadow_cuk if there is a drain current at the upper transistor => there is output current at Vo or the lower transistor is conducting (Vin>Vth).

第一个:Vb一般会小于Vdd,那么在输入管截止的情况下,上面的N管工作在饱和区,电源会充电,充电电流可以用饱和公式算直到电流为零时就是Vo的电压 所以会有Vgs-Vthn=0也就是Vb-Vo-Vthn=0则Vo=Vb-Vthn.

第二个:跟第一个一样,只是把Vb换成Vdd。

第三个:上面的p管先工作在饱和区充电,再工作在线性区,直到充电电流为零,那么电流为零的计算公式就是线性区的计算公式,按照第一个的计算方法就可以得到Vo=Vdd.

For the first case:

Reminder that the ID=1/2uCoxW/L(Vgs-Vt)2 is the equation for transistor in saturation region.

At low drain current, the transistor is in the sub-threshold region, another equation take over.

Depending on the leakage current, the top transistor are in off region or near off region or goining into sub-threshold, that means, the Vgs << Vth.

Therefore, the Vo is near Vb as Vgs is small (less than 1/2 Vth) .

For quick analysis, the top transistor is in OFF state, Vgs =0V, therefore Vo=Vb.

小编明显是把这些当数字管来考虑的,得到后面的结论也就不奇怪了

1# shadow_cuk

8# grusher

谢谢grusher跟ls各位的回帖,12楼所说的电源充电是不是指输出点对地有寄生电容的存在导致电源对电容的充电? 我老板说过如果上下两管都是高阻态的话输出即为不可目测,图3的话上面的管子导通,下面的管子高阻,输出为啥不确定呢

分析的前提是只考虑饱和区工作的情况。

MOS栅电压能够决定的是漏源电流Idso=1/2*u*Cox*W/L*(Vgs-Vth)^2。在漏端接有负载RL的情况下,Vds=Ids*RL,此时Vds就被定住了。如果漏端悬空,需要考虑MOS管的输出电阻Ro,也就是刚才所说的沟道调制效应。3图的Ro应为PMOS和NMOS的输出电阻并联。因为沟道调制效应作为Idso的弱函数,这也就是输出电压为任意值的原因,任意值的意思是说实际、仿真、手算之间可能出现比较大的误差。

还一种解释是,Ids=Idso*(1+a*Vds),Vds需要在0和VDD之间谐调以使得ids(p)=ids(n)。

可是输入管并非导通,其电阻不受沟长调制的影响,图三是个电流源负载的反相器,输入为0时输出确定为Vdd,具体可以参见ALLEN的书上图5.1-5,我好奇的是图1跟图3只是电流源负载由NMOS换成PMOS,为啥后者输出能达到Vdd,而前者只能达到Vb-VTHN,采用哪种管子对大信号摆幅方面有何影响.

不过grusher扎实的理论功底还是蛮让我佩服的,你是学生么还是已经上班了

13# yeoks99

由于输入为0,输入管完全关闭,我认为应当不存在亚阈值电流的情况,输出端之所以存在电位我认为是电源通过负载管向输出管与地之间的寄生电容充电所导致的

其实就是单管传输门传输高电平和低电平时的问题嘛!

看来你不服气,我得给你上上课,当lower NMOS 的vgs=0,id并不是=0,而是有一个极少的漏电流,pA级,使图1的upper transistor工作在亚阀值区,它的vgs大于0而少于vth,所以V0稍微大于Vb-vth,但不会等于Vb甚至超过Vb,同理图2也是如此。

你这次总算说靠谱了,是接近Vb,但差值少于vth

我谈下个人观点,首先这三个电路都可以从电流连续性出发得出上面结论,当然这里不考虑亚阈值导通的情况,由于下面NMOS截止,所以上面MOS应该没有电流,MOS管没有电流有两个条件:一,没有形成强反型层,只有耗尽层,没有导通沟道,即VGS<VTH或者VGS=VTH,即临界开启,1和2图结论即是根据临界导通条件得来的。二,有导通沟道即VGS>VTH,但是VDS=0,3图即是根据VDS=0得来的。个人愚见,希望高手指点哈!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:问一个非常郑重的问题

下一篇:高压工艺里的低压管4端都接高电位没有什么问题吧?