smic18仿真中电阻总是通不过LVS是怎么回事

录入:edatop.com 阅读:

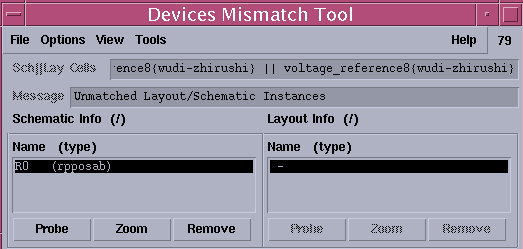

如题,DRC能通过,LVS时电阻和与电阻相连的net通不过,有谁遇见过这种问题吗?谢谢指教

could you let us see the circuit diagram?

你看看LVS rule,他的property是什么R or WL,还有就是你的netlist中应该加入一个电阻的subckt

貌似ext时就没提出res

可能是rule的问题,用smic的calibre——rule是没有问题的

谢谢,请问netlist中如何加入一个电阻的subckt,subckt是指什么?

很难说是layout的问题还是Calibre Rule提取的问题,都有可能。

1)提取的报告值得看一下。

2)看一下工艺文件,对照一下版图,看看这个电阻是否需要特别的层来定义

3)看一下LVS Rule里面关于这个器件的的提取

4)看一下版图提取的网表内容,在这个应该有电阻的地方,它提取成啥样了

我不建议手动修改提取的网表,会出大问题的!还是搞懂稳妥些。

因为有的提取出来的不是一个电阻,而是一个subckt,所以你单纯用电阻的netlist是通不过LVS的,可以写一个

.subckt XXX plus minus

R1 plus minus resistor

......

如果上面的方法可行的话,就是这个LVS的器件提取规则太差了。或者你的版图用了规则本身不打算支持的器件,所以提取不出来。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:拉扎维9.3式是如何得出的?

下一篇:求助,全差分运放启动问题