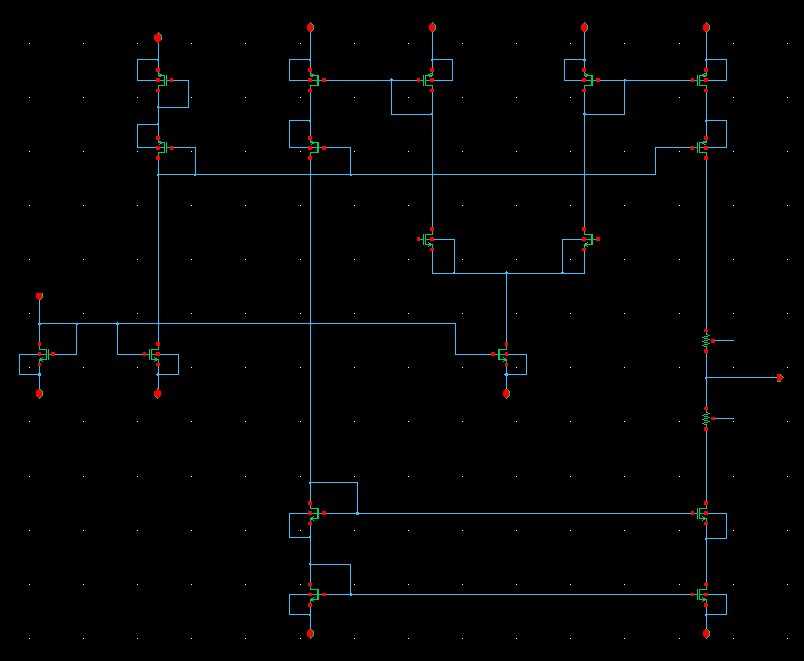

这个运放的差动输入对管到了亚阀值区域了吗? 内附详图

吗?有没潜在的危险?还有,这个是什么类型的运放啊?谢谢大家!

什么工艺?有独立的p-well?有Deep Nwell?衬底怎么这么接的?

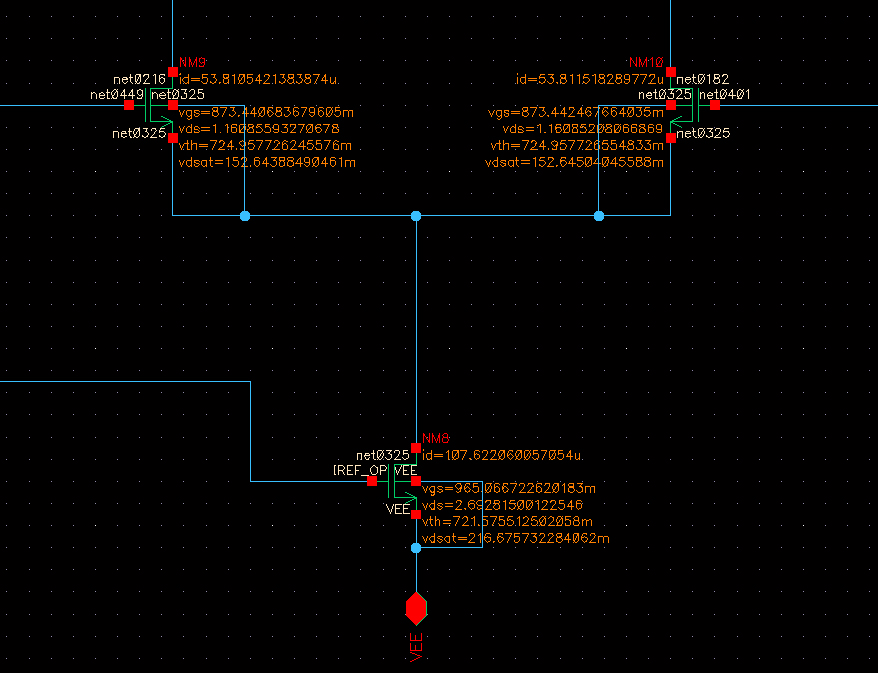

你看一下region=?就好了,3就是sub-threshold..

UMC 0.5um CMOS 工艺 , 有独立的p-well 也有 deep nwell

vgs只比vth大一点点,不太好,有潜在的危险.

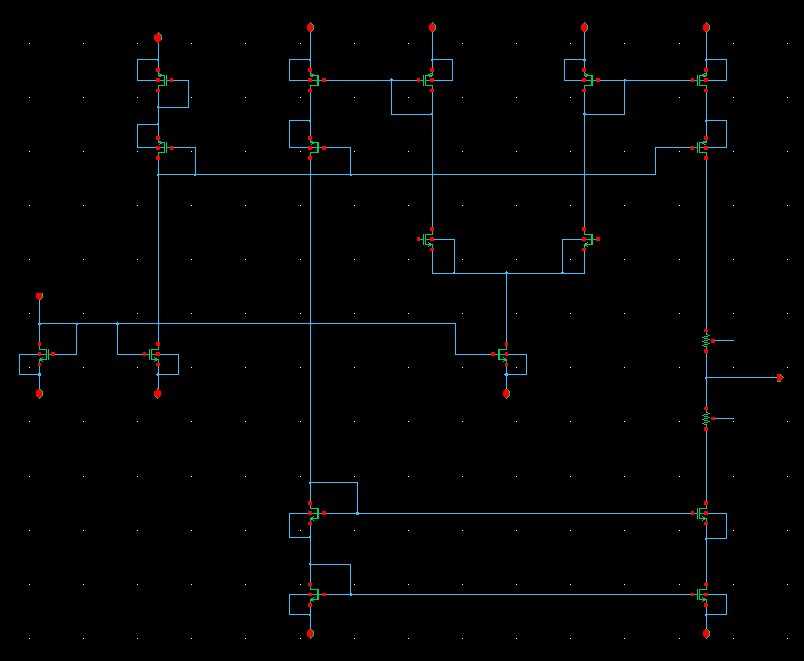

这个结构不就是一个折叠运放么

想请教下,潜在的危险,具体指的是什么呢?

Vov太小 肯定是工作在饱和区

管子太大了,所以需要的驱动电压很小

有可能会进入弱反型区

而且寄生电容比较大

非常不make sense,80uA电流需要w/L=160,浪费啊,而且没有一点好处

这样design有什么特殊考虑么难道?需要大的输入范围?大的gm?

transistor处于sub-threshold区域会使电路变慢,看看folded 点的寄生,不得了啊,而且input gm没增加多少

而且offset电流也会变大,反正是不合理

就是要大的gm,本来这个是bi-cmos工艺,npn管做输入对管的,gain很高,现在要用cmos来代替,并要达到同样的gain和bandwidth。

寄生电容不是问题,运放的输入会外接一个0.1uf的电容,这个环路的主极点在0.05Hz,而且运放的一端输入电压是固定的,没有高频下

共模抑制比的要求。现在gain和bandwidth都做到了,就是输入管子的过驱动电压好像小了些

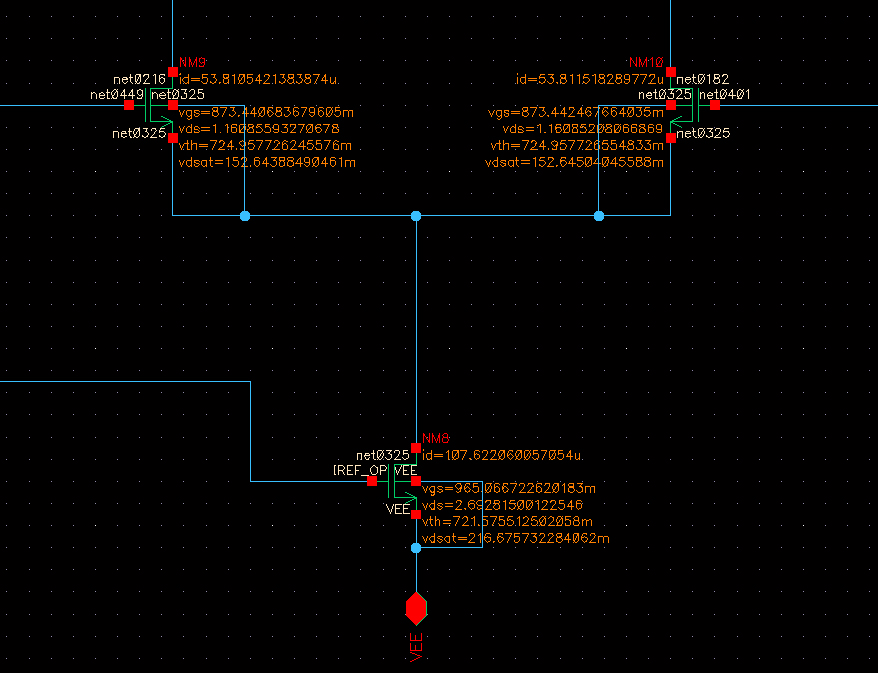

根据大家的意见,将输入对管减少了一半,W/L= 20u/2u * 4* 2 = 80 , 偏置电流108uA , 这样输入管的过驱动电压大了很多,gain 由109dB 变为 107dB , bandwidth由 21.9kHz变为 17.6kHz

.op一下不就可以看到管子的工作状态了嘛,有什么好问的。

transistor is working in weak/moderate inversion. The gm/Id is maximized. Of course, for the same current, the transistor size has to be larger, so the parasitic capacitance.

It is often observed in the low power design. BTW, differential pair working in weak inversion will also minimize input referred noise and offset.

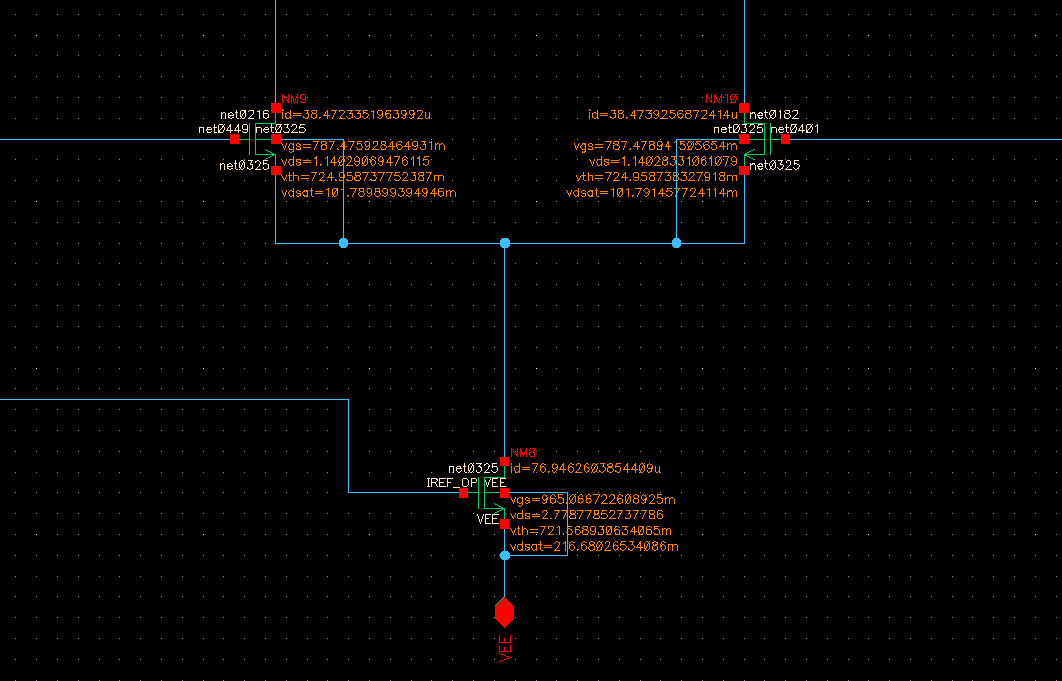

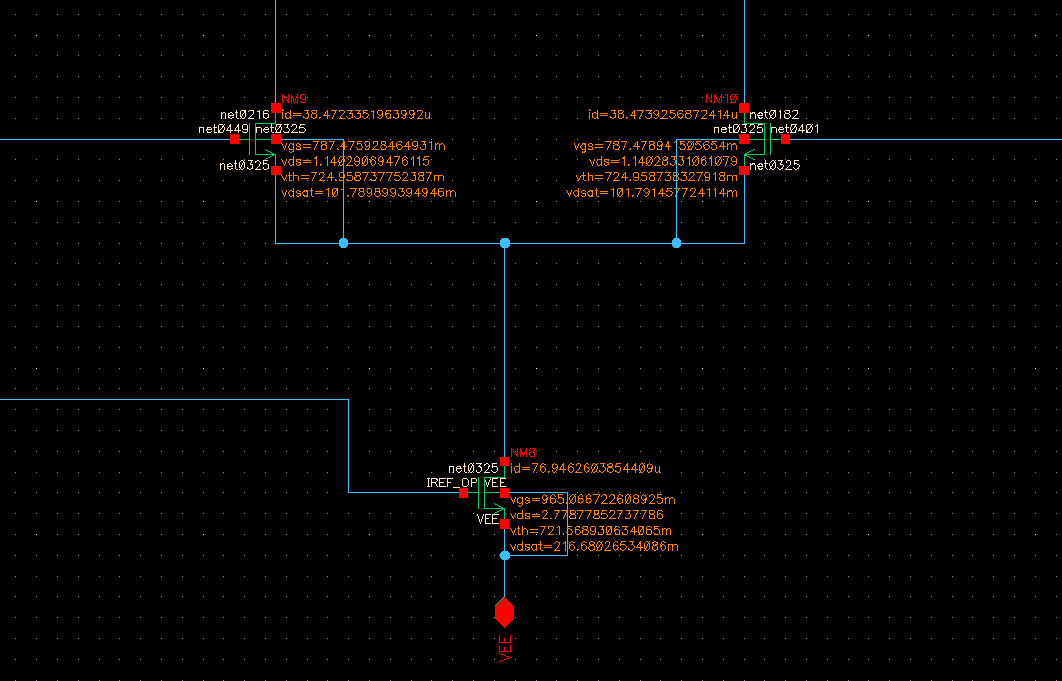

运放的偏置电流是77u, 输入对管总 W/L= 20u/2u * 8 * 2 = 160 , 直流工作点如图所示,这个运放的差动输入对管到了亚阀值区域了

吗?有没潜在的危险?还有,这个是什么类型的运放啊?谢谢大家!

什么工艺?有独立的p-well?有Deep Nwell?衬底怎么这么接的?

你看一下region=?就好了,3就是sub-threshold..

UMC 0.5um CMOS 工艺 , 有独立的p-well 也有 deep nwell

vgs只比vth大一点点,不太好,有潜在的危险.

这个结构不就是一个折叠运放么

想请教下,潜在的危险,具体指的是什么呢?

Vov太小 肯定是工作在饱和区

管子太大了,所以需要的驱动电压很小

有可能会进入弱反型区

而且寄生电容比较大

非常不make sense,80uA电流需要w/L=160,浪费啊,而且没有一点好处

这样design有什么特殊考虑么难道?需要大的输入范围?大的gm?

transistor处于sub-threshold区域会使电路变慢,看看folded 点的寄生,不得了啊,而且input gm没增加多少

而且offset电流也会变大,反正是不合理

就是要大的gm,本来这个是bi-cmos工艺,npn管做输入对管的,gain很高,现在要用cmos来代替,并要达到同样的gain和bandwidth。

寄生电容不是问题,运放的输入会外接一个0.1uf的电容,这个环路的主极点在0.05Hz,而且运放的一端输入电压是固定的,没有高频下

共模抑制比的要求。现在gain和bandwidth都做到了,就是输入管子的过驱动电压好像小了些

根据大家的意见,将输入对管减少了一半,W/L= 20u/2u * 4* 2 = 80 , 偏置电流108uA , 这样输入管的过驱动电压大了很多,gain 由109dB 变为 107dB , bandwidth由 21.9kHz变为 17.6kHz

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:关于输出放大器的问题

下一篇:HSPICE的各个版本有什么差别吗