bootstrap 电路设计问题

录入:edatop.com 阅读:

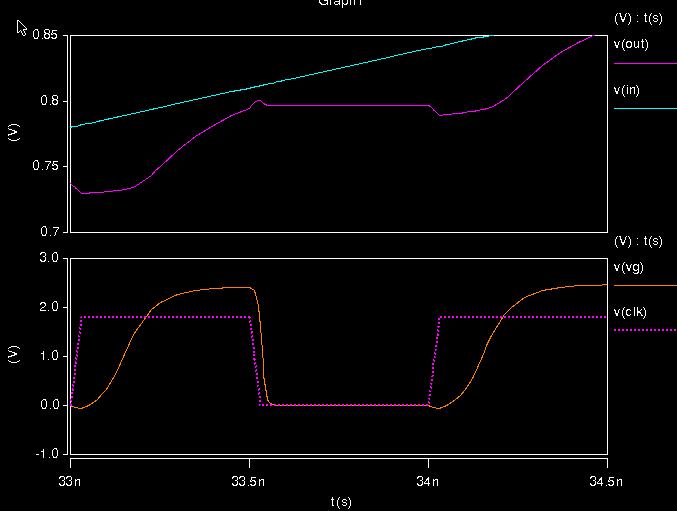

为了设计一个 1G 采样率的折叠差值ADC,先设计了一个 bootstrap 开关用在 T/H 电路里。发现开关电容负载太大了,导致产生的栅电压 Vg 形变很严重。bootstrap 用的是 Abo 论文里的形式。哪位大哥给点帮助吧。

电容取得大一点,还有大开关要做buffer 驱动。

bootstrap 里面如何加 buffer 驱动啊……

就是那些不是bootstrap的电压,管子大用inv chain驱动。

开关的大小是多少啊? 几十u么? 用的什么工艺? 最好说具体一点

看了你的waveform好像怪怪的,bootstrap应该没有这么慢的

SMIC .18um 工艺, 管子不大啊,10u/0.18u 的,5fF 左右吧

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:全差分运放怎么实现单端输出

下一篇:SC-CMFB 共模反馈