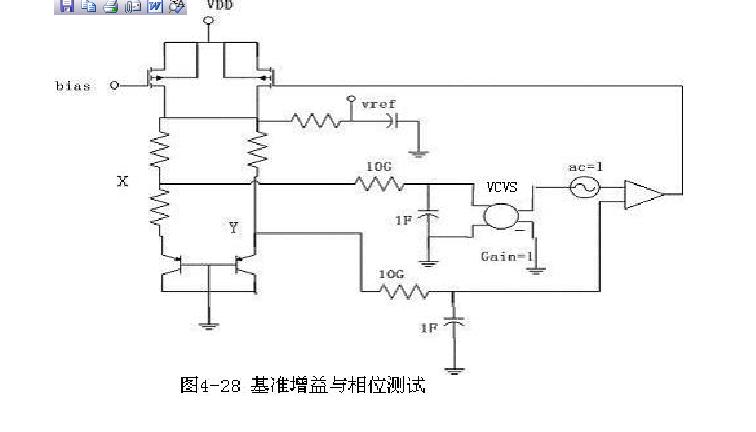

基准相位裕度仿真

vcvs是电压控制电压源

voltage control voltage source

电压放大器就是一种vcvs

这个图是那个书上面的? 有电子版吗

在capture或HSPICE中怎么实现啊?

裕度是什么阿,能解释一下么

有正反馈和负反馈环路,觉得这样只包括了负反馈,请高手解答一下这么仿可不可以呢

vcvs电路用上面代替啊?在capture or spice

The output voltage across nodes 4,3=1*V(2,1). The voltage gain parameter 1 is also given. The max and min parameters specify a maximum E1 voltage of 5v and a minimum E1 voltage output of 0v.

E1 4 3 2 1 max=5 min=0 1

单位增益vcvs。

小编这个图有点问题 单位增益的vcvs是用来做减法器(负反馈减掉正反馈)得到环路增益的。

没看明白你的意思?

公式是hspice中vcvs的描述方式

在这个电路中用单位增益的vcvs是为了得到环路增益(负反馈减去正反馈)

但电路图接法好像有点问题

好像是有问题

那该怎么样去仿相位裕度呢?指点一下 最好有个图或资料啥的

相位裕度是衡量系统稳定度的一个重要指标。它是指频率的回路增益等

0dB(单位增益,Unity Gain)时,反馈信号总的相位偏移与-180°的差。

相位裕度可以看作是系统进入不稳定状态之前可以增加的相位变化,相位

裕度越大,系统更加稳定,但同时时间响应速度减慢了,因此必须要有一个比较

合适的相位裕度。经研究发现,相位裕度至少要45 ,最好是60。

学西一下,小编为什么要仿真基准的的相位裕度,这种结构的基准又很多极点吗,我感觉不存在振荡的问题啊?

dingding

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:Cadence LVS and DRC设置求助

下一篇:请教关于spectreverilog仿真的问题,请求大侠知道