片上天线阻抗近似模拟

录入:edatop.com 阅读:

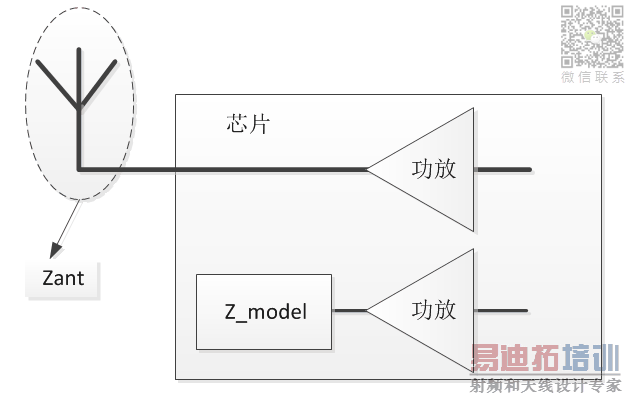

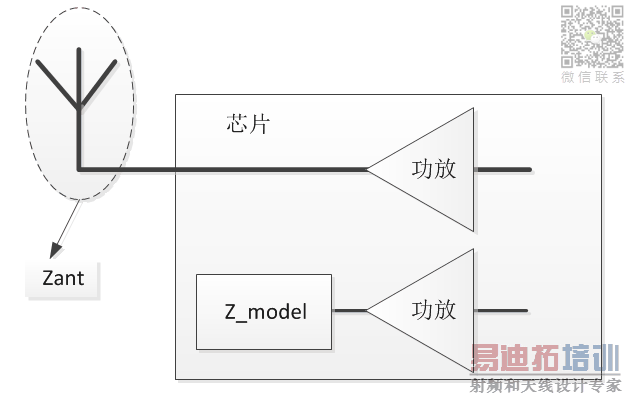

各位专家好,由于特殊需要,我期望在芯片内部能够建立一个可调阻抗网络,如图所示,希望它的阻抗Z_model能够与天线的阻抗Zant非常接近。请问我应该如何建立这个芯片内的阻抗模型。

天线是我可以自己设计的,是50欧的匹配天线(当然阻抗不可能是标准50欧,实际的阻抗形式是:R+jX),但是我不清楚,R和X的实际设计偏差能达到多少,还请各位先知能帮我给出一个估计范围?只有这个确定了,我才能确定片内阻抗网络的调整范围。

还有个问题是,假定我可以设计天线阻抗的虚部为容性,也就是为:R+1/(jwC)的形式,是不是我芯片内部的阻抗网络就可以采用电阻串联电容的形式实现(这样也就是R+1/(jwC)的最直观实现方式)。

在这里,我期望天线阻抗的虚部为容性的考虑是,如果阻抗的虚部为感性的话,芯片内部的阻抗网络是不是就应该采用电阻串联电感的形式实现。而电感在芯片内部是不容易实现的,特别是可调电感。不知道我这样的考虑是否正确。

PS:芯片内部阻抗网络模拟天线阻抗是可以实现,这个有很多论文支持,所以大家可以忽略对这个阻抗网络存在性的质疑。

但文献也没有给出天线的阻抗模型,只是给出了阻抗网络的实现,所以我不清楚应该如何依据天线设计阻抗网络。

希望各位大神帮我答疑解惑!

天线是我可以自己设计的,是50欧的匹配天线(当然阻抗不可能是标准50欧,实际的阻抗形式是:R+jX),但是我不清楚,R和X的实际设计偏差能达到多少,还请各位先知能帮我给出一个估计范围?只有这个确定了,我才能确定片内阻抗网络的调整范围。

还有个问题是,假定我可以设计天线阻抗的虚部为容性,也就是为:R+1/(jwC)的形式,是不是我芯片内部的阻抗网络就可以采用电阻串联电容的形式实现(这样也就是R+1/(jwC)的最直观实现方式)。

在这里,我期望天线阻抗的虚部为容性的考虑是,如果阻抗的虚部为感性的话,芯片内部的阻抗网络是不是就应该采用电阻串联电感的形式实现。而电感在芯片内部是不容易实现的,特别是可调电感。不知道我这样的考虑是否正确。

PS:芯片内部阻抗网络模拟天线阻抗是可以实现,这个有很多论文支持,所以大家可以忽略对这个阻抗网络存在性的质疑。

但文献也没有给出天线的阻抗模型,只是给出了阻抗网络的实现,所以我不清楚应该如何依据天线设计阻抗网络。

希望各位大神帮我答疑解惑!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:关于天线仿真的一个问题

下一篇:关于差分信号的理解