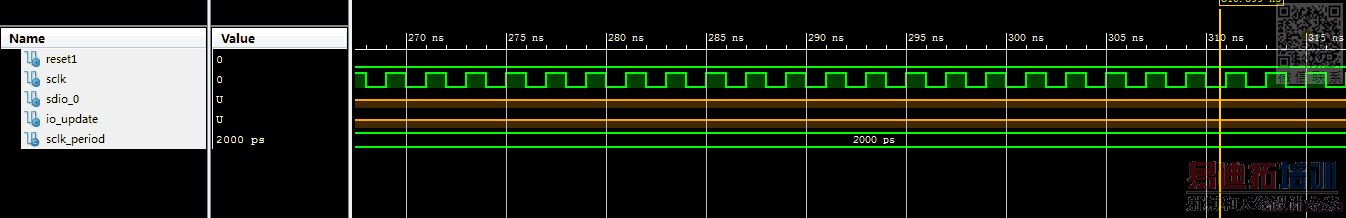

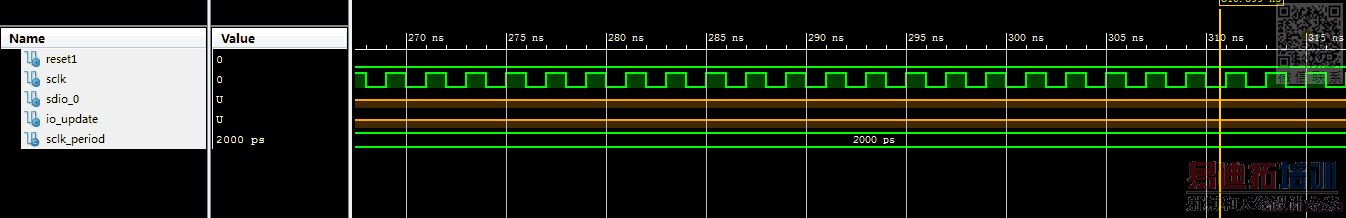

VHDL波形不对

录入:edatop.com 阅读:

我先写了一部分程序,但是发现出来的波形和预期的不一样,总是数据传不到sdio_0里,但是看了很久都看不出,所以跪求大神指导。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use ieee.STD_LOGIC_UNSIGNED.ALL;

entity data is

port(

reset1:in std_logic;

sclk: in std_logic;

sdio_0ut std_logic;

io_updateut std_logic

);

end data;

architecture Behavioral of data is

signal addr_mem: std_logic_vector(7 downto 0); --八位控制指令,第一位为1表示写,0表示读;

signal data_mem: std_logic_vector(31 downto 0); --寄存器的大小统一定义为32位;

signal addr_sig: std_logic_vector(4 downto 0) :="00000";

signal controls: std_logic :='1';

signal sdio: std_logic;

begin

addr_mem <= "000" & addr_sig;

sdio_0 <= sdio;

rst:process(sclk)

variable cnt_rst :integer range 0 to 7 :=0;

begin

if rising_edge(sclk) then --计数sclk_sig信号上升沿,每次减一

if reset1='1' then

if cnt_rst=7 then

null;

else

cnt_rst := cnt_rst + 1; --复位时长为255个SCLK周期

end if;

end if;

end if;

end process rst;

data1:process(sclk)

begin

if rising_edge(sclk) then

if reset1='0' then

case addr_sig is

when "00000" =>

data_mem <= B"11110000_00000000_00000000_00000000";

when "00001" =>

data_mem <= B"11010000_00000000_01000000_00000000";

when "00010" =>

data_mem <= B"00000000_00000000_00000000_00000000";

when "00011" =>

data_mem <= B"10000000_11000011_00100010_00000000";

when "00100" => data_mem <= B"00001111_01011100_00101000_11110110";

when "00111" =>

data_mem <= B"00000000_01010000_00000000_00000000";

when "01000" =>

data_mem <= B"00000000_10000011_00010010_01101111";

when "01010" =>

data_mem <= B"01001100_11001100_11001101_00001010";

when others => data_mem <= B"00000000_00000000_00000000_00000000";

end case;

end if;

end if;

end process data1;

con_trans:process(sclk)

variable i :integer range 7 downto 0 :=7;

begin

if rising_edge(sclk) then

if reset1='0' then

if controls='1' then

if i=0 then

controls<='0';

i:=7;

else

sdio<=addr_mem(i);

i:=i-1;

end if;

end if;

end if;

end if;

end process con_trans;

addr0:process(sclk)

variable addr0_i :integer range 31 downto 24 :=31;

begin

if rising_edge (sclk) then

if reset1='0' then

if controls='0' then

if addr_sig="00000" then

if addr0_i=24 then

controls<='1';

addr_sig<=addr_sig+1;

addr0_i:=31;

else

sdio<=data_mem(addr0_i);

addr0_i:=addr0_i-1;

end if;

end if;

end if;

end if;

end if;

end process addr0;

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use ieee.STD_LOGIC_UNSIGNED.ALL;

entity data is

port(

reset1:in std_logic;

sclk: in std_logic;

sdio_0ut std_logic;

io_updateut std_logic

);

end data;

architecture Behavioral of data is

signal addr_mem: std_logic_vector(7 downto 0); --八位控制指令,第一位为1表示写,0表示读;

signal data_mem: std_logic_vector(31 downto 0); --寄存器的大小统一定义为32位;

signal addr_sig: std_logic_vector(4 downto 0) :="00000";

signal controls: std_logic :='1';

signal sdio: std_logic;

begin

addr_mem <= "000" & addr_sig;

sdio_0 <= sdio;

rst:process(sclk)

variable cnt_rst :integer range 0 to 7 :=0;

begin

if rising_edge(sclk) then --计数sclk_sig信号上升沿,每次减一

if reset1='1' then

if cnt_rst=7 then

null;

else

cnt_rst := cnt_rst + 1; --复位时长为255个SCLK周期

end if;

end if;

end if;

end process rst;

data1:process(sclk)

begin

if rising_edge(sclk) then

if reset1='0' then

case addr_sig is

when "00000" =>

data_mem <= B"11110000_00000000_00000000_00000000";

when "00001" =>

data_mem <= B"11010000_00000000_01000000_00000000";

when "00010" =>

data_mem <= B"00000000_00000000_00000000_00000000";

when "00011" =>

data_mem <= B"10000000_11000011_00100010_00000000";

when "00100" => data_mem <= B"00001111_01011100_00101000_11110110";

when "00111" =>

data_mem <= B"00000000_01010000_00000000_00000000";

when "01000" =>

data_mem <= B"00000000_10000011_00010010_01101111";

when "01010" =>

data_mem <= B"01001100_11001100_11001101_00001010";

when others => data_mem <= B"00000000_00000000_00000000_00000000";

end case;

end if;

end if;

end process data1;

con_trans:process(sclk)

variable i :integer range 7 downto 0 :=7;

begin

if rising_edge(sclk) then

if reset1='0' then

if controls='1' then

if i=0 then

controls<='0';

i:=7;

else

sdio<=addr_mem(i);

i:=i-1;

end if;

end if;

end if;

end if;

end process con_trans;

addr0:process(sclk)

variable addr0_i :integer range 31 downto 24 :=31;

begin

if rising_edge (sclk) then

if reset1='0' then

if controls='0' then

if addr_sig="00000" then

if addr0_i=24 then

controls<='1';

addr_sig<=addr_sig+1;

addr0_i:=31;

else

sdio<=data_mem(addr0_i);

addr0_i:=addr0_i-1;

end if;

end if;

end if;

end if;

end if;

end process addr0;

end Behavioral;

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:想請問關於ADS momentun詳細教學

下一篇:HFSS 电感仿真问题