- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

低功耗无源超高频射频识别应答器芯片的射频电路

0 引 言

射频识别(radio frequency idenlificatinn,RFID)是20世纪90年代兴起的一种自动识别技术。RFID技术具有多种条形码技术所不具备的优点,应用范围十分广泛,可应用于第二代公民身份证、城市一卡通、金融交易、供应链管理、电刊文费(ETC)、门禁控制、机场行李管理、公共运输、集装箱识别、畜牧管理等,因此,掌握制造RFID芯片的技术变得非常重要。目前,日益增长的应用需求对RFID芯片提出了更高的要求,要求其容量更大,成本更低,体积更小,数据速率更高。根据这种情况,本文提出了一种长距离、低功耗的无源超高频UHF RFID应答器芯片射频电路。

RFID常用工作频率包括低频125kHz、134.2kHz.高频13.56MHz,超高频860~930MHz,微波2.45GHz,5.8GHz 等.因为低频125kHz、134.2kHz,高频13.56MHz系统以线圈作为天线,采用电感祸合的方式,其工作距离较近,一般不超过1.2m,带宽在欧洲及其他地区限制为几千赫兹。但超高频(860~93Uh1Hz)和微波(2.45GHz,5.8GHz)可以提供更远的工作距离,更高的数据速率,更小的天线尺寸,因此成为RFID的热点研究领域。

本论文提出的射频电路芯片采用支持肖特基二极管和电可擦除可编程只读存储器(EEPROM)的Chartered 0.35μm 2P4M CM0S工艺进行流片。肖特基二极管具有较低的串联电阻和正向电压,在将接收到的射频输入信号能量转换为直流电源供电时,能够提供较高的转换效率,从而降低功耗。在有效全向辐射功率(EIRP)为4W(36dBm)且天线增益为0dB的情况下,该射频电路芯片工作在915MHz,其读取距离大于3m,工作电流小于8μA。

1 射频电路结构

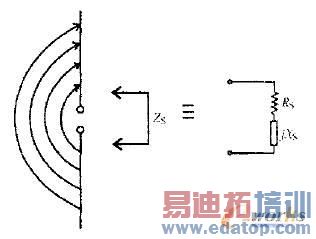

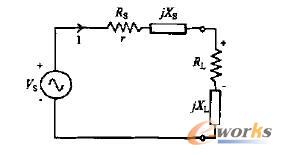

图1是UHF RF1D应答器芯片系统图,其主要包含了射频电路、逻辑控制电路和EEPROM。其中,射频电路部分又可以分为以下几个主要电路模块:本地振荡器和时钟产生电路、上电复位电路、电压参考源、匹配网络和反向散射电路、整流器、稳压器以及幅度调制(AM)解调器等。其中除天线外无外接元器件,天线部分采用偶极子结构,并通过匹配网络与整流器的输入阻抗进行匹配,作为整个芯片的唯一能量来源。其等效模型如图2所示。偶极子天线阻抗的实部由Rra和Rloss,两部分组成,其中Rra为偶极子天线的辐射阻抗,是偶极子天线固有的,一般为73Ω,它表征天线对外辐射电磁波的能力;Rloss为制作天线所用金属带来的欧姆电阻,一般只产生热量。天线阻抗的虚部X一般为正值,这是因为天线一般来说总是对外呈现电感性,此等效电感的大小一般取决于天线的拓扑结构和基板材质。整流器将耦合到的射频输入信号功率转换成芯片所需的直流电压。稳压器则将该直流电压稳定在一定的电平上,并限制该直流电压的幅度以保护芯片不会因电压过高而击穿。AM解调器用于从接收到的载波信号中提取相应的数据信号。反向散射电路通过可变电容来改变射频电路的阻抗,从而将应答器数据发送到RFID询问器或读卡器。上电复位电路用于产生整个芯片的复位信号。与13.56MHz的高频(HF)应答器不同,915MHz的UHF应答器不能从载波中分频得到本地时钟,而只能通过内建一个低功耗的本地振荡器为数字逻辑电路部分提供时钟。所有这些电路模块将在下文中逐一详细说明。

图1 UHF RF1D应答器芯片系统图

图2 应答器天线的等效电学模型

2 电路设计与分析

2.1 整流器和稳压器电路

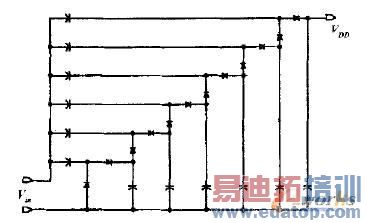

本论文采用肖特基二极管组成的Dickson电荷泵作为整流器电路,其电路原理图如图3所示。这是因为肖特基二极管具有较低的串联电阻和结电容,在将接收到的射频输入信号能量转换为直流电源供电时可以提供较高的转换效率,从而降低功耗。全部肖特基二极管均通过poly-poly电容连接在一起,其中纵向电容在输入电压Vin的负半周期进行充电、储能,而横向电容在Vin的正半周期进行充电、储能,从而产生直流高电压,其产生的电压为:

VDD=n·(Vp,RF-Vf,D)

其中Vp,RF是输入射频信号的幅度,Vf,D是肖特基二极管的正向电压,n为所采用电荷泵的级数。

图3 整流器电路图

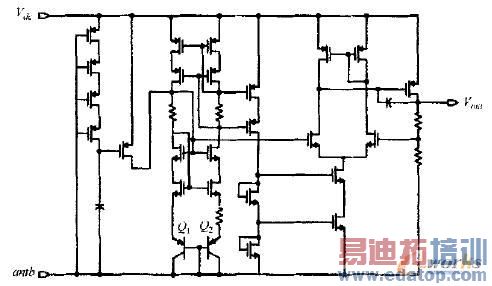

图4是稳压器的电路图。该电路是要将整流器输出的直流电压稳定在一定的电平上,并为整个应答器芯片提供稳定的工作电压,来保证不会由于应答器芯片物理位置变化引起直流电压幅度的改变,避免可能导致的芯片击穿,从而起到保护应答器芯片的作用。该电路采用了自偏置的Cascnde结构,之所以选择该电路结构是因为Cascnde结构存在共栅管的隔离作用,使其具有很好的抑制电源波动的能力,从而提高电源抑制比(PSRR),保证两个支路电流的基本稳定。其中 Q1与Q2的面积比为1∶8。此外,与一般的HF RFID应答器不同,我们在设计中采用了具有低压启动电路的低功耗电压参考源,以降低芯片的整体功耗

图4 稳压器电路图

2.2 匹配网络和反向散射电路

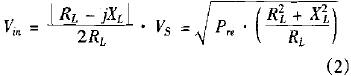

与13.56MHz的HF应答器不同,UHF频段的RFID应答器采用偶极子天线。图5是应答器与天线的SPICE(simulation program with integrated circuit emphasis)等效电路图。在该等效SPICE电路模型中,接收到的射频载波信号为Vs,天线的阻抗为Zs=Rs+jXL,可以看作是电压源Vs的内阻,而应答器芯片的等效输入阻抗则是ZL=RL-jXL。所以,当ZL=Zs*时,阻抗匹配,功率传输最大。在阻抗匹配的情况下,从带有天线的应答器看去,得到的阻抗应该是Z=2RL,从而我们得到接收功耗Pre和电压摆幅VS之间的关系为侧:

![]()

则输入到芯片两端的电压摆幅Vin为:

为了达到阻杭匹配,电路还需要对匹配网络进行阻抗变换,这样才能使得天线的内阻和射频电路部分的输人阻抗达到共扼匹配,因此我们采用了L型匹配网络。由于芯片集成电感成本较高,而且精度较低,所以我们利用天线的电感作为匹配电感,将匹配电容集成到芯片中去。经过计算,该射频电路的输入阻抗约为 (105-j406)Ω。

图5 应答器与天线的SPICE等效电路图

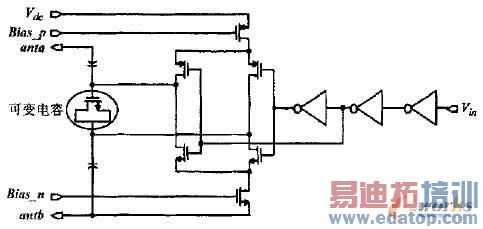

图6为反向散射电路原理图。反向散射电路通过可变电容来改变射频电路的阻抗,从而将应答器数据发送到RFID询问器或读卡器。该可变电容采用MOS变容二极管来实现,在标准CMOS工艺中,我们可以利用MOS管栅极到衬底的压控可变电容,将MOS变容二极管的栅极作为电容器的一端,源端和漏端接在一起作为电容器的另一端。

图6 反向散射电路图

2.3 AM解调器电路

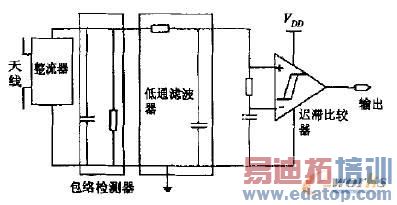

AM解调器电路用于将接收到的调制载波还原成数字信号供基带处理,解调电路由包络检测电路、滤波电路和比较器三部分构成(如图7所示),其中比较器采用迟滞比较器来降低误码率。包络检测器采用与整流器相同的电路来提取包络信号。低通滤波器则用来消除噪声信号以及电源上的纹波。最后,通过迟滞比较器将包络信号在比较器的输出端恢复为数字信号。

图7 AM解调器原理图

2.4 上电复位电路

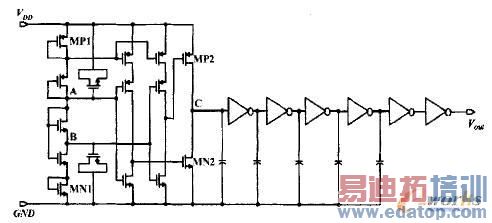

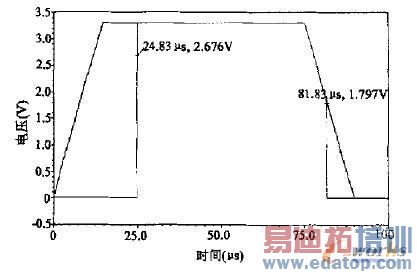

上电复位电路有两个主要作用,一是当应答器进入询问器或读卡器的有效区域,电源电压己经达到正常工作电位时,产生整个芯片的复位信号;其次是当电源电压突然降低时,该电路可以通过复位防止逻辑电路出现功能错误。图8是上电复位电路图,该电路的上电复位延迟时间为10μs。当际从零开始不断增大并超过起拉电压2.4V时,P管MP1和N管MN1率先导通,使得A、B点电位从0开始随着喻的增大而逐步上升,经过反相器,MP2和MN2管栅极电压都随着VDD的上升呈线性变化,所以在开始阶段MN2导通,MP2截止,致使C点电压一直为0(有效复位)。当VDD到达更高电位时,A点电位也同时上升到一定电平,使得MN2管截止,而此时MP2管导通,使C点电位迅速上升,经过几级缓冲器,就得到了一个从逻辑0到1的跳变信号输出,从而使电路开始正常工作。而后面的几级缓冲器加电容负载的级联是为了获得大约10μs,的时间延迟,即当VDD高于2.4V且保持10μs后复位信号完成跳变,从而实现电路稳定工作,其仿真结果如图9所示。

图8 上电复位电路原理图

图9 上电复位电路仿真结果

2.5 本地振荡器和时钟产生电路

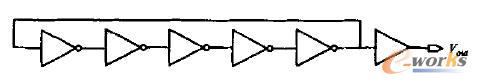

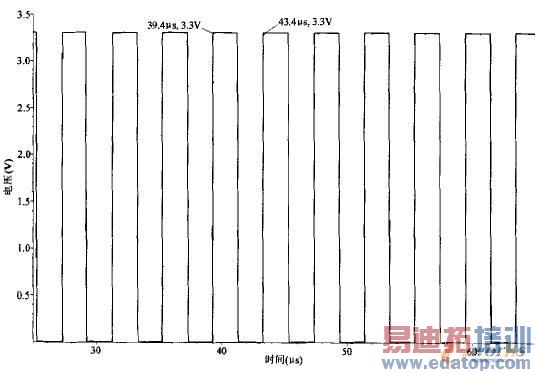

与13.56MHz的HF应答器不同,915MHz的UHF应答器不能从载波中分频得到本地时钟,而只能通过内建一个低功耗的本地振荡器为数字逻辑电路部分提供时钟,由于协议中规定时钟频率可以接受±30%的误差,对于时钟频率的精度要求不高,因此可以采用比较简单的振荡器结构以降低芯片功耗。经过分析,我们决定采用奇数级全差分反相器组成的环形振荡器,这不但可以很好地抑制共模电压的变化,而且还可以获得很好的电源抑制特性。图10为本地振荡器与时钟产生电路原理图。经过仿真测试,在考虑温度、电源电压和工艺角变化的全条件情况下,该电路输出频率约为250kHz ,其变化误差保证了数据的位速率精度(bit rate accuracy)小于VDD15%,对逻辑电路性能没有任何影响,较好的满足了系统设计要求。图11为仿真获得的时钟信号。

图10 本地振荡器与时钟产生电路原理图

图11 仿真得到的时钟信号

3 测试结果与分析

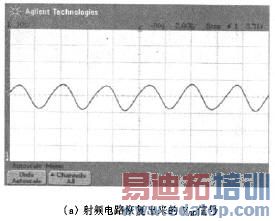

该射频电路芯片采用支持肖特基二极管和EEPROM的Chartered 0.35μm 2P4M CMOS工艺进行流片。其不含I/O焊盘(PAD)的核心电路芯片面积为300μm×720μm。除两个PAD用于连接外部天线以外,其余PAD均用于芯片功能测试。图12为射频电路芯片连接外部天线后与读卡器进行通信测试获得的波形图,测试采用北京清华同方微电子有限公司符合ISO/IEC 18000-6B标准的THM6BC1-915型UHF RFID读卡器进行。其中图12(a)是在接收到读卡器发射的射频信号后,经过整流器和稳压器电路得到的VDD波形,其平均值为3.3V,仅有小于 20mV的纹波,很好地满足了设计指标要求。图12(b)为经射频电路芯片解调得到的由读卡器发送的数字信号。经测试,在EIRP为4W(36dBm)且天线增益为OdB的情况下,该射频电路芯片工作在915MHz,其读取距离大于3m,工作电流小于8μA。

图12 射频电路芯片的测试波形图

4 结 论

本论文提出了一种符合ISO/IEC 18000-6B标准的高性能低功耗无源UHF RFID应答器芯片射频电路,该射频电路工作于915MHz,除天线外无外接元器件,通过肖特基二极管整流器从射频电磁场接收能量。采用支持肖特基二极管和EEPROM的Chartered 0.35μm 2P4M CMQS工艺进行流片,其核心面积为300μm×720μm。该RFID射频电路包括本地振荡器、时钟产生电路、复位电路、匹配网络和反向散射电路、整流器、稳压器以及AM解调器等几个主要模块。本文通过对各模块电路的设计与优化,设计出符合标准要求的低功耗射频电路。采用符合ISO/IEC 18000-6B标准的THM6BC1-915Y2型UHF RFID读卡器进行了测试,测试结果表明读取距离大于3m,其结果很好的满足了无源UHF RFID应答器系统的指标要求。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:用于IEEE 802.11b/g WLAN直接下变频接收机的射频前端设计

下一篇:一种新的无线网络通信技术Zigbee