- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

无线通讯OFDM调制技术介绍和设计实现

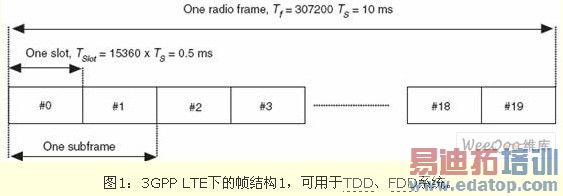

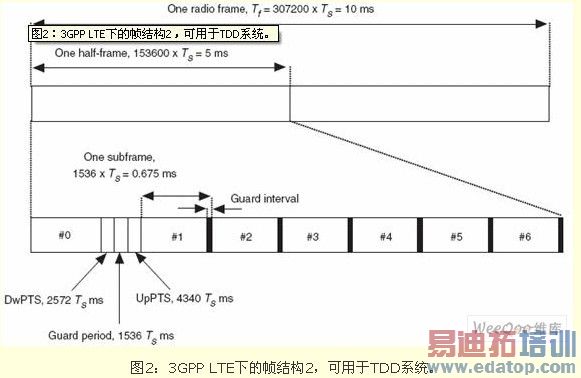

OFDM是现代宽带无线通信系统应用的技术。为了减少高数据率OFDM系统中各信道间影响带来的失真,引入循环前缀(CP)来消除码间干扰(ISI)。它将一个IFFT包的最后部分复制到OFDM符号序列的前端。注意,CP的长度必须长于色散信道的长度以彻底消除ISI。在发射器中,OFDM调制包括快速傅立叶逆变换(IFFT)运算和CP的插入。而在OFDM接收器中,CP在数据包送往FFT解调前被移除。新一代的无线系统以高动态配置为标志,其中CP的长度随着传输模式,帧结构(见图1、2)以及更高级的协议而改变。例如,3GPP LTE中的CP配置每一个时隙都不同。CP的长度基于具有2048时间间隔的OFDM符号。WiMAX系统中可以有几种相似而不同的CP结构。

OFDM调制的实现

下面将讨论如何实现OFDM调制及解调中循环前缀的插入与消除。

FFT与FFT反变换:在OFDM调制中最关键的运算就是IFFT,相类似,OFDM解调的核心为FFT。宽带系统中的高FFT吞吐率是至关重要的,尤其是在FFT被多路数据通道共享时。

在WiMAX以及3GPP LTE这类现代可扩展无线系统中,在运行中可重新配置的能力同样成为系统要求的一个重要指标。可变流模式下的FFT MegaCore函数瞄准的是可重新配置的无线通讯,是设计OFDM系统时的一个很好选择。

FFT的MegaCore函数被设定为可变流模式,它允许FFT的大小和方向逐包改变。它还采用了存储效率模式——这是FFT核的唯一模式,直接从FFT的蝶形引擎中输出位反转符号。可以在FFT核之外结合带有循环前缀插入的位反转。这样,整个OFDM调制可以节省出一个单缓冲器。

FFT模块复用:为了减少逻辑门数,FFT模块通常采用比其他基带模块更快的时钟频率并复用。FFT模块可以被不同的源共享,譬如,多路天线、时分双工(TDD)复用中的发射与接收,以及频分双工(FDD)系统。FFT模块也可以与其他功能模块共享,如振幅因数减小或信道估计模块。不过,这些复用取决于用户特定的算法,而非通用设计。这篇文章将集中讨论最常见的无线通讯系统应用:如MIMO技术、TDD和FDD通信。

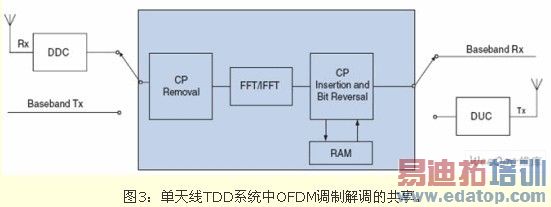

TDD操作:在TDD基站中,发送和接收发生在不重叠的时隙中。FFT模块可以很容易地在采用合适的信号多路复用技术的发射机和接收机之间共享。图3显示一个典型的单一天线TDD OFDM调制器。

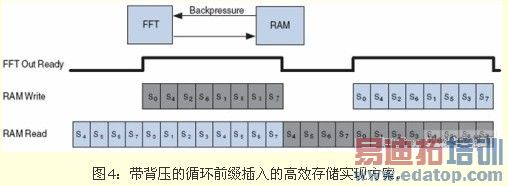

在发射数据通道中,基带数据被直接送入IFFT模块。为在IFFT运算后插入CP并进行位反转操作,可以采用很多种不同的结构。图4为一个使用Altera Avalon Streaming接口(Avalon-ST)的高效实现方案。IFFT输出的位反转信号按次序被写入一个单缓冲器,在那里,来自上一个OFDM符号的自然顺序的样本通过双端口RAM同时被读出。产生循环前缀时,通过Avalon-ST背压流量控制使FFT核停转。附加了循环前缀的连续OFDM符号再被送到数字上变频器(DUC)来传输。

而在接收通道中,经过数字下变频器(DDC)后,循环前缀从OFDM符号中被移除。如图3示,循环移除模块找到OFDM符号序列的正确起始位置然后把数据送向FFT解调。FFT模块后的单缓冲器只能作为接收通道中的位反转缓冲器而没有背压流量控制。为了重复利用控制单元,图3中CP的插入和移除模块能够区分数据包是否用来发射还是接收,并采取相应操作。在这种存储器高效率执行中,FFT核工作频率为符号速率。一个单缓冲器足以完成循环前缀的插入和位反转。

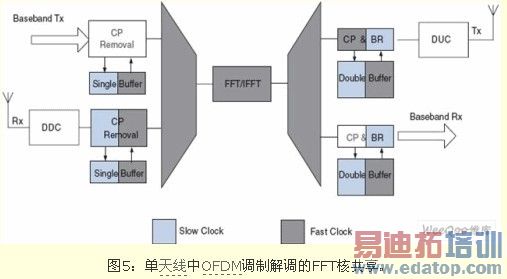

FDD操作:在FDD中,发送和接收是同时进行的。FFT核的共享要求其工作频率不低于基带符号传输速率的两倍。发射和接收数据通道各需要一个专用数据缓存。

图5描述的是FDD系统下FFT复用的一种可能配置。数据发送和接收通道的操作类似于TDD系统,其区别在于这些操作是同时进行的。因此,pre-FFT数据必须被缓存且把频率提高到快时钟频率。用一个单缓冲器就足以改变速率,因为缓冲器的写时钟频率总是低于或等于读时钟频率。

在当前的数据包以低时钟速率被写入缓冲器的时候,上一个包中的数据以高时钟率被读出。当读写操作在同一存储位置时,需要配置双端口RAM来输出旧存储内容。FFT处理后,高速率数据经过双端RAM后被还原到OFDM的发送速率。这个post-FFT存储缓冲器也作为一个位反转缓冲器。由于速率从高到低的改变,如果需要连续码流输出,就需要一个双缓冲器,即当一个FFT包被写入缓冲器时,上一个包中的数据从另一个缓冲器被读出。

MIMO结构设置

多天线结构是现代无线系统中的强制性需求,这些系统包括WLAN,WiMAX和3GPP LTE系统。在多输入输出(MIMO)系统中进行OFDM调制的一个很直接的操作就是复制数据通道,包括用于每一根天线的FFT核。

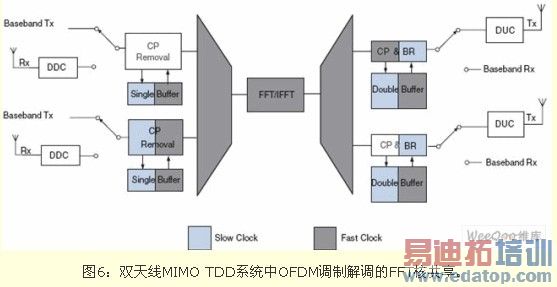

一种资源更友好的解决方案是共享每条天线的FFT核。为实现MIMO中的FFT复用,FFT核的频率至少要比基带数据传输速率快n倍,这里的n为天线的根数。当结合MIMO、TDD和FDD时,同一个FFT核能在两维上被共享,代价是需要pre-FFT数据缓冲。

图6描述的是TDD模式下一种双天线MIMO发射器的基本配置。FFT核被两条天线以及发送和接收器复用。循环前缀的插入和移除控制单元必须能够用于发射和接收。由于时钟频率的差异,每根天线的post-FFT数据处理需要一个双缓冲器。

OFDM调制实例

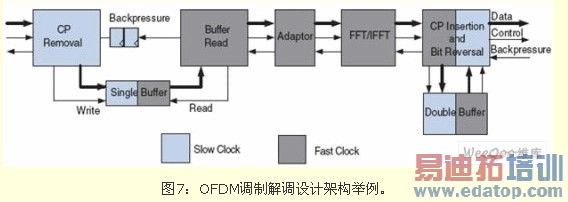

下面的OFDM调制和解调在Altera Stratix III FPGA上进行,FFT和存储缓冲器使用MegaCore函数。这个例子打算用于采用FFT复用的系统,为了实现共享,这里,FFT核的时钟率要比基带信号快很多。该设计旨在实现可重配置结构的OFDM系统,它的FFT size和循环前缀的大小在执行中可变。Pre-FFT数据通过一个单缓冲器改变速率,Pre-FFT位反转数据通过一对缓冲器改变速率和次序。所有的控制模块支持TDD操作并被发射器和接收器共享。该应用实例可以很容易扩展到MIMO、TDD或者两者结合的系统中,例如图6中的系统以及图5介绍的FDD系统。

功能描述:这个设计实例包含两部分:OFDM调制和OFDM解调。前者包含IFFT和循环前缀的位反转插入,后者包含循环前缀的移除模块和改变数据速率的缓冲器。图7为这两者的高级集成。你可以把它看作是图3中的单天线TDD系统的一种扩展。附加的pre-FFT缓冲器使设计更容易地扩展到具有FFT复用的MIMO或FDD系统。

Post-FFT处理:OFDM调制过程中的CP插入包含4个功能子模块:

1. 使用双时钟双端口RAM的双缓冲器

2. 位反转的存储写模块

3. 循环前缀插入的内存读取模块

4. 时钟同步模块

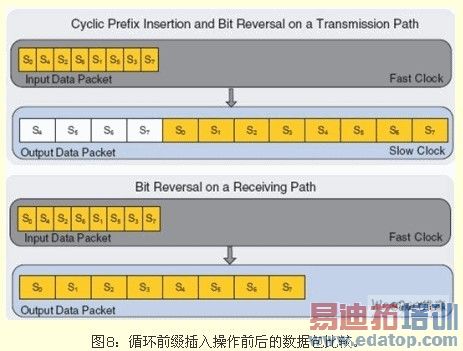

在发射数据通道中,位反转的IFFT输出数据在循环前缀插入模块被读入。一个控制单元分析数据地址并把它写入相应的存储单元。在一个完整的IFFT数据包被写入后,与循环前缀相应的最后几个样本以自然顺序读出。与此同时,如果有容量,来自下一个IFFT包的数据会被写入另一个缓冲器。如果两个缓冲器都有数据需要读取,会有一个延迟信号经过Avalon Streaming接口背压送到IFFT核。经过OFDM调制后的数据通常是连续的。而其后的模块,如IF调制解调器和天线,不应该施加背压。

在接收数据通道中,post-FFT处理限制了位反转和速率改变。位反转的FFT输出数据会被写入到正确的内存地址,就像之前所做的一样。一旦一个完整的数据包被写入了缓冲器,它将会按正常顺序依次读出。要特别注意避免过度的背压。由于读时钟频率通常慢于写时钟,故需要一个双缓冲器。图8讲述了post-FFT的数据处理。控制信号指明两个时钟域的缓存器状态,并通过同步逻辑进行同步。

Pre-FFT处理:Pre-FFT处理包括4个模块:

1. 循环前缀的移除或存储器写

2. 存储读取或速率改变

3. 双时钟双端口RAM

4. Avalon码流准备好延迟转换器

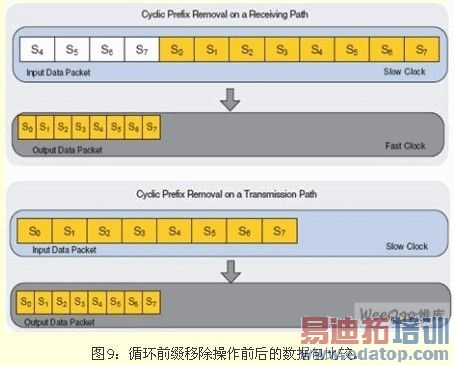

如前面所讨论,如果FFT为了资源共享采用不同速率的时钟,则需要pre-FFT数据缓冲器。在接收通道上,每当输入数据开始写入单缓冲器时,循环前缀移除模块开始记数。当整个数据包都被写入这个单缓冲器时,记数值开始从0地址被读出。

对于固定的FFT size,由于读时钟频率并不比写时钟慢,用一个单缓冲器就够了。但如果FFT size是变化的,一个单缓冲器恐怕就不够了。举个特殊的例子,假设两个时钟工作在同一频率。在这种情况下,当新的数据被写入内存,上一个数据包中的数据会从同一个存储地址被读出。如果上一个数据包的FFT/IFFT size更大,那么当前包的写操作会早在上一个数据包读操作完成前结束。这样的话,为了阻止写入过多的数据,就必须延迟上行数据流模块的运行直到上一个大数据包的读操作完成。

所幸的是,这种背压只会在FFT size由大变小时才会被施加。在实际的系统中,FFT size不太可能频繁的改变。如果它只在帧边界改变,由于帧符号之间是静止区,就永远不会施加背压。此外,为了避免使用背压,读信号和FFT核可以采用更高速率的时钟,这样读操作会在写操作之前完成。所需的时钟频率取决于最坏情况下FFT size的变化比。举个极端的例子,如果FFT size从2048减到128,那么读时钟的频率至少需要比写时钟快16倍。

在发射数据通道上,CP移除子模快只是将输入数据按次序写入单缓冲器。同样的数据以不同的速率被读出。图9讲述了pre-FFT的数据操作。在接收通道上,数据通过天线进入OFDM解调器,其后通常还接有IF调制解调器。这样,接收模式下的pre-FFT模块不会再对上行数据流模块施加背压。对于TDD操作,在pre-FFT数据缓冲时,可以复用post-FFT双端口RAM实现位反转,因为这些操作在时间上是错开的。

时钟方案:该设计中采用两个时钟域,clk_f和clk_s。FFT核运行在快时钟clk_f上。当时钟clk_f比clk_s快时,两个时钟域将会存在异步。握手信号将会被?入来同步域间的控制信号。尽管在实际系统中时钟clk_f的频率通常为clk_s频率的几个整数倍,但在这个设计中,两者频率也可以相同。这里,两个时钟必须同步。由于单缓冲器存储深度的限制,如果两个时钟同步而只是速率不同,就必须去掉解调器中的时钟同步模块。不过在实际系统中不需要考虑这一点,因为如果FFT核没有被复用就没必要使用pre-FFT缓冲器了。

接口和I/O端口:该设计实例使用了数据传输控制的Avalon Streaming协议。为了支持大小可变的FFT size、循环前缀,以及FFT方向运行时间(run time)的变化,必须对这些run time信号进行缓冲并把它们与输出数据数据包开始(SOP)信号对齐。Therefore, in every control module of OFDM modulation and demodulation, some logic is dedicated to signal alignment.因此,在OFDM调制解调中的每个控制模块中都有一些逻辑信号专用于信号对齐。

该实例中也通过Avalon Stream信号sink_ready(输入准备好信号)和source_ready(输出准备好信号)来支持背压。循环前缀插入模块中输入准备好延迟选0和输出准备好延迟选44。循环前缀移除模块的输入准备好延迟选0。不过,因为输出数据取自存储器,后面的缓冲器读取子模块的输出准备好延迟选2。由于FFT核为延迟0,为了实现与FFT核的连接,需要在在缓冲读模块与FFT核之间插入一个延迟适配器。延迟适配器用延迟2接收输入数据,然后用延迟0输出数据。适配器也支持背压并把可重配置的循环前缀的大小和FFT的方向信号与输出数据包对齐。

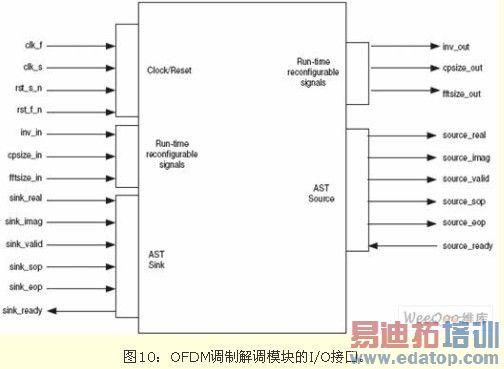

调制解调的输入输出信号是有符号的定点格式但位宽度是可配置的。在可变流模式中,IFFT核的输出数据具有基于最大IFFT size的满分辨率。如果必要,可以在循环前缀插入模块中切断数据序列,也可以设置位宽参数。图10所示为OFDM调制解调模块的I/O端口。

本文小结

这篇文章提供了一个可重配置无线系统中的OFDM调制解调的实现例子。设计架构的核心为FFT模块的复用。

这个设计实例实现了3GPP LTE系统的OFDM调制解调,支持FFT size与循环前缀大小的可重配置。该设计实例也可用于WiMAX、WLAN以及其他基于OFDM的现代通讯系统。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:DMR终端锁相调频接收机设计

下一篇:卫星通讯的通道仿真和测试解决方案