- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

射频和硬件EMC规范讲解

录入:edatop.com 点击:

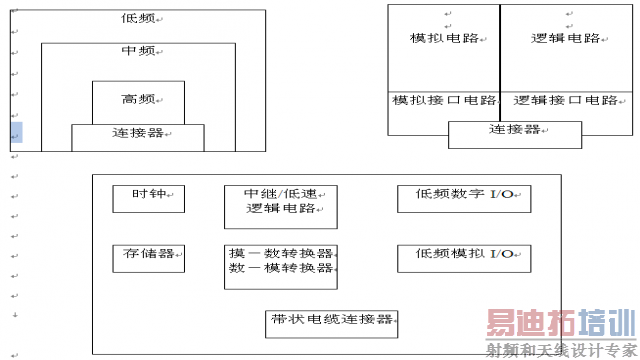

二、布局

下面是电路板布局准则:

1、 晶振尽可能靠近处理器

2、 模拟电路与数字电路占不同的区域

3、 高频放在PCB板的边缘,并逐层排列

4、 用地填充空着的区域

三、布线

1、电源线与回线尽可能靠近,最好的方法各走一面。

2、为模拟电路提供一条零伏回线,信号线与回程线小与5:1。

3、针对长平行走线的串扰,增加其间距或在走线之间加一根零伏线。

4、手工时钟布线,远离I/O电路,可考虑加专用信号回程线。

5、关键线路如复位线等接近地回线。

6、为使串扰减至最小,采用双面#字型布线。

7、高速线避免走直角。

8、强弱信号线分开。

四、屏蔽

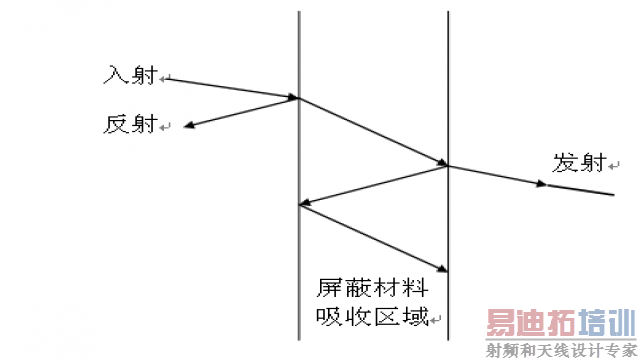

1、屏蔽 > 模型:

高频射频屏蔽的关键是反射,吸收是低频磁场屏蔽的关键机理。

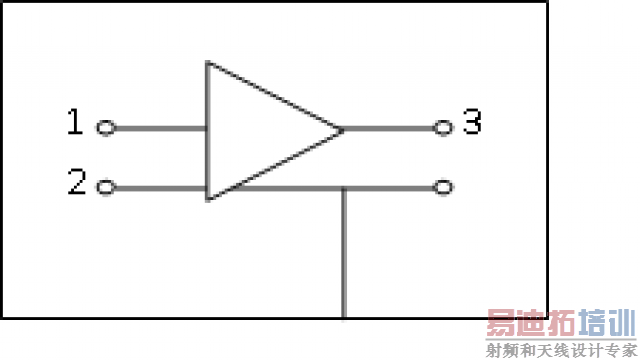

2、工作频率低于1MHz时,噪声一般由电场或磁场引起,(磁场引起时干扰,一般在几百赫兹以内),1MHz以上,考虑电磁干扰。单板上的屏蔽实体包括变压器、传感器、放大器、DC/DC模块等。更大的涉及单板间、子架、机架的屏蔽。

3、 静电屏蔽不要求屏蔽体是封闭的,只要求高电导率材料和接地两点。电磁屏蔽不要求接地,但要求感应电流在上有通路,故必须闭合。磁屏蔽要求高磁导率的材料做 封闭的屏蔽体,为了让涡流产生的磁通和干扰产生的磁通相消达到吸收的目的,对材料有厚度的要求。高频情况下,三者可以统一,即用高电导率材料(如铜)封闭并接地。

4、对低频,高电导率的材料吸收衰减少,对磁场屏蔽效果不好,需采用高磁导率的材料(如镀锌铁)。

5、磁场屏蔽还取决于厚度、几何形状、孔洞的最大线性尺寸。

6、磁耦合感应的噪声电压UN=jwB.A.coso=jwM.I1,(A为电路2闭合环路时面积;B为磁通密度;M为互感;I1为干扰电路的电流。降低噪声电压,有两个途径,对接收电路而言,B、A和COS0必须减小;对干扰源而言,M和I1必须减小。双绞线是个很好例子。它大大减小电路的环路面积,并同时在绞合的另一根芯线上产生相反的电动势。

7、防止电磁泄露的经验公式:缝隙尺寸<λmin/20。好的电缆屏蔽层覆视率应为70%以上。

五、接地

1、300KHz以下一般单点接地,以上多点接地,混合接地频率范围50KHz~10MHz。另一种分法是:< 0.05λ单点接地;< 0.05λ多点接地。

2、好的接地方式:树形接地

3、信号电路屏蔽罩的接地。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:降低RF电路寄生信号的八个设计规则

下一篇:技术牛人详解矢量信号分析仪原理