- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

信号完整性不佳的因素

录入:edatop.com 点击:

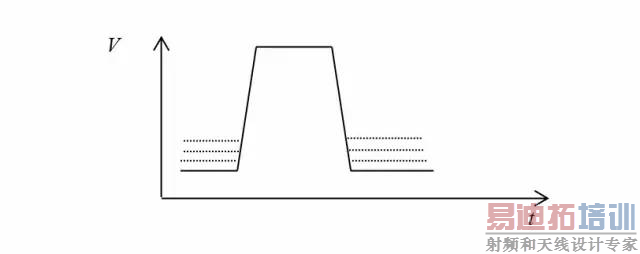

1、线电阻的电压降的影响——地电平(0电平)直流引起的低电平提高

图中虚线为提高的情况。提高幅度与IC的功耗大小、IC密度、馈电方式、地线电阻(R) 、馈电的地线总电流有关。 ΔV地= ΔI× ΔR

2、 信号线电阻的电压降的影响

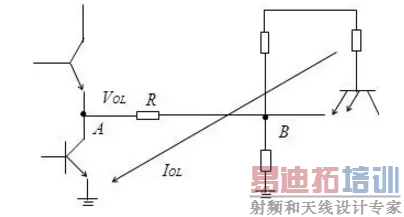

a) IC输出管脚经过印制导线或电缆到另一IC的输入脚,

输出低电平电流在印制导线或电缆电阻上引起一个低电平的抬高,其值为ΔVOL=IOL×R 。 见图中的上面一条虚线。

显而易见,低电平的抬高与印制导线电阻值及输出低电平电流有关,如下图所示:

B点的低电平比A点的低电平高

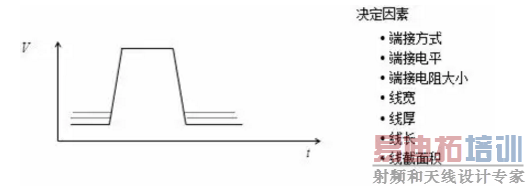

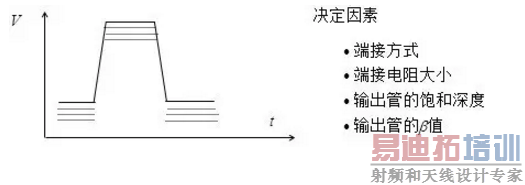

注意:当IC输出脚为低电平时,如果此器件不是驱动器, 而是一般器件,则由于输出低电平电流太大, 远大于器件手册给出的值,输出三极管将退出饱和区,进入工作区,使输出低电平抬高很多。如下图中上面一条虚线所示:

决定因素:端接方式

端接电阻大小

输出管饱和深度

输出管β值

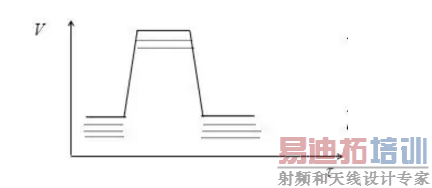

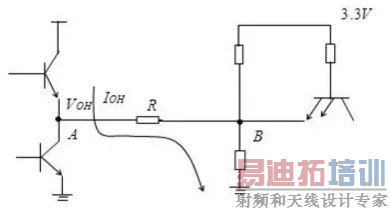

b) IC输出管脚经过印制导线或电缆到另一个IC的输入脚,输出高电平电流在印制导线或电缆电阻上引起一个高电平的降低,其值为ΔVOH=IOH× R,见下图中高电平上的下面虚线:

R由下列因素决定:线宽、线厚、线长

显而易见,高电平的降低与印制导线或电缆电阻值及输出高电平电流有关,如下图所示:

B点的高电平比A点的高电平要低

注意: IC输出脚为高电平时, 如果此器件不是驱动器,而是一般器件, 则由于输出高电平电流太大,远大于器件手册给出的值时,输出管也会退出饱和区,进入工作区,使输出高电平降低很多。如下图中下面一条虚线所示:

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:天线增益的计算公式

下一篇:射频回波损耗、反射系数、电压驻波比、S参数的含义与关系