- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

RF电路中如何选择LDO稳压器PSRR和噪声

LDO是一种微功耗的低压差线性稳压器,它具有极低的自有噪声和较高的电源抑制比(PSRR)。SGM2007高性能低压差线性稳压器在10Hz至 100kHz频率范围内的输出噪声为30 µV(RMS),在 1 kHz 的频率下电源抑制比(PSRR)高达73dB,它能够为诸如射频(RF)接收器和发送器、压控振荡器(VCO)和音频放大器等对噪声敏感的模拟电路的供电提供低噪声、电源纹波抑制比(PSRR)和快速瞬态响应,它的使能电路兼容TTL电平适合数字电路供电。SGM2007的输入电压在2.5V至5.5V之间,适合蓝牙数码相机和个人数字助理(PDA),以及诸如无线和高端音频产品等单个锂电池供电或固定3.3V和5V系统。

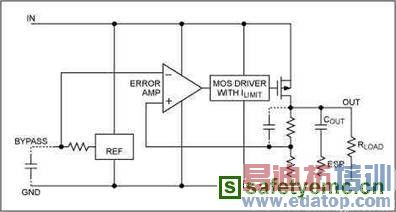

LDO的低压差线性稳压器的结构主要包括启动电路、恒流源偏置单元、使能电路、调整元件、基准源、误差放大器、反馈电阻网络,保护电路等,基本工作原理是这样的:系统加电,如果使能脚处于高电平时,电路开始启动,恒流源电路给整个电路提供偏置,基准源电压快速建立,输出随着输入不断上升,当输出即将达到规定值时,由反馈网络得到的输出反馈电压也接近于基准电压值,此时误差放大器将输出反馈电压和基准电压之间的误差小信号进行放大,再经调整管放大到输出,从而形成负反馈,保证了输出电压稳定在规定值上;同理如果输入电压变化或输出电流变化,这个闭环回路将使输出电压保持不变,即:

Vout=(R1+R2)/R2 * Vref

Power supply ripple rejection ratio (PSRR)是反应LDO输出对输入纹波抑制的一个交流参数,输出和输入的频率是一样的。和噪声(Nosie)不同,噪声一般为在10Hz至100kHz 频率范围内一定输入电压下其输出噪声电压的均方值,PSRR的单位是dB。

PSRR=20 log(△vin/△vout)

大多数蜂窝电话基带芯片组需要三组电源:内部数字电路、模拟电路和外设接口电路。基带处理器(BB)的数字电路供电电压的典型值为1.8V至 2.6V,一般情况下,Li+电池电压降至3.2V-3.3V时电话将被关闭,对于为基带处理器供电的LDO来说至少有500至600mV的压差,因此对压差要求不高。另外,数字电路本身对LDO的输出噪声和PSRR的要求也不高,而是要求LDO在轻载条件下具有极低的静态电流。

基带处理器内部模拟电路供电电压典型值是2.4V至3.0V,压差在200mV至600mV。要求LDO具有较高的低频(GSM电话为217Hz)纹波抑制能力,消除由RF功率放大器产生的电池电压纹波。LDO始终保持有效工作状态,同样需要较低的静态电流指标。

RF电路分为接收和发送两部分,供电电压典型值为2.6V至3.0V,其中低噪声放大器(LNA)、混频器、锁相环(PLL)、压控振荡器(VCO)和中频(IF)电路需要低噪声、高PSRR的LDO。实际应用中,VCO、PLL电路的性能直接影响射频电路指标,如发射频谱的纯度、接收器的选择性、模拟收发器的噪声、数字电路的相位误差等。噪声会改变振荡器的相频和幅频特性,同时振荡器环路也会进一步放大噪声,可能对载波产生调制。LDO输出噪声受其内部设计和外部旁路、补偿电路的影响。如图是线性稳压器的简单框图。导致LDO输出噪声的主要来源是基准

线性稳压器的简单框图

为降低基准噪声,用于连接基准旁路电容。增大旁路电容能够使基准噪声成为产生LDO输出噪声的次要因素,有利于减小输出噪声。建议使用陶瓷电容的典型值为 470 pF 到 0.01 µF 。也可使用此范围以外的电容,但会对输入电源上电时LDO 输出电压上升的速度产生影响,旁路电容值越大,输出电压上升速率越慢。在使用时这点要注意。

影响LDO输出噪声的其它因素还有:LDO内部极

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:移动设备的电池消耗在那里

下一篇:手机支付产业技术关键