- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

集成电路电磁干扰EMC测试方法

一、前言:

集成电路产业是我国高新技术产业的一个重要部分,它带动了其它产业的蓬勃发展,集成电路已成为各个行业中电子、机电设备智能化的核心,起着十分重要的作用。

近年来越来越多的电路设计人员和应用人员开展集成电路的EMC设计和测试方法的研究,EMC性已成为衡量集成电路性能的又一重要技术指标。随着集成电路集成度的提高,越来越多的元件集成到芯片上,电路的功能和密度增加了,传输脉冲电流的速度提高了,工作电压降低了,集成电路本身的电磁骚扰与抗干扰问题已成为集成电路的设计、制造业关注的课题。集成电路EMC的研究不仅涉及集成电路自身的电磁骚扰与抗扰度测试和设计方法研究,而且有必要与集成电路的应用相结合,将强制性标准对设备和系统的EMC要求,结合到集成电路的设计中,使电路更易于设计出符合标准的最终产品。电磁骚扰小的集成电路更有利于产品的EMC设计,可以减少系统设计的负担,节约滤波、屏蔽等措施的费用,因此开展集成电路的EMC设计和检测研究能为电路的应用提供设计指南,节约最终产品的成本。

集成电路的广泛应用,反过来对其又提出了更高的要求,人们需要性能更好、可靠性高、成本更低的集成电路。从20世纪60年代以来正如摩尔定律预计的那样每隔18到 24个月芯片上的元件数翻了一番,出现了在芯片的价格持续降低的同时,性能和可靠性不断提高的行业特点。集成的元件数的提高可以通过减小芯片上的关键尺寸(CD)或最小化特征尺寸来实现,这样在集成度提高的同时芯片的速度也提高了。由于集成电路通过高速的脉冲数字信号来进行工作,工作频率越高产生的电磁骚扰频谱越宽,越容易引起对外辐射的EMC方面的问题。

二、研究对象

在集成电路电磁骚扰研究检测领域,通常将直接从芯片上的电路和集成电路封装产生的电磁发射称为辐射骚扰;将由集成电路引脚注入到印制电路板的布线或电缆上的脉冲电流引起的电磁发射称为传导骚扰1。一般芯片上的电路和集成电路封装产生的直接辐射骚扰比由射频电流通过外围电路产生的电磁辐射小得多。从电磁发射的角度来看,电路板上布线与连接电缆构成了电磁发射的天线。

由集成电路内部产生的射频电流,通过引脚和与之相连的PCB 板上的连线向外发射,引脚和连线形成了等效的发射天线,产生了无意发射。向外发射功率的大小可由式(1)来计算:

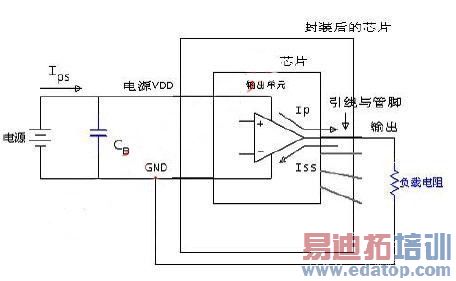

其中Rr为无意发射天线的等效发射阻抗,IRF为IC工作时产生的射频电流。由此可以看出评价集成电路传导骚扰可通过测量集成电路引脚的射频电流来进行。在数字集成电路中,该射频电流是由电路芯片和驱动电路产生的脉冲射频电流。如图(一)是集成电路的电流分布示意图,ZL 为连接输出端口外围电路的等效阻抗,IP 为输出电平由低电平到高电平时的输出电流,ISS 为输出电平由高电平到低电平时的输出电流,ICC 为输出级电路的供电电源的电流。当电路工作时,瞬时脉冲电流一部分从旁路电容CB得到,另一部分来自供电电源IPS。经过旁路电容的电流大小与旁路电容相对于集成电路的放置位置、布线情况、电容的特性有关,即与连接旁路电容的串联阻抗、谐振频率等电容本身的特性有关。通常旁路电容为高频信号提供一个低阻抗回路,这样电流的高频部分由电容来提

供,其余由电源提供形成输出电流。

图(一)数字集成电路的芯片与I/O电路电流分布

可以看出,外围电路的变化会对电流的分布情况产生影响,因而测试应在专门设计的电路板上进行。在确定的电路板上,集成电路的电磁发射的水平,可通过测出的电源端和输出端口电流来描述。

三、集成电路电磁骚扰标准发展状况

目前国际电工委员会制定的有关集成电路电磁发射的标准如表(一)所示:

序号标准名称

1 IEC61967-1 集成电路-电磁发射,150kHz to 1GHz-通用条件与定义

2 IEC61967-2 集成电路-电磁发射,150kHz to 1GHz-TEM 小室法

3 IEC TS61967-3 集成电路-电磁发射,150kHz to 1GHz-表面扫描法

4 IEC61967-4 集成电路-电磁发射,150kHz to 1GHz-1Ω/150Ω直接耦合法

5 IEC61967-5 集成电路-电磁发射,150kHz to 1GHz-工作台法拉第笼法

6 IEC61967-6 集成电路-电磁发射,150kHz to 1GHz-磁场探头法

下面简要介绍几种电磁发射的测试方法。

1、TEM 小室法

TEM小室法是在电磁兼测试中应用较为广泛的TEM小室的基础上建立起来的一种电磁骚扰测量方法。TEM 小室中间的矩形部分开了一个与被测线路板相适应的矩形窗口,用于放置装有被测集成电路的专用评估线路板,该PCB 板的内侧为被测的集成电路,外侧为集成电路的外围电路及辅助设备的连接端子。如果TEM 小室工作频率低于截止频率,只有TEM 模被激发,传递到两同轴负载的功率与被测PCB 板上试品的电流平方成正比,这样通过测试同轴输出端的频谱就能评估线路板上集成电路的电磁发射性能。该方法的缺点是必须制作专用的测试板用于测试,在电路电磁发射源多的情形下测试板对测试结果的影响比较大。

2、表面扫描法

表面扫描法通过测量集成电路表面电场和磁场的方法来描述集成电路的电磁发射特性。该方法的测量频率范围可达10MHz—3GHz,测量采用电场探头或磁场探头按一定顺序扫过集成电路表面,由接收机将相应的测量结果依次传送给计算机处理。测试结果的准确性与电场或磁场探头的特性和探头定位装置的精度有关。该方法可用于探测集成电路芯片上不同部位的电磁发射分布情况,适用于对集成电路的不同设计方案的电磁发射特性的比较。

3、1Ω/150Ω直接耦合法

直接耦合法分为射频电流测试和引脚的射频电压测试两种测试方法。射频电流测试法是在需进行测试的电路中接入一串联电阻为1Ω的电流探头,用频谱仪或接收机测量射频电流流经该电阻时产生的射频电压,所测得的电压应为所有流回到集成电路的射频电流在电流探头上产生电压的总和。射频电压测试法用于测试集成电路的单个引脚或一组引脚上的射频电压,该方法主要用于测试那些准备

连接较长引线输出高频信号的引脚,因为较长的引线更易成为发射电磁波的天线。集成电路的引脚通过标准规定的匹配网络接到测试接收机。由于电流探头和电压探头及网络需设计在线路板上才能进行测试,所以该方法需要设计专用的标准测试板来进行。该方法的具有重复性高的优点,可用于比较不同集成电路的电磁发射特性。

4、工作台法拉第笼法

工作台法拉第笼法的测试在一个长0.5m 宽0.35m 高0.15m的金属屏蔽盒中进行,如图(四)所示。被测试线路板与底部参考地的距离为0.03m,与周围金属面的距离至少为0.06m,测试端口的共模阻抗为150Ω,其它功能连线应经过相应的滤波器并接磁环使其共模阻抗远大于150Ω(频率150kHz 时LCM≥280uH)。其测试布置如图(六)所示。

图(四)工作台法拉第笼法图(五)磁场探头法

工作台法拉第笼法用于评估可在小尺寸的线路板上模拟其独立功能的集成电路。集成电路的电磁发射可在预定的工作条件下进行测量,另外该方法可以直接测量实际应用电路板相同或与实际应用相近的电路板,这就为预测集成电路在实际应用场合的电磁发射情况提供了评估方法,也为在对EMC有强制性要求的集成电路功能模块的电磁发射性能分级提供了测试方法。

该方法来源于IEC61000-4-6,当线路板的电尺寸较小,也就是尺寸≤ , 如在1GHz 频率线路板尺寸小于0.15m 时,连接线路板的电缆成为集成电路的发射天线,电磁发射主要由这些天线产生,相对这些天线,由集成电路本身产生的发射小得多,通常可以忽略。从该方法的原 理可以看出,测试结果中还体现了如下因数的影响:电路板的布线结构;集成电路的去耦措施;电容、电感等分立元

, 如在1GHz 频率线路板尺寸小于0.15m 时,连接线路板的电缆成为集成电路的发射天线,电磁发射主要由这些天线产生,相对这些天线,由集成电路本身产生的发射小得多,通常可以忽略。从该方法的原 理可以看出,测试结果中还体现了如下因数的影响:电路板的布线结构;集成电路的去耦措施;电容、电感等分立元

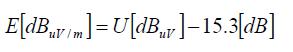

件的高频性能以及集成电路内部不同功能模块工作时的影响。所以用专门制作的标准测试板测试可以比较集成电路EMC性能,而用实际电路板还可以评估实际应用场合所设计的线路板的EMC性能。在共模测试端测得的电压与测试距离为10米时的骚扰场强的关系大致为:

实际场强数值与线路板及引线的结构和长度有很大的关系。

5、磁场探头法

该方法用于测量由集成电路输出到线路板引线上的射频电流引起的电磁辐射,与该激励电流有关的引线、电源层和地层以及与线路板相连的电缆起到了发射天线的作用,产生的场强的大小与该电流成正比。线路板的设计,虚拟天线的发射效率,射频电流的耦合因子等因数也会影响最终场强的大小,而集成电路的射频电流是产生电磁辐射的根源。所以测量集成电路产生的射频电流可作为评价

集成电路、PCB 板及系统EMC特性的一个方法。采用一个微型磁场探头在被测线路(如电源线或I/O线)上的特定位置测量其磁场就可经计算得出被测引线上的电流大小。在该磁场探头放置精确的情况下用这种方法所得的测试结果的可重复性比较高。

我所根据工作台法拉第笼法和磁场探头法建立了两个方法的测试系统,测试仪器采用Agilent公司的频谱分析仪E4440A和26dB的预放大器。 E4440A的频率范围为10Hz—26.5GHz,它的分辨率带宽可从1Hz-8MHz的范围内选择,并具有附合CISPR标准的电磁干扰测试分辨率带宽和峰值、准峰值和平均值检测模式,它还具有MIL-STD-461E标准要求的带宽和检波方式,适合用于电磁骚扰的测试与评估。测量小信号的灵敏度很高,在1Hz时底噪声可达到-160dBm,配上预放大器,即使磁场探头的插入损耗大,也足以检测到较小的干扰信号。为提高测量准确度,系统配备了射频电压校准功能,使仪器的测量误差小于1dB。工作台法拉第笼法和磁场探头法的特点是不仅能测试专用测试电路的电磁兼容性,还可以在实际的应用板上进行测试,可作为不同设计应用方案的性能评估,评价实际应用线路板的电路EMC性能,这样集成电路生产企业与应用集成电路设计产品的工程师都能利用该方法进行检测。由于其体积小,使用方便,可方便EMC设计人员查找产品电路设计、结构布局方面存在的问题,在电路设计改进阶段和产品的整改阶段提供帮助。