- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

多核心运算平台的节能设计

录入:edatop.com 点击:

< 10年前PC处理器从时脉调校转向多核心架构,并藉由制程精进,从记忆体控制器、绘图晶片到周边处理晶片电路单元无所不包,也使系统业者对其电源稳压电路的设计煞费苦心;新世代处理器晶片直接整合高效率变压细胞电路与特殊封装模组,同时藉由不同运算电路之间的独立电压调控,以及更多的节电模式,来跟早已迈向多核心的智慧手机、平板等行动装置,一争功耗效能的王座…

单核心CPU的时脉与节能设计

24年前PC刚问世时,其采用的8086/8088是采用3.3或3.45V标准工作电压设计的16位元处理器。由于处理器功率(p)=介电常数(c)x工作电压(V)的平方x工作频率,也就是处理器设计功率(废热)跟工作频率、工作电压的平方值成正比。

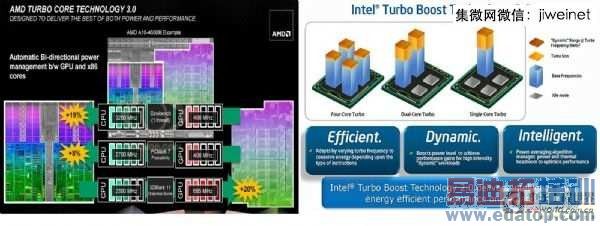

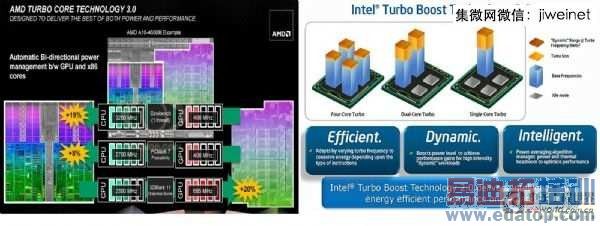

AMD APU、Intel Core i系列处理器,都开发出各针对不同CPU/GPU核心做工作频率/电压动态调校的技术。Source:AMD/Intel

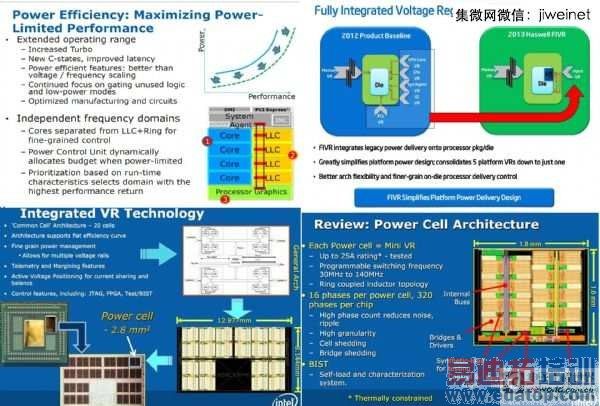

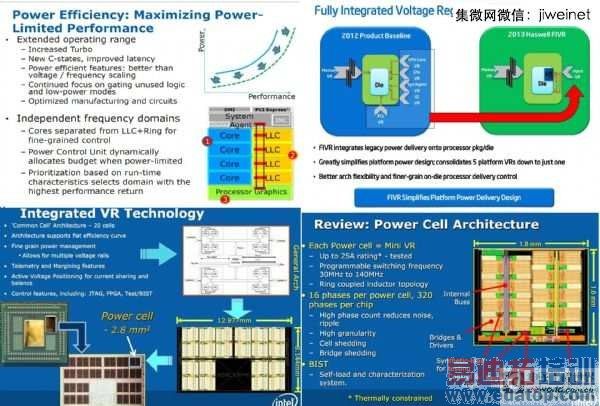

英特尔于22奈米Haswell、14奈米Broadwell处理器内建高性能交换式变压电路,提升各运作电路的独立工作频率/电压调校效能。Source:Intel

在相同制程下,处理器频率提升20%,效能值变为1.13,但热功率会提升为1.73(+73%):反之频率降低20%,效能值减为0.86(86%),但热功率可以降为0.5(50%)。

因此英特尔于1995年Pentium Pro/Pentium MMX时代导入了稳压模组(Voltage Regulator Module;VRM)的规范,藉由定义十几到几十组不同工作频率/电压的阵列组合,让处理器能够因应不同的负载而调低工作频率与工作电压,使整体热功率能维持在一定区间内。

但即便有摩尔定律每2年的制程进化,以一定的矽晶粒面积(成本)下,塞入更多的电晶体、逻辑闸电路来设计、强化处理器的效能,但由于制程进化所缩减的工作电压,仍不足以抵销因为线路微缩造成漏电、工作频率调升所需的电压微调,所造成处理器热功率成等比级数的飞快提升,若不更弦易辙,处理器晶片温度将会直逼太阳表面的温度。

在2003~2004年间,各CPU研发厂商均面临到处理器热功耗/废热提升比效能还快的功耗之墙,也因此各CPU厂不约而同,改以验证过的单一核心,藉助半导体IC制程技术或封装技术,将2颗、4颗以对称方式叠加起来,套前面的公式,2颗各降20%频率的CPU核心叠加起来,总功耗跟1颗全速CPU差不多,但2颗CPU核心搭配双线绪软体全速发挥下,效能值可以提升至1.87(+87%)。等2年制程再进化,可以用一半的功耗,再加倍叠出4核心的处理器,同时维持2年前甚至多年前的热功率,并拥有有较佳的效能/功耗比。因此各CPU厂商纷纷朝向多核心处理器开发,CPU时脉停留在4GHz已有一阵子。

多核心与SoC各功能电路的电压调校

在CPU封装里只有CPU的单纯年代,CPU的电力由独立的VRM电压调整模组供应,VRM在同一时间内仅对CPU输出一种电压,到2008年CPU刚开始内建记忆体控制器时都还是如此。

随着CPU朝向SoC化,从图形处理器(GPU)、影音处理器(Audio Video/DSP)、记忆体控制器等控制电路/单元都整合进来,每个处理单元都有不同工作频率、工作电压与节能需求。新一代高性能微处理器对电源的需求,电源控制IC也从传统的单一类比控制方式,朝向多功能的整合型控制PWM IC发展。

当CPU迈向多核心发展下,像英特尔(Intel)、超微(AMD)纷纷发表像是Intel Turbo Boost、AMD Turbo Core等核心调校技术,依据不同线绪(Thread)的负载,去动态调整各核心的工作频率/电压,以4核心CPU执行到4线绪时,仅各个CPU核心能允许小幅度超频;只用到双核心时,可以针对这2个核心做较大幅度的超频,另外2个核心则降频甚至关闭,当执行像是单线绪游戏类软体时,可以集中在单一核心给予最大的超频幅度,而同时维系整体热功率在一定水准内,可以在执行效能与总体功耗取得较完美的平衡。

而接下来超微(AMD)、英特尔(Intel)也都陆续在处理器晶圆内建热敏电阻感测器,可以随时动态侦测各工作单元/电路的实际运作温度,在一定的总热功率上限下,进一步的依工作负载去调整GPU或CPU的工作电压/频率。

以AMD R-464L APU为例,其CPU核心时脉为2,300MHz,GPU为496MHz,在一般x86与GPU负载均衡下各自时脉不变;当进入多线绪平行处理(Multi-Threaded)的状态,x86时脉会视需要动态拉升到最高39%(3,200MHz),而GPU时脉维持不变;当执行到偏3D图形处理的程式时,x86时脉维持2,300MHz,但GPU时脉动态拉升到最高38%(685MHz)。

Haswell/Broadwell内建高效能变压电路

过去处理器需借助主机板上的变压电路模组(VRM)来供应电压/电流。以22奈米Ivy Bridge平台来说,主机板仍需提供PLL VR 1.8V、Core VR 0~1.2V可变电压、GPU 0~1.2V可变电压、锁相回路(PLL) VR 1V、标准输出入电压(Input/Output) VR 1V、System Agent VR 1V,及DDR3记忆体模组驱动所需的DDR VR 1.2~1.35V,再经过CPU内部的分压输出,受限于电容、电感的延迟效应,而使得各单元的电压调校无法做到极精细。

2013年英特尔技术论坛 (IDF 2013)中,首度揭露22奈米处理器(代号Haswell),在处理器矽晶圆内建全整合式电压调节器(Fully Integrated Voltage Regulator;FIVR),多达20组的16相位电源细胞电路(Power Cell),每个Power Cell工作频率高达140MHz,供电上限25安培,可依据不同的CPU核心、GPU核心、PCI-E、周边I/O等做精细且独立的调整,光CPU本体就能应付到多达320相位,480安培(500A)的总电流量流入;主机板厂商仅需针对 480A 这个规格设计,Haswell/Haswell-E主机板被简化到仅需2个供电回路,一组Vccin对处理器供电,另一组Vddq对记忆体供电即可。

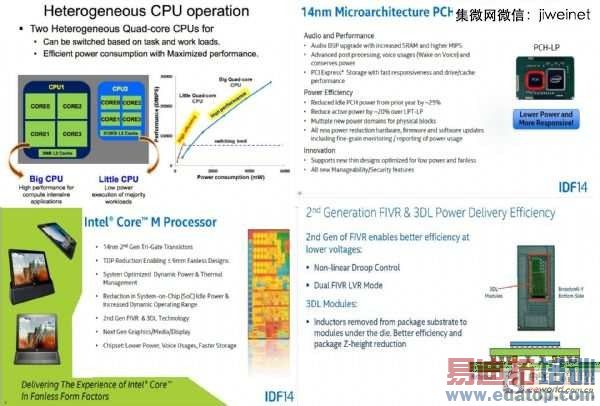

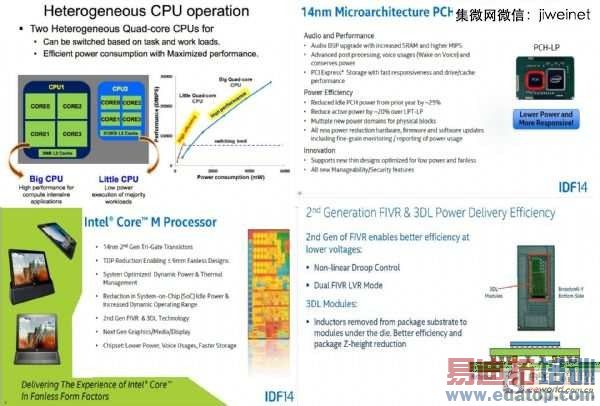

于2014年9月圣荷西举办的秋季IDF2014论坛中,英特尔正式发表采最先进14奈米(14nm)制程打造的行动型处理器Core M (原始代号Broadwell),Core M行动处理器特别针对Detachable、Convertible 2in1变形平板、超极致笔电(Ultrabook)所打造。

Core M采2~4核心设计,内建第4代绘图晶片核心,同时CPU矽晶圆与周边南桥晶片(PCH)采MCP多重晶片构装为一体的SoC设计,整个SoC晶片总设计功耗仅4.5W,可搭配一般散热片或热导管做散热,设计出更纤薄、轻巧且安静的无风扇行动装置(Fanless)。

据传(几乎已获得证实)Intel 将会在2015年14nm的Skylake处理器/主机板平台中,取消FIVR设计重回传统外部分离供电的设计。主机板得重新负责VCCGT、VCCIO、VCCSA等电压的调控,其思考策略为何则不得而知。

行动装置处理器从多核心到异质性的节能设计

从CPU的演进中,单核CPU到了发展瓶颈,同质多核心(Homogenous system)CPU随着核心数量增加到一定程度后,仍面临到功耗、平行化软体与效能无法持续延展的瓶颈。异质性多核心系统(Heterogeneous Systems)则由各种应付不同类型工作负载的异质性核心所组成,藉由颠覆传统的程式码撰写机制,依不同核心特性做运算分派与效能最佳化,可以确保效能持续延展下去。

2012年6月,AMD联合ARM、Imagination、联发科、德仪、三星与高通,成立非营利性的异质系统架构协会(Heterogeneous System Architecture;HSA Foundation),从矽智财(Silicon IP)到软体开发商等产业链的建立,一同推动异质性系统架构的普及。

预计于2014下半年会出现的高阶4核、8核智慧手机,其行动应用处理器人选,有高通(Qualcomm) Snapdragon系列808(6核)/810(8核) 64bit应用处理器,以及联发科(Media)的MT6595(4核)/MT6795(8核)的64bit应用处理器。前者采用安谋(ARM)非对称式(big.LITTLE)-4核Cortex A57加上2~4核Cortex A53设计,后者则直接使用8核心Cortex A53的设计。

过去应用处理器内建电源管理并采共用电压来驱动,当跨入40、32甚至28奈米制程,因CMOS制程/线路微缩,无法以5V工作电压直接驱动;而4核以上处理器,有需要针对每个核心做动态升降频/降压,因此AP业者尝试改以外接的高效能电源管理晶片,提供6组或更多稳压线路与动态电压控制(DVC)功能,可跟处理器负载做适时调整(Adaptive Adjustment),将所有处理工作的电源效率最佳化。

单核心CPU的时脉与节能设计

24年前PC刚问世时,其采用的8086/8088是采用3.3或3.45V标准工作电压设计的16位元处理器。由于处理器功率(p)=介电常数(c)x工作电压(V)的平方x工作频率,也就是处理器设计功率(废热)跟工作频率、工作电压的平方值成正比。

AMD APU、Intel Core i系列处理器,都开发出各针对不同CPU/GPU核心做工作频率/电压动态调校的技术。Source:AMD/Intel

英特尔于22奈米Haswell、14奈米Broadwell处理器内建高性能交换式变压电路,提升各运作电路的独立工作频率/电压调校效能。Source:Intel

在相同制程下,处理器频率提升20%,效能值变为1.13,但热功率会提升为1.73(+73%):反之频率降低20%,效能值减为0.86(86%),但热功率可以降为0.5(50%)。

因此英特尔于1995年Pentium Pro/Pentium MMX时代导入了稳压模组(Voltage Regulator Module;VRM)的规范,藉由定义十几到几十组不同工作频率/电压的阵列组合,让处理器能够因应不同的负载而调低工作频率与工作电压,使整体热功率能维持在一定区间内。

但即便有摩尔定律每2年的制程进化,以一定的矽晶粒面积(成本)下,塞入更多的电晶体、逻辑闸电路来设计、强化处理器的效能,但由于制程进化所缩减的工作电压,仍不足以抵销因为线路微缩造成漏电、工作频率调升所需的电压微调,所造成处理器热功率成等比级数的飞快提升,若不更弦易辙,处理器晶片温度将会直逼太阳表面的温度。

在2003~2004年间,各CPU研发厂商均面临到处理器热功耗/废热提升比效能还快的功耗之墙,也因此各CPU厂不约而同,改以验证过的单一核心,藉助半导体IC制程技术或封装技术,将2颗、4颗以对称方式叠加起来,套前面的公式,2颗各降20%频率的CPU核心叠加起来,总功耗跟1颗全速CPU差不多,但2颗CPU核心搭配双线绪软体全速发挥下,效能值可以提升至1.87(+87%)。等2年制程再进化,可以用一半的功耗,再加倍叠出4核心的处理器,同时维持2年前甚至多年前的热功率,并拥有有较佳的效能/功耗比。因此各CPU厂商纷纷朝向多核心处理器开发,CPU时脉停留在4GHz已有一阵子。

多核心与SoC各功能电路的电压调校

在CPU封装里只有CPU的单纯年代,CPU的电力由独立的VRM电压调整模组供应,VRM在同一时间内仅对CPU输出一种电压,到2008年CPU刚开始内建记忆体控制器时都还是如此。

随着CPU朝向SoC化,从图形处理器(GPU)、影音处理器(Audio Video/DSP)、记忆体控制器等控制电路/单元都整合进来,每个处理单元都有不同工作频率、工作电压与节能需求。新一代高性能微处理器对电源的需求,电源控制IC也从传统的单一类比控制方式,朝向多功能的整合型控制PWM IC发展。

当CPU迈向多核心发展下,像英特尔(Intel)、超微(AMD)纷纷发表像是Intel Turbo Boost、AMD Turbo Core等核心调校技术,依据不同线绪(Thread)的负载,去动态调整各核心的工作频率/电压,以4核心CPU执行到4线绪时,仅各个CPU核心能允许小幅度超频;只用到双核心时,可以针对这2个核心做较大幅度的超频,另外2个核心则降频甚至关闭,当执行像是单线绪游戏类软体时,可以集中在单一核心给予最大的超频幅度,而同时维系整体热功率在一定水准内,可以在执行效能与总体功耗取得较完美的平衡。

而接下来超微(AMD)、英特尔(Intel)也都陆续在处理器晶圆内建热敏电阻感测器,可以随时动态侦测各工作单元/电路的实际运作温度,在一定的总热功率上限下,进一步的依工作负载去调整GPU或CPU的工作电压/频率。

以AMD R-464L APU为例,其CPU核心时脉为2,300MHz,GPU为496MHz,在一般x86与GPU负载均衡下各自时脉不变;当进入多线绪平行处理(Multi-Threaded)的状态,x86时脉会视需要动态拉升到最高39%(3,200MHz),而GPU时脉维持不变;当执行到偏3D图形处理的程式时,x86时脉维持2,300MHz,但GPU时脉动态拉升到最高38%(685MHz)。

Haswell/Broadwell内建高效能变压电路

过去处理器需借助主机板上的变压电路模组(VRM)来供应电压/电流。以22奈米Ivy Bridge平台来说,主机板仍需提供PLL VR 1.8V、Core VR 0~1.2V可变电压、GPU 0~1.2V可变电压、锁相回路(PLL) VR 1V、标准输出入电压(Input/Output) VR 1V、System Agent VR 1V,及DDR3记忆体模组驱动所需的DDR VR 1.2~1.35V,再经过CPU内部的分压输出,受限于电容、电感的延迟效应,而使得各单元的电压调校无法做到极精细。

2013年英特尔技术论坛 (IDF 2013)中,首度揭露22奈米处理器(代号Haswell),在处理器矽晶圆内建全整合式电压调节器(Fully Integrated Voltage Regulator;FIVR),多达20组的16相位电源细胞电路(Power Cell),每个Power Cell工作频率高达140MHz,供电上限25安培,可依据不同的CPU核心、GPU核心、PCI-E、周边I/O等做精细且独立的调整,光CPU本体就能应付到多达320相位,480安培(500A)的总电流量流入;主机板厂商仅需针对 480A 这个规格设计,Haswell/Haswell-E主机板被简化到仅需2个供电回路,一组Vccin对处理器供电,另一组Vddq对记忆体供电即可。

于2014年9月圣荷西举办的秋季IDF2014论坛中,英特尔正式发表采最先进14奈米(14nm)制程打造的行动型处理器Core M (原始代号Broadwell),Core M行动处理器特别针对Detachable、Convertible 2in1变形平板、超极致笔电(Ultrabook)所打造。

Core M采2~4核心设计,内建第4代绘图晶片核心,同时CPU矽晶圆与周边南桥晶片(PCH)采MCP多重晶片构装为一体的SoC设计,整个SoC晶片总设计功耗仅4.5W,可搭配一般散热片或热导管做散热,设计出更纤薄、轻巧且安静的无风扇行动装置(Fanless)。

据传(几乎已获得证实)Intel 将会在2015年14nm的Skylake处理器/主机板平台中,取消FIVR设计重回传统外部分离供电的设计。主机板得重新负责VCCGT、VCCIO、VCCSA等电压的调控,其思考策略为何则不得而知。

行动装置处理器从多核心到异质性的节能设计

从CPU的演进中,单核CPU到了发展瓶颈,同质多核心(Homogenous system)CPU随着核心数量增加到一定程度后,仍面临到功耗、平行化软体与效能无法持续延展的瓶颈。异质性多核心系统(Heterogeneous Systems)则由各种应付不同类型工作负载的异质性核心所组成,藉由颠覆传统的程式码撰写机制,依不同核心特性做运算分派与效能最佳化,可以确保效能持续延展下去。

2012年6月,AMD联合ARM、Imagination、联发科、德仪、三星与高通,成立非营利性的异质系统架构协会(Heterogeneous System Architecture;HSA Foundation),从矽智财(Silicon IP)到软体开发商等产业链的建立,一同推动异质性系统架构的普及。

预计于2014下半年会出现的高阶4核、8核智慧手机,其行动应用处理器人选,有高通(Qualcomm) Snapdragon系列808(6核)/810(8核) 64bit应用处理器,以及联发科(Media)的MT6595(4核)/MT6795(8核)的64bit应用处理器。前者采用安谋(ARM)非对称式(big.LITTLE)-4核Cortex A57加上2~4核Cortex A53设计,后者则直接使用8核心Cortex A53的设计。

过去应用处理器内建电源管理并采共用电压来驱动,当跨入40、32甚至28奈米制程,因CMOS制程/线路微缩,无法以5V工作电压直接驱动;而4核以上处理器,有需要针对每个核心做动态升降频/降压,因此AP业者尝试改以外接的高效能电源管理晶片,提供6组或更多稳压线路与动态电压控制(DVC)功能,可跟处理器负载做适时调整(Adaptive Adjustment),将所有处理工作的电源效率最佳化。