- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Cortex-A12架构深入解析

《ARM世界之旅(一):特殊的生存之道》一文中,我们详细解读了ARM的授权模式经营之道,理解了这家英国小公司是如何生存、壮大的。今天我们再转向技术方面,重点看看新宣布的Cortex-A12究竟是怎么回事儿。

【Cortex-A架构体系】

在消费级产品领域(台式机、笔记本、平板机、智能手机),Intel有两套架构,一是2008年引入的高性能和主流级别Core(酷睿),二就是低功耗的Atom(凌动)。

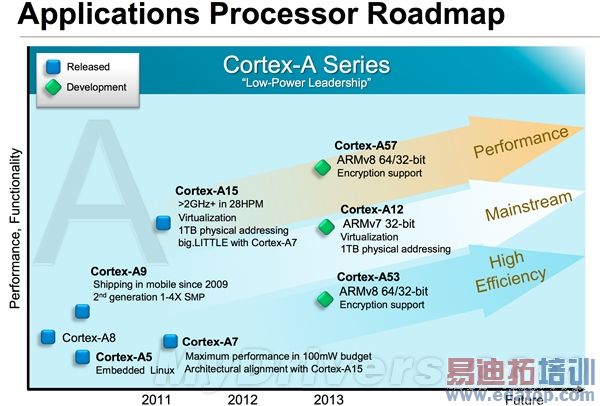

ARM则有三套架构,分别是高端的Cortex-A15、主流的Cortex-A9、低功耗高能效的Cortex-A7。Intel的超低压版Core Y系列、Atom可以说分别对应前两者,但是面对A7,Intel还没有可以竞争的方案。

(ARM其实还有Cortex-R系列嵌入式、Cortex-M系列微控制器方案,但不在本文讨论范围内。)

很显然,ARM在移动领域已经有了完整的布局,Intel则正努力将桌面和笔记本那一套拿过来。

A15、A7一高一低,可以组成big.LITTLE联合方案,但是要注意,A15并不是用来取代A9的,而在很长的一段时间内,A9并没有真正的后继者。

A15、A7未来将会分别被64位ARMv8架构的A57、A53所取代,A9呢?它的后代在哪里呢?这就是最近宣布的:Cortex-A12。

A12将会和A57、A53形成新一代的“三驾马车”,但在架构上它其实还是32位的ARMv8,跟其它两位并不一样(这个后边详述)。

(注意横轴时间线不是产品上市时间,而是IP授权时间)

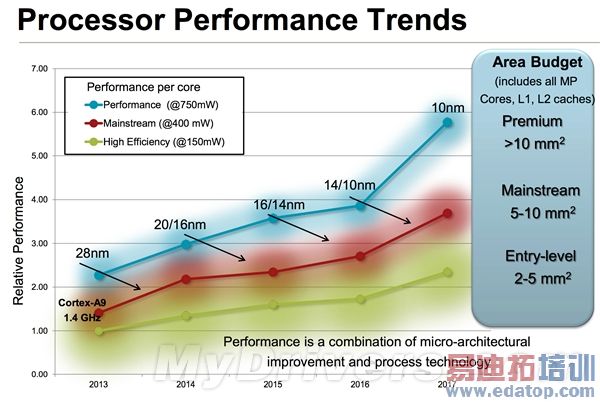

说起处理器的性能、功耗,除了依赖架构之外,生产工艺也是关键所在。当前的主流是28nm,接下来还会有20nm、16/14nm、10nm……

尤其是对于A15来说,28nm已经无法在提供足够性能的同时将功耗控制在合理水平,这也正是bit.LITTLE诞生的理由之一。如果过渡到20nm,A15的情况无疑会好很多。

当然,对于移动GPU也是同样的道理,比如Imagination PowerVR 6系列宣布了那么久还停留在纸面上,除了开发周期之外最重要的原因就是当前工艺伺候不了它,而根据与台积电的合作,16nm才会是PowerVR 6系列的理想着陆点。

【A12架构纵览、前端设计】

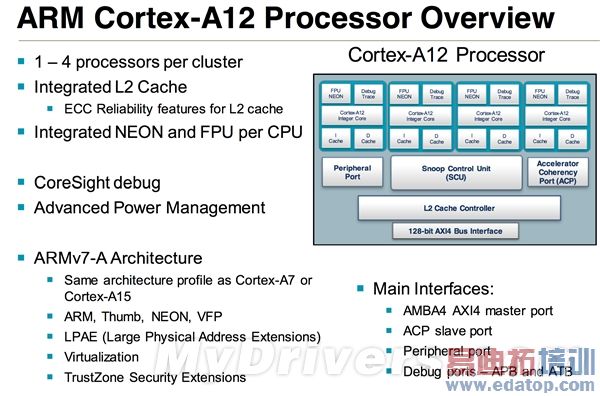

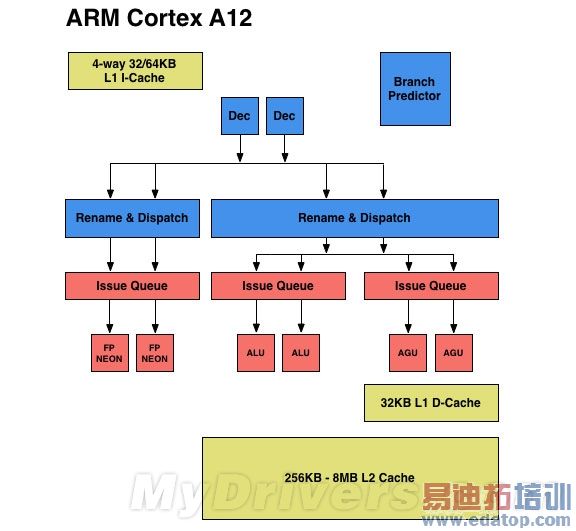

从高端层面讲,A12是双发射、乱序执行架构,整数流水线10-12级(A9 8-11级),整合二级缓存和载入/存储、浮点、NEON单元(标准配置而非可选),每个群簇支持最多四核心,也可以多个群簇并联,组成八核心、十二核心……

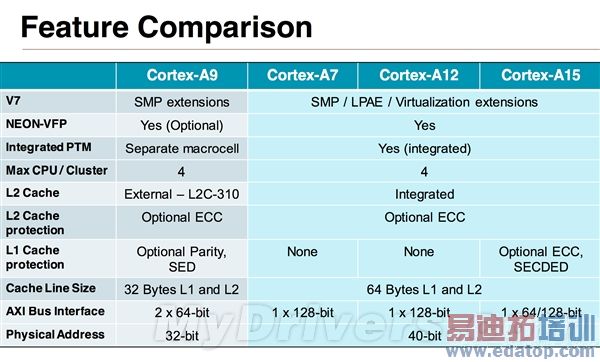

从指令集架构兼容性上讲,A12、A7、A15是一家的,都是32位的ARM-v7A,均支持40位物理寻址(最大容量1TB)、128-bit AXI4总线界面、虚拟化、整合缓存。

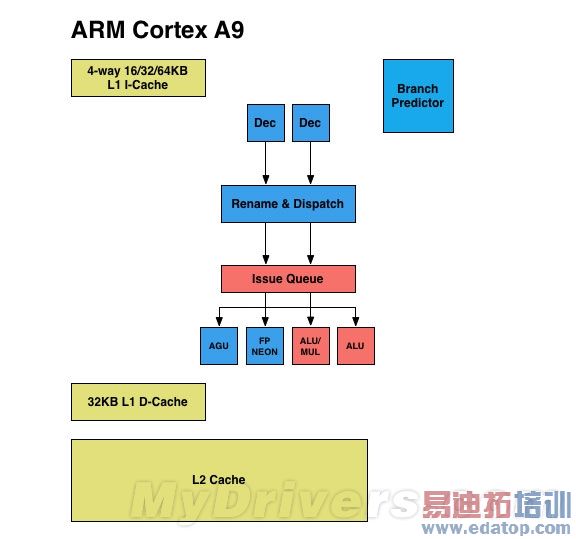

相比之下,A9支持的是32位物理寻址,2×64-bit AXI4总线,外置缓存,NEON单元也是可选的。

Cortex-A12架构纵览

尤其值得一提的是二级缓存,A9上是外置的,需要操作系统单独支持,A12则和A15/A7一样完全整合,为所有核心共享,并有自己独立的电压和频率层,不过如果需要,后者也可以和CPU同步。

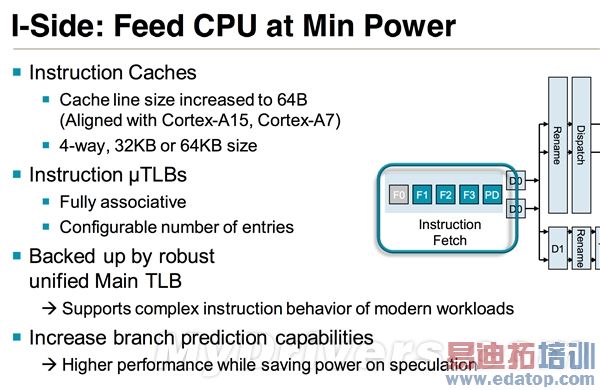

一级缓存是四路关联,容量可选32KB、64KB,同时缓存数据线(cache line)也翻番为64Byte,以便更好地和DDR内存控制器对齐。

值得一提的是,A12最终也会支持big.LITTLE,同样能够搭配A7,但是目前的初始版本还不行,缺乏必需的一致性界面。

A9、A12/A7/A15架构特性对比

分支预测器比A9有了很大改进,可以大大改进能效、性能,不过在A12设计之初,ARM对其性能估计不足,直到大约三个月前才意识到错误,但此时时间紧迫,ARM必须做出选择:是照常发布这个低效率的设计,还是迅速寻找替换一个更合适的分支预测器?

A12团队最终选择了A53里的分支预测器,拉过来塞给A12,并做了一些细微的针对性调整。

【A12后端设计】

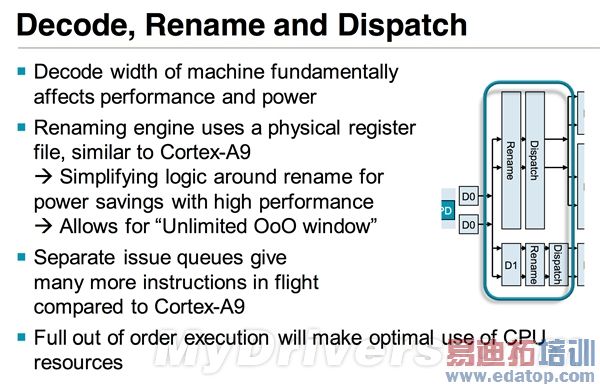

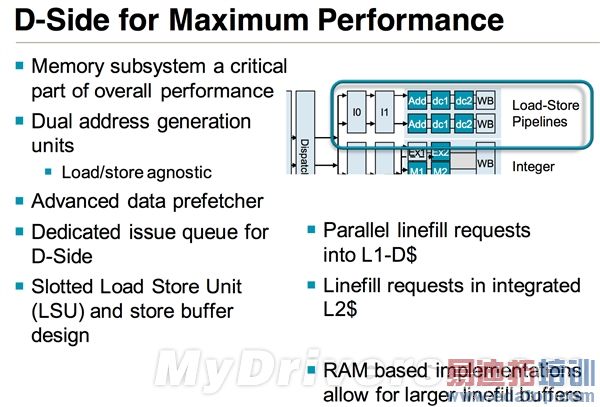

A12的前端虽然比A9效率更高,但真正的性能提升来自于核心内部的执行。类似A15,A12在功能单元之前引入了多个独立的发射队列。

指令解码进入微操作,重命名指令分派进入发射队列,然后微操作在操作数可用的时候从发射队列中发射出来。这一切都依赖于发射队列的正确顺序处理,A12是可以乱序执行的(绝大部分情况下)。

A9只有一个发射队列,只能处理4个解码指令;A12增加到了三个队列,每个都比A9里更大。仅此一点就能大大提升IPC。

这三个发射队列分别是:整数、FP/NEON、载入/存储。

下边就是A12、A9的简单架构对比图,其中蓝色部分是顺序执行的,粉色/黄色则是乱序执行的。很显然,A12仍然只是部分乱序架构,只不过比A9“更乱”而已。

Cortex-A12

Cortex-A9

A12保留了A9中的两条整数流水线,但是和A7/A15一样加入了对整数除法的支持,A系列其它架构都没有这一点,不过除此之外整数流水线没啥变化。

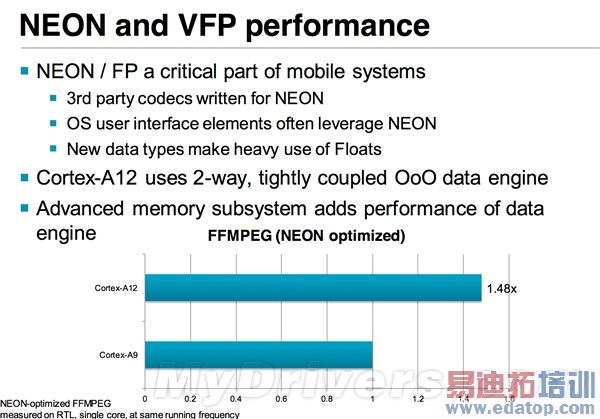

FP/NEON单元的改进非常大。A9刚发布的时候,NEON代码很少能用到,这也正是NVIDIA Tegra 2去掉了它的主要原因,不过现在情况不同了,Android和移动应用对NEON的支持已经很好了。

A12仍然是整数和浮点操作的物理寄存器文件相分离,但是比A9里更大了。

A9中的浮点和NEON指令都是顺序执行的,A12将它们改成了完全乱序,至少在非内存操作上如此。FP/NEON发射队列是双发射的,分成两个流水线,都可以完全乱序操作,配合也很紧密,可以在浮点和整数单元之间快速转移数据。

AGU单元也变成了两个,对应两条流水线,而且也成了完全乱序的。

【提升40%?A12性能、未来展望】

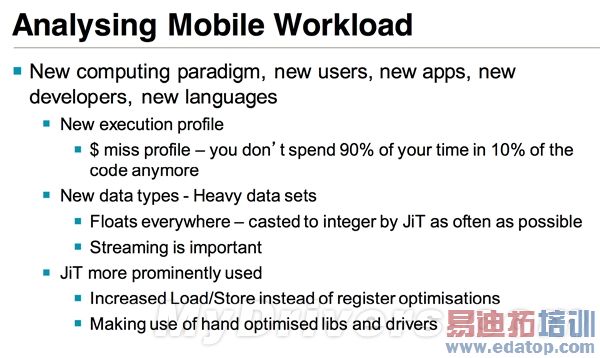

A9架构诞生于2009年,当时智能手机才刚刚起步,而这几年的巨变让很多东西都完全变了,比如FP/NEON指令大大增加了,内存访问频率更高了,应用性能要求更高了,A9在浮点、内存方面的缺陷就暴露了出来。

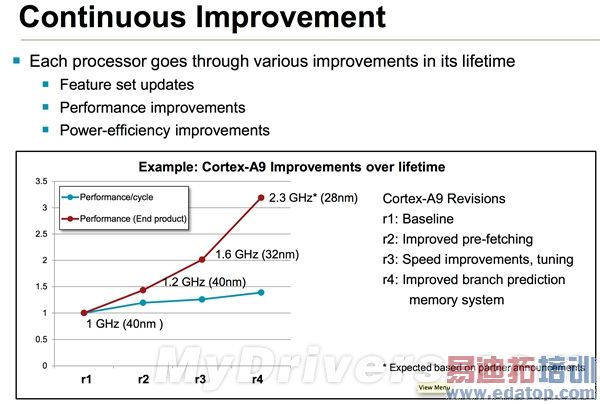

为此,A9架构这几年来也在不断改进,先后衍生了四个版本:最初的r1版对应40nm工艺,主频最高1GHz;r2版改进了预取部分,工艺不变主频可达1.2GHz;r3版来到了32nm工艺,配合改进与调校,频率也升至1.6GHz;最新的r4版由改进了薄弱的分支预测和内存系统,会用在28nm上,主频有望高达2.3GHz。

不过,这些细微的调整并不能掩盖A9本质上的劣势。这,就是A12要弥补的。

ARM虽然也声称A9是乱序执行架构,但其实仅限整数部分,浮点和内存操作都是顺序的。A12则变成了一个几乎完全乱序的结构,各处设计也都有了改进。未来几年,A9仍将继续辅以并深挖潜力,但是很显然,A12会有更好的性能、更高的能效。

在同样的频率下,ARM宣称A12的性能可比A9提升40%,比如照ARM的说法,FP/NEON的改进能让FFMPEG负载下同频率性能提升48%!当然实际应用中肯定没这么多。

能效和内核面积的改进更有趣。ARM声称使用同样的制造工艺,A12的内核面积估计会比A9大最多40%,但能效可与A9持平或者更好。

A12 IP在几周前才刚刚最终定案,目前已经对外提供授权。按照以往的开发周期惯例,第一款芯片将在大约一年后诞生,第一款设备则可能要2014年底或者2015年初。这段时间就是A9发挥余热的最后时刻。

不过,移动市场发展这么快,两年后还需要A12么?特别是还有高通的Krait 300的定位就很类似。或许还是那句话,没有很差的产品,只有不合理的定价。如果能比骁龙600系列便宜很多,A12一样会很吸引人。

最后提一句,ARM表示会继续改进优化A15的功耗问题。