- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Intel瞄准智能机开发0.28V x86处理器

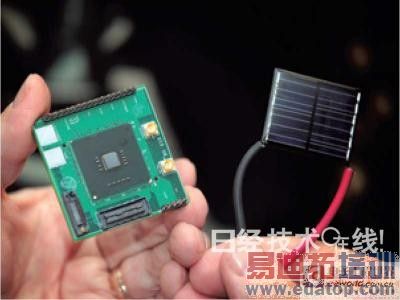

利用小太阳能电池也能运行的x86处理器

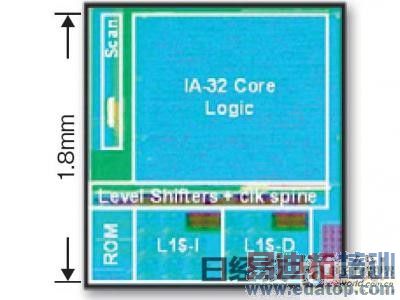

美国英特尔开发出了以0.28V~1.2V的大范围电源电压驱动的x86处理器“Claremont”(图1)。技术详情已经在2012年2月举行的半导体国际学会“ISSCC 2012”上发布。英特尔开发出了在极低电源电压下也能准确无误地进行逻辑运算的专用单元库,使该处理器得以实现。开发工作主要在英特尔的印度研发基地进行,由于Claremont是作为相当于Pentium的老式CPU内核封装的,因此难以直接产品化,不过此次开发的电路技术似乎可以用于该公司面向智能手机和平板终端的SoC产品。

Claremont在0.28V电压下工作时的耗电量为2mW,工作频率为3MHz。采用32nm工艺CMOS技术制造,电路面积为2mm2,晶体管数量为600万个。需要高处理性能时,可以利用通常的电源电压驱动。例如,电源电压为1.2V时,工作频率为915MHz,耗电量为737mW。

通过FPU的动态开/关和电路实现

该处理器主要是通过两方面的改进实现的。一个方面是动态开/关浮点运算单元(FPU)的电源。即对CPU内核执行的命令进行监控,在FPU没有运算命令时切断FPU部分的电源。FPU在CPU内核中占逻辑电路面积的20%,所以这一改进可大幅削减耗电量。

另一方面是面向低电压工作开发了专用标准单元库。一般情况下,如果降低数字电路的电源电压,晶体管的导通/截止比就会下降,工艺偏差的影响会相对变大,因此难以维持正常的逻辑运算。这种倾向在复杂的逻辑门电路中尤为显著,所以此次从标准单元中去除了这种逻辑门。

比如,组合电路方面,去除了4段以上的堆栈构造逻辑门,以及采用传输门的4输入以上多路复用器。与3段构造和3输入相比,4段逻辑门与4输入多路复用器的正规延迟时间的偏差分别增加了108%和127%。另外,宽度不到制造技术容许的最小宽度2倍的小规模逻辑门由于对工艺偏差的耐性低,也被去掉了。

图1:英特尔公司的x86处理器“Claremont”

电路面积为2mm2,晶体管数量为600万个。采用32nm工艺CMOS技术制造。

触发器也有所改进

除了组合电路,Claremont中还改进了顺序电路。改进之处是扩大了顺序电路内的反馈路径。另外,主从型触发器方面,将普通传输门类型换成了时钟逆变器类型,这是因为传输门虽然面积小,但难以在低电压下工作。缓存存储元件方面,采用了由10个晶体管构成的单元,与由8个晶体管构成的单元相比,电源电压可降低0.25V。

时序分析方面,在0.5V、0.75V和1.05V三种电源电压下分析了角点条件。结果证实,在0.5V的角点条件下获得了充分的时序性能。在1.05V的角点条件下能以650MHz工作。面向1.05V的标准单元方面,虽然漏电流和电路面积较小,但低电压时的处理性能较差,因此采用了面向0.5V的标准单元。

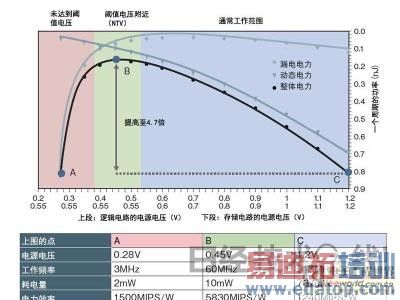

电力效率方面,在电源电压为0.45V,接近阈值电压时最高,为5830MIPS/W(图2)。原因是,虽然降低电源电压后动态电能会减少,但漏电损失的电能激增。

三星采用基板偏压技术

在ISSCC 2012上,韩国三星电子也发布了用于智能手机等的低耗电量技术。即配备ARM公司CPU内核“Cortex-A9”的应用处理器“Exynos”技术。该公司没有公布芯片面积和晶体管数量等,不过表示采用32nm工艺CMOS技术制造,工作频率为1.5GHz(图3)。在CPU内核、GPU、DRAM控制器和其他部分共计4处设置了电源域。

图2:电力效率在接近阈值电压时最高

与以1.2V的电源电压工作时比较,以接近阈值电压的电压驱动时,电力效率提高至4.7倍。存储器电路的最小电源电压为0.55V。

图3:三星的应用处理器“Exynos”

采用32nm工艺CMOS技术制造。采用双核或四核构成。

三星首次在Exynos采用的32nm工艺制造技术中导入了基板偏压技术。通过在LSI的硅基板上加载偏压,可以改变晶体管通道附近的电场,动态控制阈值电压。这样就能够根据处理负荷提高晶体管的性能,并降低漏电流。应用处理器领域的应用方面,美国德州仪器的OMAP系列,以及更早的美国Transmeta公司的x86处理器“Efficeon”中,都采用了基板偏压技术。

基板偏压技术有两种方式:一种是在基板部分加载正电压以降低晶体管阈值电压,从而暂时提高速度的“Forward-Body-Biasing(FBB)”;另一种是在基板部分加载负电压以提高阈值电压,从而暂时抑制漏电流的“Backward-Body-Biasing(BBB)”。三星的Exynos中同时采用了这两种方式。该公司没有公布加载的偏压,不过表示采用FBB时性能提高了13.5%。

估计三星承担了美国苹果公司应用处理器“A5”的制造,所以此次的基板偏压技术除了Exynos外,还有可能用于苹果公司的处理器。