- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Android处理器的高速化和低耗电量化

录入:edatop.com 点击:

正在发表演讲的松本(点击放大)

在2011年12月13日~12月15日举行的“2011冬季款智能手机&平板终端”研讨会上,日本TOP Systems代表董事社长松本佑教发表了演讲。TOP Systems是一家风险公司,主要开发可抑制工作频率、通过并行处理提高性能的多核型微处理器。在此次演讲中,松本佑教介绍了Android终端用应用处理器的高速化和低耗电量化现状,并对未来发展趋势进行了展望。以下为此次演讲的要点。

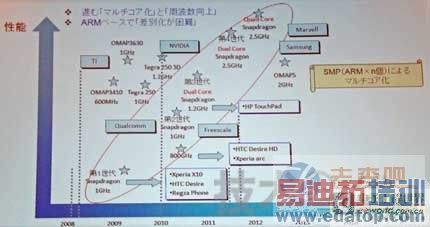

目前,Android终端占据智能手机市场(按照台数计算)的1/2左右,其中配备的是美国高通的“Snapdragon”(参阅本站报道1)、美国德州仪器的“OMAP”以及美国英伟达的“Tegra”(参阅本站报道2)等处理器。这些处理器的共同特点是基于ARM,属于多核型。CPU的工作频率超过1GHz已经成为主流。

Android用处理器的开发动向

(摘自松本的演讲资料)(点击放大)

多核化取得进展的理由主要有以下三个。

(1)ILP的壁垒:在单核中,1时钟可同时执行的指令数量为3~4,在ILP(Instruction-Level Parallelism:指令级并行性)上存在限制。

(2)存储器的壁垒:在处理器频率不断提高的同时,存储器频率却只有几十MHz左右。为了弥补这个缺口,需要在处理器侧配备缓存。

(3)耗电量的壁垒:智能手机用处理器目前的耗电量为1~1.5W左右,如果将频率提高至2倍,那么耗电量也会增至3W左右,因此必须在不增大频率的情况下提高性能。

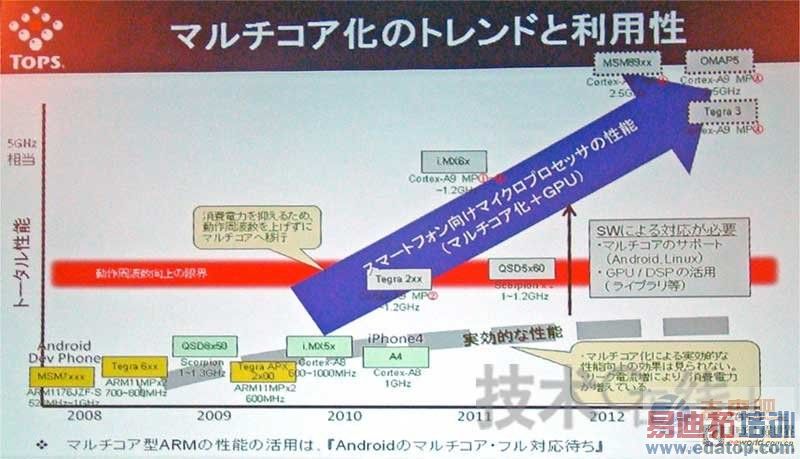

多核化的趋势和可利用性

(摘自松本的演讲资料)(点击放大)

利用率的壁垒

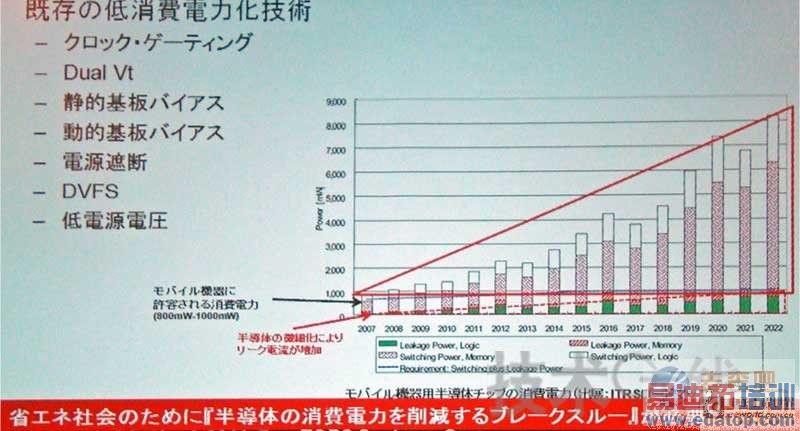

但是,多核化带来的实际性能的提高,还停留在远远低于理论值的水平上。多核化未能在提高性能上发挥效用的主要原因是,随着半导体的微细化,同时运转的晶体管比例呈指数下降。另外,原来半导体耗电量一直随着微细化而降低,但是90nm工艺以后由于漏电流的增大,反而出现了耗电量增大的情况。随着微细化的发展,今后还需考虑在Android用处理器上采用效率更高的晶体管。

便携终端用半导体的耗电量走势图

(摘自松本的演讲资料)(点击放大)

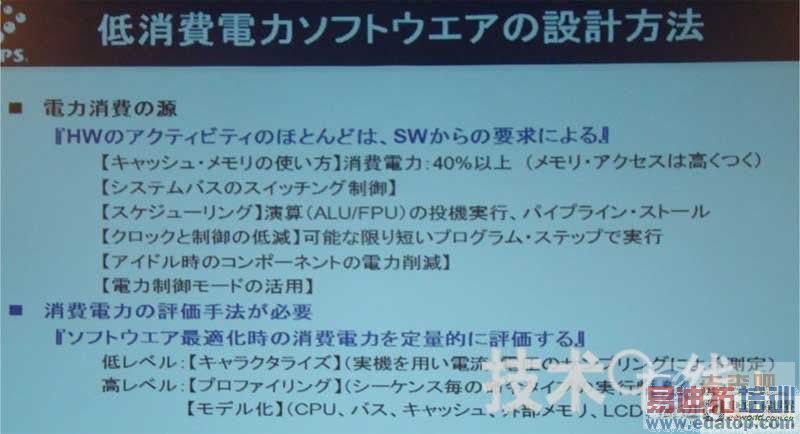

此前在开发软件时并不太重视耗电量,而实际上硬件几乎都是按照软件的要求工作的。因此,可以考虑采用通过软件来减少硬件耗电量的各种方法,比如利用缓存(存储器访问的耗电量较大)、控制系统总线的开关以及进行调度等(参照下图)。所以性能和电力的可视化,以及硬件和软件的协同设计等,将成为新一代Android终端开发的关键。(记者:赤坂 麻实,Tech-On!)

低耗电量软件的设计方法

(摘自松本的演讲资料)(点击放大)

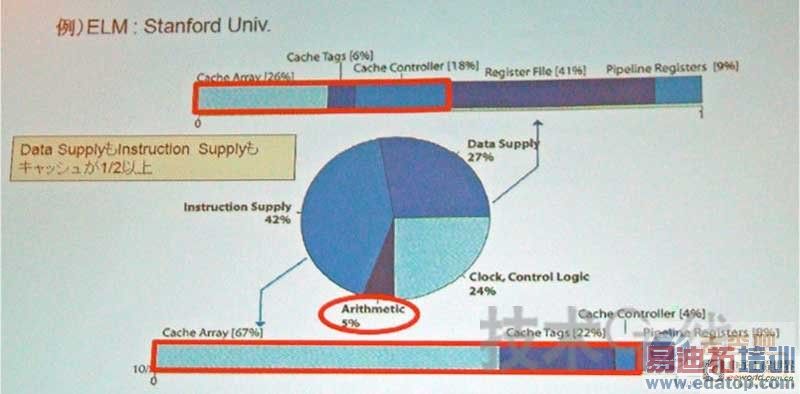

耗电量的可视化。微处理器的耗电量分布图