- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

MAX9489/MAX9493: 集成时钟发生器方案

MAX9489/MAX9493是多输出时钟发生器,MAX9489设计用于SOHO路由器和网络设备, MAX9493用于机顶盒和数字电视。与典型的“本地”时钟方案相比,集中时钟发生器能够为多端口、多模块应用提供更多的优势。

使用多输出时钟发生器时需要考虑一些实际问题,这里给出的指导方针有助于改善集中时钟源的设计,尽可能消除对信号的不良影响,排除噪声干扰,降低系统成本。本文利用原理框图说明这些应用。

集中时钟源的应用优势

现有的网络路由器/交换机系统必须支持越来越多的连接端口和模块,每个端口或模块一般都需要一个参考时钟,这个时钟通常由与端口或模块相关的本地晶体或晶体振荡器提供。随着端口数或模块数的增多,参考时钟的成本也会提高。而且,这种本地时钟方案使得系统重新配置参考时钟以便进行测试非常困难,也不适合接口的电源管理和端口(或模块)升级或降级。这也正是机顶盒和数字电视所面临的设计挑战。

集中时钟发生器并不是一个新概念,它已广泛用于PC 机主板。例如,在机顶盒设计中,存在11个以上的不同接口或模块,这些接口或模块需要不同的时钟。MAX9489或MAX9493能够产生路由器和机顶盒所需要的全部时钟,而不需要提供本地参考时钟。利用一个诸如MAX9489和MAX9493的集成多输出时钟发生器,可以节省系统成本、提高设计对系统的控制能力。

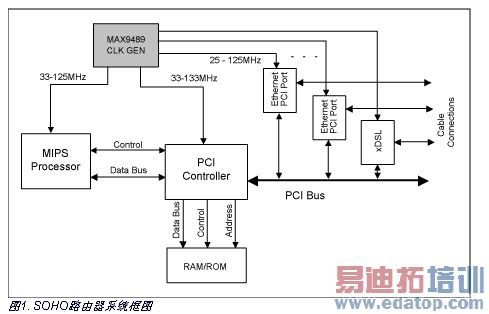

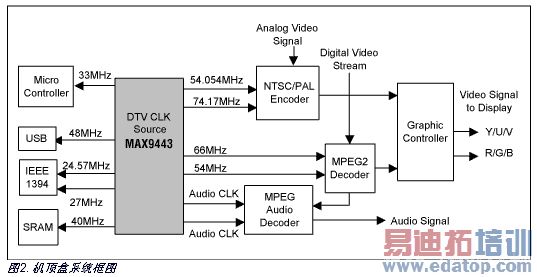

MAX9489提供15路LVCMOS可编程时钟输出,每路时钟具有10种不同的频率选择,适用于以太网、PCI、存储器和 MCU。MAX9493有11路时钟输出,为视频、音频、USB、IEEE1394、MCU和存储器提供时钟。在MAX9489和MAX9493中,每路时钟可通过I2C接口单独控制。另外,MAX9489的时钟输出频率可以上、下调节5%或10%,方便了系统的过驱动和欠驱动测试。为了降低EMI,我们在MAX9493中还集成了扩频和摆率控制功能。图1和图2分别给出了MAX9489在路由器中的应用框图和MAX9493在机顶盒中的应用框图。

电路板设计

使用集成的时钟发生器进行设计时,如何在不降低信号完整性的前提下解决时钟的跨电路板连接是所面临的一个设计难题。通常,时钟引线的长度在3英寸到9英寸之间,对于这样的引线长度,按照主板的设计原则,LVCMOS信号最高可以工作在150MHz。但是,必须仔细考虑电路板布局。需要解决两个实际问题:必须减少较长的PCB引线对上升/下降时间造成的影响,另外,还要排除同一电路板上其它信号源的噪声干扰问题。

降低对信号的影响

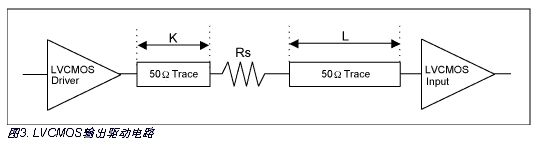

为了降低对信号上升/下降时间的影响,常常采用50引线,并在CLK输出引脚和引线之间插入一个25至33的电阻(Rs)。 已知驱动器的上拉和下拉晶体管阻抗约为20, 插入Rs能够使LVCMOS驱动器的总输出阻抗匹配于50引线。驱动器电路原理图如图3所示。

表1给出了K和L的长度。

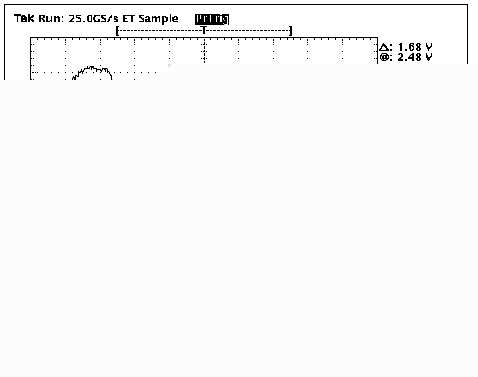

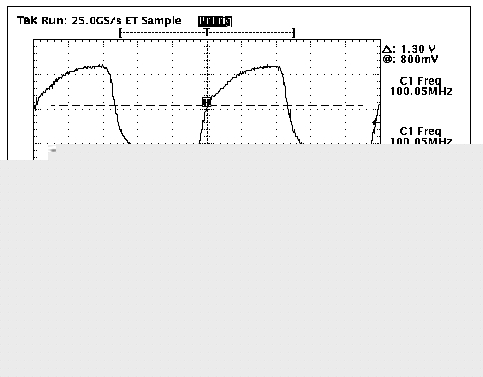

电阻Rs应该通过K英寸引线连接到LVCMOS输出引脚。K和Rs的最佳值可通过试验或仿真确定。这些数值是驱动器输出阻抗、引线阻抗和长度的函数,还与实际元件、终端阻抗有关。如果输出引脚到终端的距离少于2英寸,则不必使用Rs。当时钟频率高于100MHz时, 应该进一步减少时钟引线长度。为了说明匹配引线能够提供更好的信号完整性,我们用MAX9489产生一路100MHz的时钟,并将其连接到一段5英寸长的 50引线上。图4给出了在引线不同位置测试的波形。

如图4至图6所示,通过在适当位置增加Rs,有效改善了信号完整性。

?

?

避免噪声干扰

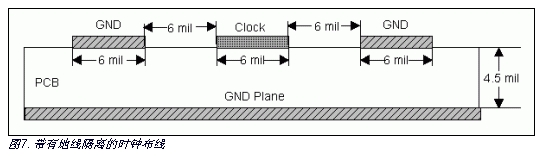

为了解决噪声干扰的第二个实际问题,我们需要减少时钟与其它信号之间的相互干扰。时钟引线最好夹在地线之间,如图7所示。

评估板和I2C编程可以申请MAX9489和MAX9493评估板。如果系统中没有I2C总线,请向Maxim索取I2C编程接口板,接口板带有ID (型号),MAXSMBus。