- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

省电设计使DDS更适合便携应用

直接数字频率合成器(DDS)已获得广泛应用,这是由于其快速的频率切换速度和调制能力。但是,在低功耗和低成本作为关键因素的情况下,对模拟锁相环(PLL)合成器是有利的,DDS则往往降为第二位的选择。然而,ADI公司的AD9913型号在125MHz输出带宽范围内提供了DDS技术的快速切换和调制灵活性,并具有类似PLL大约只有50mW的低功耗。

DDS解决方案的功耗一直以来都很高。例如,当型号为AD9850的第一款集成数字-模拟转换器(DAC)的DDS产品在20世纪90年代中期出现时,它在50MHz的输出带宽下功耗为380mW。体现在AD9913中的创新造就了相对AD9850而言,在功耗与带宽关系之间20X的提升。

AD9913为便携式和/或仪表应用带来了三个关键的好处。较低的50mW功耗让设计师能够在掌上电脑和其它便携式应用中利用DDS的优势。可编程模数结构对网络时钟和仪表应用是一个具吸引力的功能。它使得频率合成可以是采样速率的任意有理(两个整数之比)分数。当分母是2的倍数时,传统的DDS只能合成采样率的有理分数,如1/4和5/16,而AD9913并不局限于2倍数的约束。它可以产生的输出信号是采样率的任意有理分数,如1/10、3/7或286/11487(只要它们属于AD9913的编程范围之内)。最后,像该公司早前的某些DDS产品一样,AD9913提供了极为灵活的波形产生。

AD9913的低功耗是通过几种省电创新来实现的。第一个问题涉及到DDS基于正弦和/或余弦函数通过相位累加器将产生的瞬时相位值转换为振幅值。传统上,只读存储器(ROM)查找表来实现这项任务。不过,随着DDS技术发展到更高的速度和更大的复杂性,ROM方式的功耗负担变得令人望而却步。这导致采用专利的角旋转算法,该算法依靠计算引擎来实现正弦和/或余弦转换。角旋转算法的方式可以追溯到AD9850型DDS,并且发现其相对ROM查找表法而言可显著降低功耗。许多早期不采用角旋转算法的DDS产品会需要特殊的热封装来配合增加的功耗。此外,在该公司现有的DDS产品中,热考量可能迫使许多宝贵的特点被去除(例如,DDS输出信号的数字相位和/或频率调制、数字滤波来减轻sin(x)/x损耗、用于多通道应用的多DDS内核)。

在降低功耗方面的下一个重大突破可以归功于该公司专利的相位交叉DDS结构。早期降低功率是通过角旋转算法,使得在同一芯片上运行多个DDS内核成为可能。结果发现,在较低的采样速率运行多个DDS内核,比在非常高的采样率下运行单个DDS内核的功耗要低。这是一个重大的突破,因为高分辨率(14b或更高)、高采样率(1GHz或更高)的数字-模拟转换器(DAC)内核需要在DDS技术上创新,以便充分利用这些新的DAC内核。交叉DDS架构能让设计师把多份已低功耗的DDS内核副本合并,并在比高频率DAC内核更低的采样速率下操作它们。随着过渡到180-nm CMOS制造工艺,这种新的创新架构导致了DDS输出带宽的急剧增加,但相对前一代低频DDS产品而言仅有适中的功耗。

然而,即使有了这些创新,在手持设备和便携式应用中功耗仍是极大的。为了缩小这种差距,另一个创新是必要的。随着新的专利变异角度旋转算法的出现,进一步降低了DDS内核的功耗。新的算法结合了关注低功率操作的设计理念,使设计师能够达到预期的低功耗设计目标。新的理念包括了当不需要特定的操作模式时,关闭所有无关的内部时钟,以及从每块电路削减功耗,只要不降低频谱性能或过分限制带宽。

其成果就是AD9913,它工作在采样率达250MHz,但只有50mW的功耗。250MHz的采样率产生了大约100MHz的可用带宽。结合了低功耗的输出频率能力,使得AD9913对广范的射频控制器件以及条形码无线扫描器和射频识别(RFID)标签而言,成为极具吸引力的候选者。但是,对于要求高于100MHz的应用而言,必须采用辅助PLL来实现上变频。其他便携/手持应用可以低功耗DDS技术中获益,这包括了软件定义无线电(SDR)、遥控或便携式有线电视测试设备、医疗葡萄糖计、无线火灾报警器,以及电子测量设备,例如频谱分析仪和波形发生器等。

独特的结构

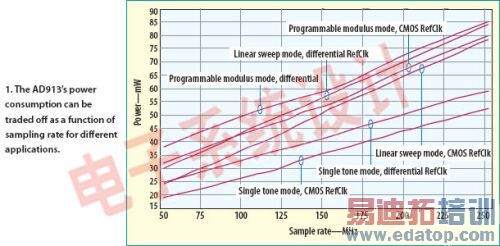

图1表示了当工作在100MHz的标称输出频率时,AD9913的低功耗特性。该图表明了三种不同的工作模式(单音、线性扫描、可编程模数),具有直接接收差分或单端源(屏蔽内部PLL)驱动的REFCLK输入。

AD9913的可编程模式结构是独一无二的,并且其与常规DDS器件有着区别。传统的DDS依靠相位累加器实现其频率分辨率,累加器的大小(位数)决定了DDS的频率分辨率。

有C-bit分辨率相位累加器的传统DDS将提供fS/2C的频率分辨率,其中fS是DDS的采样率。数字调谐字M可以是从零到2C-1}-1的任何整数。技术上,允许从2C-1至2C-1的调谐字,但这导致了奈奎斯特镜像频率合成(例如,计数旋转相量)。该数字调谐字和DDS采样率(fS)产生了通常的DDS频率合成方程,其中fO是DDS的输出频率:

fO/fS=M/2C (1)

因为M必须是整数,对于任何给定的采样率,传统的DDS只能合成2C-1的特定频率。也就是说,对于M=0,输出频率是零(DC),而对M=2C-1-1,输出频率略低于0.5fs。所有剩余的输出频率受限于fs2C(DDS的频率分辨率)的增加。在大多数情况下,这种精细的频率分辨率更令人满意。例如,对AD9913,其拥有32-b累加器,频率分辨率是(250MHz)/232,即约为0.058Hz。

现在,考虑具有32-b累加器的传统DDS,其准确合成采样速率1/1000th的输出频率。这意味着fO/fS=1/1000。将其带入公式1的左侧,并求解M为:M=232/1000,或M=4294967.296,其中M显然不是一个整数。传统DDS要求M为一个整数值,在这个例子中其最接近的值是4294967。困难在于,使用这种调谐字不能准确合成0.001fs的频率,大约为0.000999999931fs。在某些应用中,这种与理想频率略有偏差是不可接受的(例如网络时钟应用)。