- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

平台式存储器控制器的考量及实作

近年来手持装置日渐普遍,体积小且具备高运算能力的装置,已是必然的潮流。为了满足多媒体应用日渐增多,手持装置的容量需求亦随之增加,因此设计高效率的存储器控制器(Memory Controller;MC)来控制大量资料的存取,将是必然趋势,而平台式设计方法(Platform Based Design Methodology)是目前最普遍也最有效率的设计流程。

本文拟以在AMBA-Based的设计平台上,针对平台式存储器控制器的设计,就系统架构面以及应用需求面来考量,做一详尽的介绍及分析。

近年随着各式各样的资讯产品问世,SoC的设计理念已促使平台式设计方法的兴起,平台设计的关键想法就在于重复使用的观念,它颠覆了以往方式,是为了特殊需求而去设计的单一特定电路(ASIC Design)。

所谓平台式设计方法的诉求在于能够提供产品更快速的上市时间。然而,另一方面,由于是在既定的平台上进行开发,产品差异化的程度也将受到侷限,因此在开发平台上所使用的IP,就需考量到设计的弹性。将IP延伸做参数化的设计(Configurable IP),使得IP能在平台上根据不同的需求,透过参数的调整控制,便能重复被使用,缩减设计的时间。

此外,一个完整可行的设计平台必须包含微处理器(MPU)或提高运算效能的数字信号处理器(DSP)架构,并提供预先验証过的软件和硬件、编辑器、EDA以及建立软件工具使用流程(Tool Chain)等等。

因此,在本文中将探讨设计符合平台式存储器控制器IP所需考量到的一些情况,如系统对存储器频宽的需求、匯流排(BUS)上的MASTER(如MPU、DSP、DMA 等)对存储器存取的仲裁原则(Arbitration Rule)、存取资料延迟的解决方式以及参数调整的弹性等等。

在探讨存储器控制器IP的设计考量之前,先介绍存储器的种类及用途。存储器可分为两大类,一是静态式存储器(Static Memory),另一是动态式存储器(Dynamic Memory)。静态式存储器的分类大抵可分为SRAM、ROM、Flash等,而动态式存储器则有DRAM、SDRAM、DDR以及DDR-II 等。静态式存储器与动态式存储器的差别,在于动态式存储器需透过预充电(Precharge)及更新(Refresh)的方式才能将资料储存,而静态式存储器的资料储存具有非挥发性(Non-Volatile),不会因断电而造成资料的遗失。

一个完整的平台式架构设计会使用哪些种类的静态存储器以及动态存储器,将会在第二节里就这部分逐一说明;第三节会就设计存储器控制器IP时,讨论在系统架构面及应用需求面的考量及分析;第四节则探讨利用现有完整的平台对IP进行验证,而完整的平台则会使用工研院晶片中心所开发的PAC Main Board[1]。最后,会对未来存储器的使用趋势以及存储器控制器的设计取向做一结语。

存储器类型的选择及考量

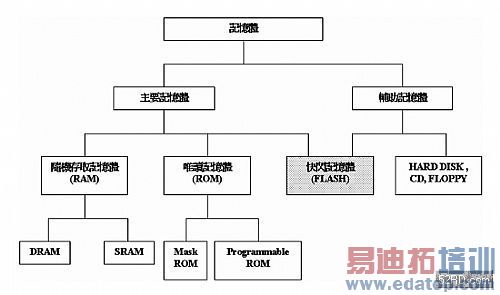

存储器主要功能是为了要储存资料及程式,分为主要存储器与辅助存储器两类,如(图一)所示。主要存储器通常是由半导体元件构成,资料的存取速度较快,用于置放执行的程式或即将取用的资料。而辅助存储器的单位成本低且具有大量储存空间,例如硬碟、光碟等,这些装置存取速度较慢但可储存大量资料,一些非急迫性的程式资料都可存放于此,但执行程式时要先将程式从辅助存储器搬到主存储器才能执行。本章节将探讨各类存储器,并评估较符合系统需求的存储器。

(图一) 存储器分类图

■静态存储器

静态存储器包含唯读的ROM、可程式化的ROM、静态随机存取存储器(SRAM)以及快闪存储器(Flash)。一完整的平台需要有初始的程式(Boot Code),以初始化系统周边的设定,完成后才能载入OS Kernel,而初始程式就可放在ROM或是Flash里。当平台上有新加入或移除的周边,则需修改初始程式,修改完之后透过烧录的方式将初始程式重置于ROM或是Flash里。ROM与Flash的主要用途是以读为主,两者的资料写入时间较长,不适合用于大量资料的存取。

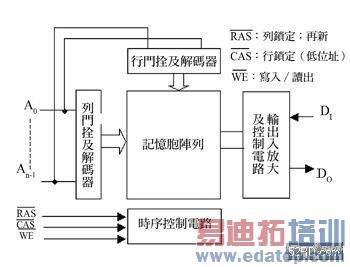

静态随机存取存储器由于存取速度快,常被运用于系统中的快取存储器(Cached Memory),由于SRAM 中一位元的储存细胞元(Memory Cell)需使用四个电晶体,如(图二)所示,非常佔用面积,消耗功率的情形也较为严重,所以系统上採用的SRAM 大小也就特别受到限制。

(图二) 静态存储器储存细胞元读/写控制电路

SRAM一般都被运用于微处理器或DSP中当作Instruction Memory、Data Memory或LocalMemory来满足一些即时高速的运算。

■动态存储器

动态存储器所指的也就是动态随机存取存储器,储存一位元的资料只需要一电容,当列解码线(RAS)与行解码线(CAS)动作时,可令MOSFET接通允许电容电压被读取或写入。由于电容的电压储存时有漏电现象或传输时的耗损,除了在写入与读出时都经过放大之外,每一列的所有位元经过一段时间就必须将资料读出后再写入一次,这个工作称为DRAM的更新,(图三)为动态随机存取存储器的存取控制。

DRAM最大的优势是容量大,约为SRAM的四倍,不但省电又比SRAM便宜,但DRAM需重复更新以及预充电的设计,导致使用上的不方便,也影响到存取的时间,因此从使用效率上来看也就比不上SRAM。

(图三) 动态随机存取存储器的存取架构

由于DRAM的预充电时间限制了它的存取速度,这个天生的障碍很难改善分散资料的随机存取时间。但是对于猝发模式(Burst Mode)的存取,却可预知下一笔资料的位址,因此有了SDRAM(Synchronous DRAM)的问世。SDRAM利用交叉记忆模组(Interleaved Memory Module)及多重管线化(Multi-Pipeline)的技术,改善了DRAM在猝发模式下的存取时间,在连续存取存储器中可达到与外部时脉同步存取的效率,但对第一笔资料存取时间的延迟仍无法改善。

■选择合适的存储器

在考量到微处理器及DSP运算处理速度需要有高速的储存装置搭配,SRAM也就势必得在平台架构中使用;而储存启动系统之初始程式的存储器,则以可烧入式的ROM或Flash为考量。

在选取动态随机存取存储器方面,以市面上的产品种类来说,则有更多的选择,有一般标准的SDRAM、Mobile SDRAM(Cellular SDRAM)、Pseudo SRAM、DDR、Mobile DDR以及DDR-II等,可以考量平台的低功率设计或效能来选择适当的SDRAM。目前市面上开发成熟的手持式产品,为了增加待机时间而使用的低功率设计,大部分皆採用Mobile SDRAM、Mobile DDR;若是以效能为主的准系统,则会选择以DDR、DDR-II为主。因此,在存储器选择上仍要以实际应用的需求为主要考量。

设计存储器控制器IP的考量与分析

接下来,就存储器控制IP在设计过程中可能遇到的问题,以及如何解决问题或找出更好的答案,来做讨论。分析此设计主要分两个方向来说明,一是系统架构面,另一是应用需求面,以求能使存储器的存取效率达到最快。

■系统架构面之考量

在一完整的平台架构中,可能存在着一些造成存储器存取速度不佳的情况,而这些问题大致整理如下:

(1)在单层匯流排(Single Layer Bus)上同时有多个MASTER上来对存储器做存取的情况;

(2)当存取时间成为主要瓶颈时,该如何克服;

(3)若平台为多层匯流排架构(Multi-Layer Bus)时,如何安排不同层间的MASTER 对存储器做存取,而不同层的MASTER又同时对存储器发出要求存取的动作;

(4)设计的IP若因平台上有不同模组移除或加入,在不影响设计时间的情况下,该如何做调整。

首先,要解决上述第一个问题,一般在BUS上都会有一些仲裁原则来决定谁先取得BUS的使用权,则谁先就可先对存储器做存取,而仲裁原则有一般最常见的如Round-Robin、Fixed Priority或Priority programmed by register等[2]。而问题二的情况大部分发生在一些随机的读或写相间隔错置,若能在某一段的时间间隔里,在不影响到资料相依性的情况下,去对这些读写指令做有效的排程(Scheduling),让读与写的动作能集中在最合适的组合下完成读写,如此一来就能将读写的延迟情况降低许多。

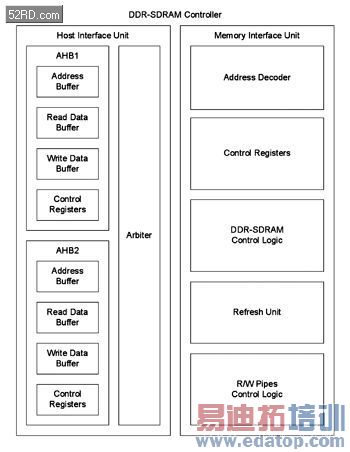

在问题三的情况中,可以透过增加传接埠(Access Port)的方式来实现[2],如(图四)所示为Dual-Port的SDRAM MC,但在选用存储器时则需考量存储器是否也具有Dual-Port access的能力,且存储器控制器IP也须有仲裁原则(如同问题一的解决方式)来决定由哪一个MASTER可以对存储器进行存取。

(图四) Dual-Port的DDR SDRAM MC

在问题四的情况中,可以透过参数化(configurable)的设计[2],经由修改暂存器内部的值做来Enable/Disable 模组中的一些功能模组,而这也是SoC设计所提倡的中心思想,让IP不断地被重复利用,发挥最大的效益。

■应用需求面之考量

首先,从目前最热门的多媒体应用H.264来看,其资料处理量相当大,如Motion Estimation或Texture Coding等。这些大资料的运算及搬移,在某一段时间域里会有很高的机会再次被使用到,因此在存储器控制器IP中加入读/写缓冲区(R/W Data Buffer),让之前被读出或写入的资料重复被利用,若下一次读写的资料在读/写缓冲区中命中(Hit),则可省下资料读取或写入所花的延迟时间;但如果发生在缓冲区找不到资料时(Miss),则就是这次读写所多花的一段时间延迟(Miss Penalty)。

H.264的运算处理多以MB(Macro Block)为单位,若能将这些MB中的资料及一些资讯在存储器写入时做适当的位置安排,使得需要从存储器读出资料时,能以最快的方式连续将资料一併送出。

然而,若此设计能满足多媒体的应用,却往往可能影响到存储器控制器IP设计的弹性;若用在网路或无线通信的领域上,则用途可能受到侷限,甚至可能得重新设计新的架构。

存储器控制器IP的验证环境

在讨论完设计IP所需考量的情况之后,接着探讨在完成IP设计之后,要如何验证IP,而接下来介绍的环境将会以工研院晶片中心所开发的PAC Main Board为主[4],并搭配一些ARM的CM(Core Module)及LT(Logic Tile)Module,并以ARM 环境中的软件来验证。

■工作站的模拟及测试

首先,在工作站的环境中,将设计的IP加入存储器的Behavior Model一起做模拟,确认基本的读写动作是否正确。之后使用nLint将IP重新再编译过,将逻辑上或一些可能会发生错误的情况排除,再进行下一步骤做合成,完成后产生NetList File,再回到之前的步骤重新做一次模拟,而此次模拟若能完成通过,则此IP的初步验证就算完成。

接下来,将IP整合进ARM所提供的VIP(Verification IP)环境中,这是一个完整的AMBA-Based平台,可供设计者将自行设计的IP整合进这平台中,对自己的IP做验证,若能完成测试,则可保证这个IP是AMBA Compliance(符合ARM AMBA BUS Protocol),适用于ARM所提供的环境中。

之后可在PC端,利用ARM所开发的ADS(ARM Development Suit)撰写C code,经编译过后成为Binary File,将此Binary File放到ARM的EASY下去实际模拟,若结果正确并与C code符合,如此一来,这IP在工作站的验证算是初步完成。

■Board-Level 的模拟及测试

再来,将设计的IP经由FCII做FPGA的合成,根据PAC Main Board所选用的FPGA Device来合成。合成完之后,需将产生的edf File加入平台架构中,再透过Xilinx的ISE做P&R,P&R完成之后就将产生的BIT File透过ARM的Multi-ICE将此架构下载至PAC Main Board的FPGA里,如(图五)所示。

(图五) PAC Main Board

(图六) PAC Main Board Demo

接下来透过Firmware来驱动PAC MainBoard,透过撰写好的Machine Code来测试是否能完成一些应用,如MP3的拨放或解压缩JPEG的图片等,如(图六)所示,就是一个JPEG 的范例。

结语

目前在设计存储器控制器IP的领域中,有Denali的Databahn Memory Solutions[3]、Synopsys的Designware[4]以及ARM的PrimeCell[5],这些公司所开发的存储器控制器IP产生器(Generator),透过一些参数的设定以及选项的勾选之后,便可产生一个满足使用者需求的IP,如此一来,IP的产生以及运用更具有弹性。透过IP 的产生器来辅助完成设计,能简化设计平台式架构的流程,且在短时间内就能透过所产生的IP,来验证架构的可行性,但缺点是这些IP产生器的授权需耗费较大的成本,在技术不受限于人的情况下,自行设计开发也就是另一途径。

由于目前市面上的存储器制造技术日益更新,目前的主流已是DDR及DDR-II,但由于存储器的产品週期极短,也造成存储器控制器IP设计的风险。因此,存储器控制器IP在设计时,需考虑到未来新一代存储器产品的修改弹性,尽量透过参数化的方式,使其能有重复利用的机会,以求快速整合到不同的平台架构上,达到最快速的SoC设计方式。(作者任职于工研院系统晶片中心系统晶片整合技术组/多媒体设计课)

上一篇:提升可携式装置锂电池充电效率

下一篇:如何对锂离子电池进行高效率的充电(三)