- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

模拟电路设计(十六)增幅电路的噪音对策(下)

模拟电路设计(十五)增幅电路的噪音对策(上)中,我们探讨了真性噪音的定义、特性与处理噪音的Level。接下来,我们将更进一步地探讨构成真性噪音的原因以及如何处理OP增幅电路的噪音。

构成真性噪音的各种噪音

(一).热噪音

a.如何决定电路噪音的下限

热噪音主要是电阻内部的热扰乱(Braun运动)造成,换言之任何消费能量的物体都会产生热噪音,电路的最低噪音Level取决于热噪音大小。

电阻R(Ω)内部产生的热噪音vT(VRMS),理论上可以用下列Nikesto定理表示:

vr:Voltsman定数 。

k:绝对温度(1.38Х10-23J/K) 。

T:噪音频宽(K) 。

fB:噪音频宽(Hz) 。

根据式(4)可知降低热噪音有下列三种方法分别是:

①降低阻抗值。

②降低温度。

③减少电路的频宽。

b.常温状态、R=1kΩ,fB=1Hz时,热噪音电压密度为4nVRMS

噪音电压密度vND可用下式表示:

换言之等价噪音频宽乘上噪音电压密度vND,就可以获得噪音电vT(VRMS),值得注意的是式(5)为定量计算,因此常温状态、R=1kΩ,fB=1Hz时,热噪音电压密度为4nVRMS,建议读者谙记以上数据,使用上相当方便。

c.热噪音Level的计算方法

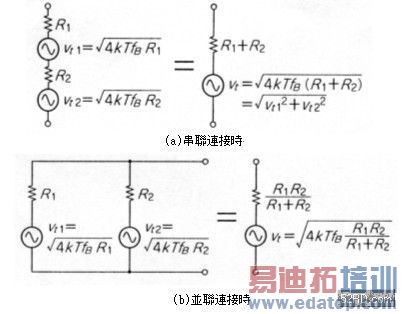

图7是有关热噪音的各种计算方法。由于热噪音Level是阻抗值是电阻值造成因此必需先计算合成阻抗,再将该阻抗值代入式(4)才能求得热噪音。

此外开放电路的阻抗值为无限大,因此一般会认为噪音也是无限大,然而实际上如式(6)所示噪音Level,取决于浮游容量而不是阻抗。

图7 与电阻整合的热噪音计算方法

(二).半导体内部的shot噪音

a.IDC=1mA,fB=1Hz时,shot噪音为18pA

shot噪音是与跨越半导体内部电位能阶的电流有关的噪音,反过来说无电位能阶的导体与电阻等电子元件,理论上就不会发生shot噪音。

假设通过电晶体或是二极管PN接合部位的平均电流为IDC(A),噪音的实效噪音电流I5k(ARMS)可用下式表示:

q:电子的电荷(1.59Х10-19C) 。

fB:噪音频宽(Hz)。

式(7)又称为「shot key定理」。噪讯电流密度

虽然式(8)还称不上是热噪音,不过经常应用于定量计算。根据经验显示IDC=1mA,fB=1Hz时,shot杂讯为18pA,建议读者不妨谙记以上数据,使用上相当方便。

b.如何降低与电路性能的trade off

下列方法可以有效降低shot噪音:

①降低PN接合部位的平均电流。

②使用PN接合部位平均电流较低的FET。

③减少电路的频宽。

有关第①项,如果降低电流等价性阻抗会变大,热噪讯则相对提高;有关第②项,使用FET会使Gain降低,为补偿Gain因此电路需作特殊设计,这种方法另一项缺点是会牺牲其它特性。

由此可知降低shot噪音有一定的限度,因此必需透过实际测试才能具体决定shot噪音的最低值。

(三).接触噪音

a.数十Hz以下的频率为支配性噪音源

接触噪音主要原因是材料之间的接触不完全,导致导电率发生变动所致,例如开关(switch)、继电器(relay)、连接器(connector),或是电晶体等半导体元件、电阻等被动元件,銲接不完全时就会发生接触噪音。接触噪音与频率呈反比增加,因此接触噪音又称为「1/f 噪音」。

接触噪音与接触部位流动的电流平均值IDC(A)呈比例增加,单位频宽的实效噪音电流可用下式表示:

IF:实效噪音电流 。

K:材料与形状构成的比例定数。

f0:设计者需求的频率(Hz)。

fB:以f0为中心的噪音频宽(Hz) 。

虽然式中的K为未知数,不过一般IFD在数十Hz以下时,会变成具有支配性的要因。

b.如何降低接触噪音

①使用金属皮膜电阻

在被动元件中噪音最大,而且使用数量最也是最多的电子元件是碳素皮膜电阻,由于碳素皮膜的微细缺陷,极易造成接触不完全等问题;相较之下卷线电阻具有最低噪音的特徵,不过它的频率特性与阻抗值范围非常狭窄,因此只适合特殊用途使用。金属皮膜电阻具有较低的噪音特性而已比较实用,因此低噪音的增幅电路大多使用金属皮膜电阻。

②低频领域降低Gain,或是选用低噪音的的OP增幅器

使用在数十Hz以下的信号,具备1/f支配性而且不需增幅的交流增幅电路,或是需要增幅成直流的增幅电路等场合时,建议读者尽量选用低 的OP增幅器。

(四).分配噪音源

a.高频波为支配性的噪音源

两个电极例如电流分配到base与collector时就会发生噪音,该噪音称为「分配噪音源」,一般而言高频波属实支配性的噪音源。

分配噪音的实效噪音电流Idiv(ARMS)单位频宽值 ,在频率f0<fT时:

f0:设计者需求的频率(Hz)。

hfe(fo):f0的电流增幅率。

IB:电晶体的emitter电流。

q:电子的电荷量。

fB:噪音频宽(Hz)。

fT:使|hfe(fo)|变成1的频率(Hz)。

由式(10)可知一旦变成高频波,hfe(fo)会大幅降低,分配噪音则相对增加。

b.如何降低分配噪音

下列方法可以有效降低分配噪音:

①使用无分配电流的unipolar元件,例如FET等等。

②尽量使用大fT的bipolar电晶体。

需注意的是以上元件的低频噪音都非常大,所以使用上必需作全面性衡量。

OP增幅电路的噪音

(一).如何计算OP增幅IC的噪音

a.利用data sheet的计算方法

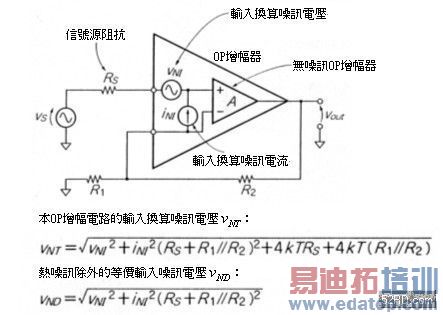

使用OP增幅IC构成的增幅电路,它的输出噪音Level同样是由各种因素造成,而且原因错综复杂,因此计算OP增幅IC的噪音时,经常使用图8所示的等价电路,因为图8的电路是将OP增幅IC当作是由无噪音的OP增幅器,以及已经input至输入端的噪音电压源与噪音电流源所构成。

图8 与电阻整合的热噪音计算方法

b.从data sheet获得各噪音源的参数

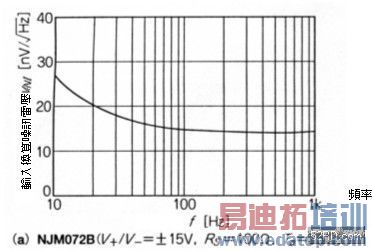

一般厂商公布的噪音电压源与噪音电流源的的资料大多是代表值,例如OP增幅IC NJM072B的输入偏压(bias)电流几乎是零,因此厂商公佈的资料中并无噪音电流参数。OP增幅器有输入偏压电流的场合,通常厂商会公佈信号阻抗造成的噪音特性。图9是厂商公布的data sheet记载的噪音特性实例。

此外高精度OP增幅器经常使用造成1/f噪音问题的低频直流频率范围,因此data sheet会记载有关1/f噪音的Level,不过必需注意的是NJMOP-07在0.1Hz~10Hz频率范围,会产生最大0.65µVp-p的1/f噪音。

图9 实际OP增幅IC的噪音特性

(二).计算值与实测值的比较

a.制作两个OP增幅器进行实验

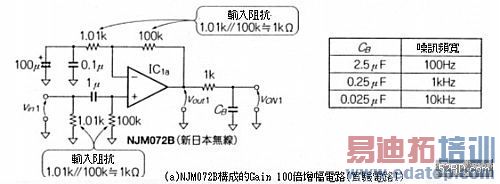

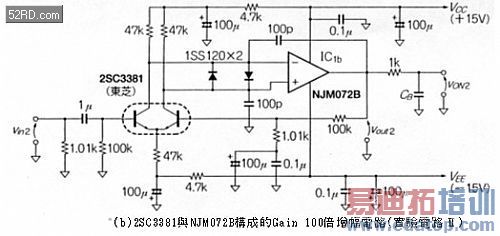

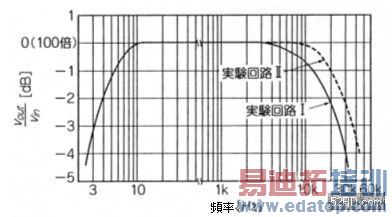

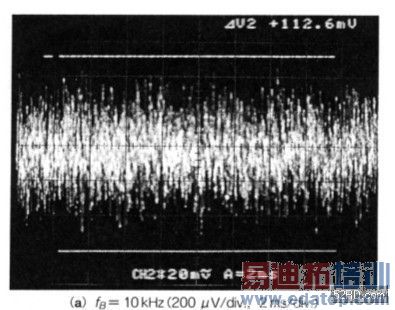

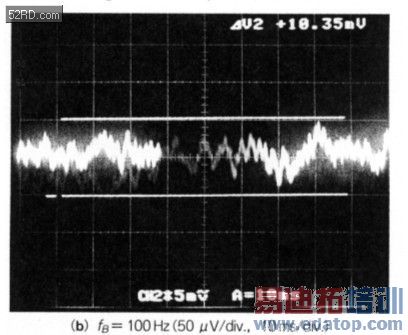

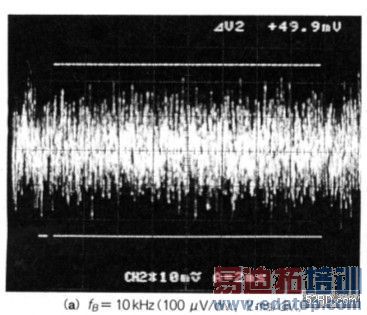

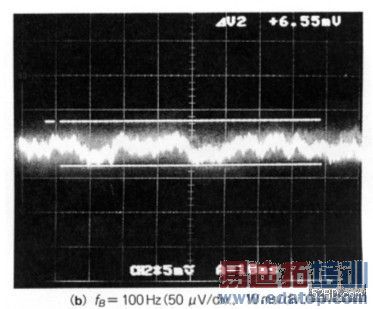

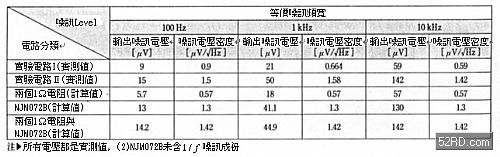

如图10所示制作两个OP增幅器,测试它的输出噪音。图10(a)是使用NJM072B Gain为100倍的增幅电路;图10(b)的NJM072B前段追加设置2SC3381构成的差动增幅电路,形成Gain为100倍的增幅电路。必需一提的是上述差动增幅电路并未作最佳化设计。图11是上述两实验电路的频率特性;表3是实验电路的输出噪音电压与输出噪音电压密度的实测结果;照片1与照片2是上述两实验电路的输出噪音波形。

图10 为确认data sheet记载的噪音特性的实验电路

图11 两实验电路的频率特性

图11 实验电路I的输出噪音波形

图12 实验电路Ⅱ的输出噪音波形

接着利用两个1Ω的电阻计算实验电路Ⅱ,以及NJM072B的噪音电压作比较,根据比较结果显示只要加大等价噪音的频宽,上述两者就无差异,换句话说厂商公佈的资料具有很高的可信度。

值得一提的是利用两个1Ω计算电阻NJM072B获得的噪音电压值,几乎可以忽略1/f噪音的存在,由于它并非单纯的加算而是向量总合,因此可以利用图4(a)中的公式计算。

b.与低噪音电晶体组合可获得低噪音效果

由表3的比较结果可知,等价噪音频宽相同的场合,若在OP增幅IC追加设置低噪音电晶体,输出噪音电压可以降低一半以下,换句话说需要作低噪音化设计时,使用低噪音电晶体可以获得很好的低噪音效果,该结论非常值得设计者参考、使用。

表3 图10的实验电路输出噪音电压与输出噪音电压密度比较

(三).OP增幅电路的低噪音化设计技巧

a.使用能与热噪音匹配的OP增幅IC

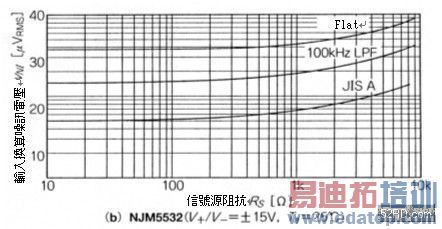

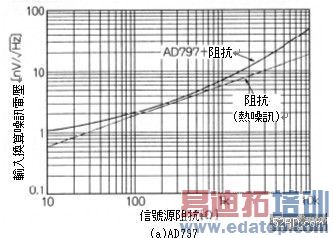

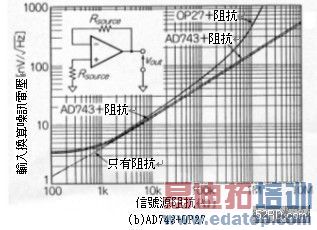

根据低噪音OP增幅IC的data sheet记载可知,输入信号源的阻抗只在特定范围噪音才会变成最低值。图12是低噪讯OP增幅IC AD797、AD743、OP27的部份data sheet资料,上述OP增幅IC包含输入阻抗热噪音在内的输入换算噪音电压,全部都是热噪音倍以下,这意味着OP增幅IC的内部噪音比热噪音更低。

选用OP增幅IC时除了考虑设计规范规定的输入信号源阻抗之外,还需要选择适合的type,例如输入信号源的阻抗为50Ω~2kΩ时必需选用AD797;输入信号源的阻抗为600Ω以上时则需选用AD743。

图12 超低噪音OP增幅器的输入信号源阻抗与输入换算噪音电压

b.必需限制增幅电路的频宽

在数十Hz以下的低频领域随着1/f噪音特性,会造成频率降低整体噪音则相对增加;在此同时数百Hz以的高频领域,则随着分配噪音会造成频率升高整体噪音也相对增加。

为迴避上述噪音领域,因此必需将增幅电路的频率特性,限制在十Hz至数百Hz范围内,藉此使噪音变成单纯的白色噪音,因为此时输入换算噪音会与频宽的平方根成比例。

c.利用实验决定直流偏压电流

根据以上考察结可知热噪音除外,直流偏压电流越低噪音就越小,因此一般认为与OP增幅IC整合用双极电晶体(bipolar transistor)电路的直流偏压电流越低,对低噪音会有很大的助益,然而实际上直流偏压电流太低的话,内部的等价阻抗则相对变大,而且热噪音也会大幅增加。

由于电晶体低电流时的transition频率fT,随着直流偏压电流降低变小,进而导致低频时几乎不会造成问题的分配噪音可能会出现影响,此外还有制程上的各种因素都会影响噪音值,因此建议读者利用实验方式,决定最适宜的元件与直流偏压电流。

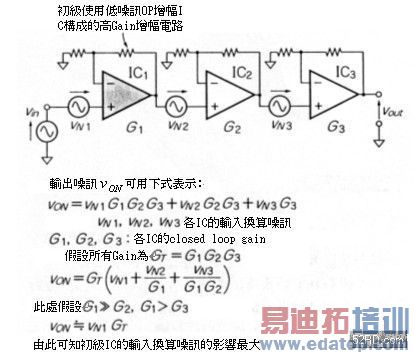

d.高Gain增幅电路若使用复数OP增幅IC,可获得低噪讯效果

利用汎用OP增幅IC制作增幅电路时,通常最大Gain只有100倍(40dB)以下,宽频增幅电路的场合Gain值更低。如果设计上要求高Gain时,可以参考图13的电路,将复数个OP增幅电路作纵连接。

图13 获得高Gain低噪音的方法

利用复数个等价输入噪音电压相同的OP增幅IC,制作高Gain增幅电路时,建议读者在初级段设置使用AD797、AD743,等超低噪音OP增幅IC构成的高Gain增幅电路,若有成本考量时,图10(b)的低噪音电晶体与OP增幅IC构成的电路,也可以当作初级段的增幅电路使用。值得一提的是此时流入电晶体电路collector的偏压电流设定,必需使信号源阻抗的噪音最小化。