- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

可定制MCU实现软硬件并行开发与最佳演算法

嵌入式MCU效能最佳化需软硬件平衡

对于开发基于嵌入式微控制器的应用来说,大多数人都同意软件和硬件是同样重要的。在许多情况下,软件比硬件要花费更长的时间和更多的金钱。现在的趋势是朝着电子系统级(electronic system level,ESL)设计发展,使用统一的语言(如System Verilog)对硬件和软件进行详细规范,然后按照这个统一规格同时进行开发。然而,ESL设计在实际应用上仍然有限。

此外,大多数围绕嵌入式微控制器构建的应用,都需要密集的演算法处理,而且往往需要即时地、或者以尽可能短的时间运行。例如,在全球定位系统(GPS;Global Positioning Systems)中,首次定位时间(the time to first fix,TTFF)和定位时间(Time To Fix,TTF)是密集式运算系统的关键性能指标。在电机控制中,至少需要以电机最大转速所需的控制输出速率来执行控制演算法。要使嵌入式微控制器达到最佳性能,需要在执行演算法处理时,在硬件和软件之间取得最佳平衡。

爱特梅尔(Atmel)CAP是由一个基于ARM的系统级晶片(System-On-Chip,SoC)和一个高密度的金属可程式设计(metal programmable,MP)数字逻辑模组构成的,前者提供基本的数据处理能力;后者可通过定制来提供专用功能的执行硬件,以及额外的週边设备和外部介面。CAP综合了合理的开发周期和具吸引力的量产成本双重优点,其开发流程强调的是软/硬件的并行开发。开发板采用一个高密度FPGA来模拟演算法执行和附加的周边设备/介面,然后固化这些功能到MP模组中。

CAP设计流程

图1展示了CAP设计流程中软/硬件并行开发的情况。以下段落将描述设计流程的具体步骤。

图1:CAP设计流程

■系统规格和软/硬体划分

CAP设计流程的起始点是为系统制定技术规格,以及划分硬件和软件所要实现的功能;并考虑到CAP平臺上的处理器和和固定的周边设备/介面,以及在MP模组中实现特定应用功能的可能性。一般原则是利用硬件来提高性能,而利用软件来提高灵活性,但实际上这种划分的变化范围很大。CAP设计流程的一个主要优点是:在将硬件制作成硅片之前,可以验证软/硬件的划分,如有必要,更可在模拟阶段进行纠正。

MP模组的定制、硬件综合/模拟

定制MP模组的第一步是开发专用硬件模组和相关的软件驱动程式。大多数情况下,使用Verilog RTL对硬件块进行编码,而软件则使用C、C++ 或 ARM组合语言。至于执行硬件和软体库模组的演算法,我们将在下一段中描述其流程。

将专用功能整合进MP模组是靠功能块的预留位置实例(placeholder instantiations)来完成的,这些功能块已写进爱特梅尔公司提供的MP模组RTL代码的范本中。其中一些模组已预先对DMA或者週边设备数据控制(Peripheral Data Controller,PDC)连通性(connectivity)进行了程式设计。下图2是带有PDC连通性的APB连接功能的例子。

////////////////////////////////////////////////////////////////////////////

// mpapb0:

// PORTS:

// psel_mpapb0 (APB select)

// mpapb0_config_clock (APB configuration clock)

// pwrite (APB write)

// paddr (APB address - 14 bits)

// pwdata (APB write data bus)

// mpapb0_channel_rx_end (from PDC - rx buffer full)

// mpapb0_channel_tx_end (from PDC - tx buffer full)

// mpapb0_rx_buffer_full (from PDC - both rx buffers full)

// mpapb0_tx_buffer_empty (from PDC - both rx buffers full)

// prdata (APB read data bus)

// mpapb0_size (to PDC - rx/tx transfer size)

// mpapb0_rx_rdy (to PDC - rx ready)

// mpapb0_tx_rdy (to PDC - tx ready)

// mpirq0 (Interrupt to AIC)

//

// Replace empty module with user-defined logic

// APB0

apb_pdc_empty i_apb0 (

//-- INPUTS

.nreset(nreset_r_apb),

.pclock(mp_pclocks[0]),

.config_clock(mpapb0_config_clock),

.psel(psel_mpapb0),

.pwrite(pwrite),

.paddr(paddr),

.pwdata(pwdata),

.rx_end(mpapb0_channel_rx_end),

.tx_end(mpapb0_channel_tx_end),

.rx_buffer_full(mpapb0_rx_buffer_full),

.tx_buffer_empty(mpapb0_tx_buffer_empty),

//-- OUTPUTS

.prdata(p_d_from_mpapb0),

.rx_size(mpapb0_size),

.tx_size(),

.rx_rdy(mpapb0_rx_rdy),

.tx_rdy(mpapb0_tx_rdy),

.apb_irq(mpirq0)

);

图2:MP模组中APB连接功能预留位置实例的 RTL代码

在整合MP模组内各项功能的RTL代码时,应验证该代码与CAP架构的相容性,然后再使用爱特梅尔提供的制程目标库(process specific target libraries)来综合RTL代码,并在整个元件上完成功能模拟。

■专用软件和作业系统的整合

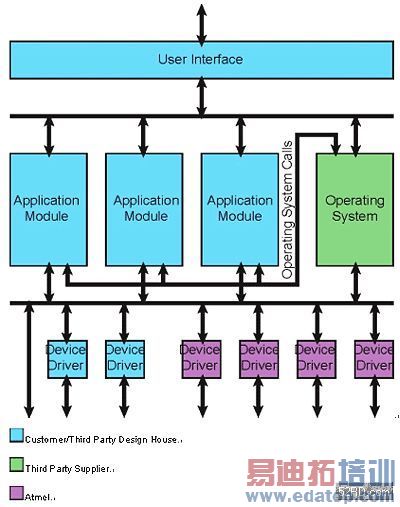

在硬件整合的同时,客户会开发和整合与硬件相应的软件套件。如图3所示,爱特梅尔为微控制器的固定部分、以及源自客户或协力厂商设计机构的MP模组,提供低层元件驱动程式。这些程式将与程式设计MCU和周边设备/介面的应用模组互相整合。如果需要作业系统,可从合格的协力厂商取得移植好的版本,并整合在软件套件中。

图3:CAP软件结构

然后,使用业界标准的开发工具来测试软件套件。如果有可用的工具,这个阶段更可以进行软/硬件的共同模拟。

■基于FPGA Emulation Board模拟板上的Emulation

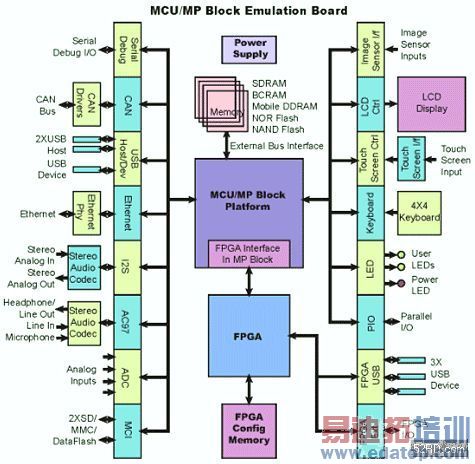

图4:CAP模拟板架构

设计流程中的一个关键步骤是在CAP模拟板上进行硬件和至少是低层软件的模拟。如图4所示,CAP模拟板包括整套的存储器、标准介面与网路连接,以及可以针对应用要求进行配置的额外连接,尤其是:

.CAP元件的固定部分以单晶片的形式实现,并且在MP模组上配有FPGA介面。

.高密度FPGA用以模拟带有嵌入式存储器和外部I/O的MP模组。

.FPGA配置存储器用来储存MP模组编译好的HDL代码。

.外部汇流排介面(EBI)和来自FPGA的外部输入/输出被连接至扩展板上的各种存储器:SDRAM、移动DDRAM、猝发手机RAM(Burst Cellular RAM)、NOR快闪存储器、NAND快闪记忆体等。这些储存器用来载入软件以及应用程式的数据。

.所有标准介面(CAN、USB、乙太网路、I2S、AC97、ADC、MCI等等)通过收发器/PHY/转码器(codec)与外部连接,实现了对外部介面以及元件联网/通信连接的全面测试/调试。

.图像用户介面(GUI)的所有元素均与板上的元件或介面连接,包括LCD、键盘、触控式萤幕介面等,这样就可以对 GUI的基本元素进行板上测试。

.提供外部并行I/O(PIO)和FPGA输入/输出,用于与专用外部设备的连接,以及非标准介面的实现。

.串列调试I/O与运行一组工业标准应用程式开发/调试工具的个人电脑互相连接。

这个CAP/FPGA组合以接近于元件最终的工作频率运行,可以实现元件的实际工作速度测试,包括MCU、标准介面、MP模组所实现的功能,以及到当前为止开发的所有软件──至少包括了元件的驱动程式、作业系统移植及控制MP模组功能的应用代码模组。开发人员无须付出任何成本,就可以对硬件或者软件元素进行修正。

经验告诉我们,这一模拟步骤几乎总能指出在硬体和/或软件;或者元件的硬件和软件介面中的错误。在该阶段便能够纠正和重新测试元件的整个设计,是缩短设计阶段、降低设计成本,以及提高软/硬件首次成功率的一个主要因素。另一个优点是:最终设计的模拟版本可以用作未来设计的起始点,从而大大节省设计工作量。

CAP演算法实现流程

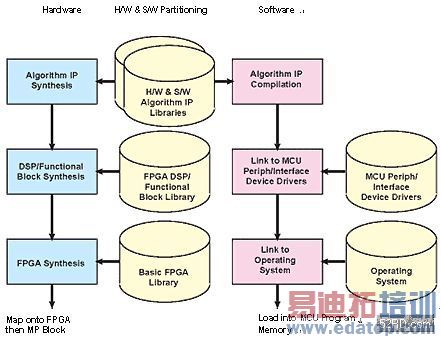

以上介绍的CAP设计流程可以用来开发最佳软/硬件组合,以实现演算法的高效执行。图5所示为具备演算法所需的软/硬件功能库的开发流程。第一步是使用FPGA库和工具进行初步的演算法软/硬件划分,然后将基于硬体的功能映射到类似DSP的结构或者其他在FPGA中实现的处理元素上。同时,对基于软体的演算法进行编译,使之能透过微控制器来执行。此时微控制器可以在自己的位址空间中看到FPGA/MP模组。

图5:CAP演算法软/硬件划分和实现流程

在硬件方面,首先利用功能库或FPGA供应商所提供的工具,将演算法模组进行综合。综合的结果再与所需的DSP,或类似的源自FPGA厂家资源库的处理功能模组进行综合。最后,将这些综合后的高级结构映射到基本的FPGA结构中,以便配置CAP开发板上的FPGA。

软件方面,首先要编译演算法所需的IP模组,然后与爱特梅尔的低层元件驱动程式库相连结,这些驱动程式负责处理CAP 系统级晶片的多个週边设备和外部介面的操作。如有必要,编译后的代码还可与作业系统、使用者介面和运行整个系统的顶层控制模组相连结。完整的代码将被载入到处理器的程式储存空间,然后,再进行如前段所述的开发模拟过程。

CAP金属程式设计和制备流程

当元件功能被模拟并得以确认后,用于FPGA程式设计的最终RTL代码就会被映射到CAP MP模组的金属层。严格的后布局模拟技术,能确保CAP金属程式设计的功能与模拟版本完全一致。

接着,就可采用在金属层之前已预制的空白元件快速生产出原型。有了这些原型,应用开发人员就能对元件的软/硬件功能进行最后验证,尤其是检查演算法的处理是否最佳化。在最坏的情况下,如果原型达不到要求,从模拟阶段重新开始开发所增加的成本和时间也是合理的,比更换标准单元ASIC的整个掩模过程所耗费的成本和时间少得多。

当原型认可后,就可用与生产原型相同的制程流程,开始进行定制CAP元件的量产。

基于CAP 架构的元件更可以根据应用现场的回馈意见,以及对应数据处理演算法的升级,通过修改开发板上FPGA的配置来作出改进,而所需的开发时间较最初版本更快;成本也更低。

结论

爱特梅尔的CAP可定制微控制器能解决软/硬件并行开发,以及最佳化复杂演算法的执行所面对的种种困难;CAP开发板能以接近真实运行的速度和实际使用条件,模拟演算法的软/硬件划分,为确定哪个方案更最佳化而进行的反復模拟不会增加任何成本。如此一来,设计者选中的实现方案就可以固化成一个性能优秀、功耗低,并且量产成本极具吸引力的产品。

上一篇:液晶电视电源的最新发展趋势探析

下一篇:模拟电路设计(五)如何设计差动增幅电路