- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

采用先进工艺并改进存储单元的布局 使DRAM成本每年下降30%

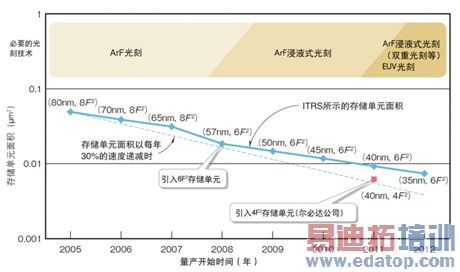

目前,主流的DRAM存储单元的面积为8F2,2007~2008年,业界开始正式启用6F2的存储单元技术。在计划中明确表示要采用4F2存储单元技术的目前还只有尔必达公司。2006年版的国际半导体技术路线图(ITRS)中,制定了全球半导体厂商到2020年的技术路线图,但其中并未提到4F2 DRAM存储单元技术(见图1)。

某韩国DRAM龙头企业的工程师认为,安达隆郎的上述演讲是为了表明该公司的决心:虽然目前难以实现,但公司仍然坚持引入4F2 存储单元技术,以使DRAM每年的成本削减速度能达到30%。如果根据ITRS 来计算存储单元面积的走势,相对于2005年~2008年间每年30% 的削减速度,2009 年以后,削减速度将放缓,每年大约可削减20% 左右(见图1)。

按照尔必达公司的计划,如果真的能在2011年量产40nm 工艺的4F2 存储单元,存储单元面积每年30% 的递减率就至少可以维持到2011年。如果采用4F2 存储单元,那么,相同工艺下存储单元的面积就只有6F2 产品的2/3。那么,DRAM成本每年30%的递减率也可维持到2011年。

采用先进工艺与改进存储单元布局双管齐下

以往,DRAM实现低成本主要是依靠采用更先进的工艺。只要使用更先进的制造工艺,基本就能实现每年30%的成本递减率。但是,自从2004年最小特征尺寸低于100nm之后,光靠工艺技术的发展已不能再维持上述的递减率。因此,DRAM厂商开始着手改进存储单元的布局,以缩小存储单元的面积。

|

| 图1 保持每年30% 的成本递减速度 |

|

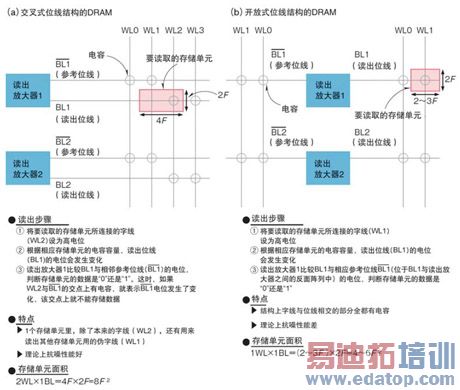

| 图2 引入开放式位线结构,实现6F2存储单元 |

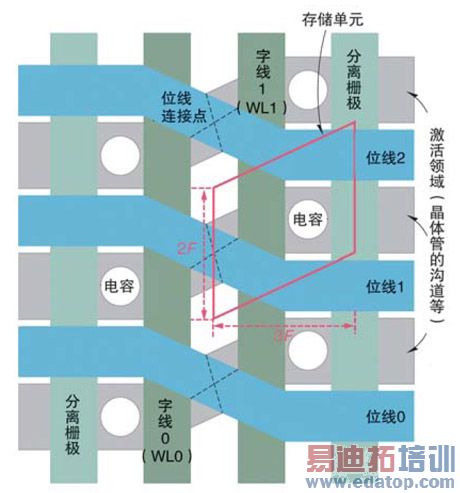

2007年~2008年间,许多厂商正式在产品中使用面积为6F2 的存储单元(见图2)。与8F2 的存储单元相比,DRAM的芯片面积可削减20%以上。而且,使用6F2存储单元后,产品在性能、耗电量、可靠性等方面都与以往的产品基本相同。已有多家生产厂商开始量产6F2存储单元的DRAM。先行一步进入实际应用的是美光科技公司(见图3)。该公司从2002 年开始将其应用到量产产品中,从2006 年秋开始使用6F2 存储单元量产78nm 的DRAM。继美光公司之后,三星电子从2007 年上半年开始使用6F2 存储单元量产68nm的 DRAM。在2007年末~2008年第2季度,尔必达公司也开始采用6F2 存储单元量产65nm的DRAM,主要应用于1Gb产品中。

|

| 图3 美光公司6F2 存储单元的存储单元布局 |

消除噪声

为了实现6F2的存储单元面积,各公司都采用了开放式位线结构。这种结构之所以能减小面积,是因为其字线与位线相交的部位全都能放置电容(见图2b)。之前之所以没能将开放式位线结构的存储器单元推向实际应用,主要是因为其抗噪性能太差。而面积为8F2的存储单元由于采用的是交叉式位线结构,所以避免了抗噪性差的问题( 见图2a)。

在DRAM里,从存储单元输出的微电压需要通过读出放大器检出。这时,是以参考位线的电位为基准值。在交叉式位线结构中,要读取的存储单元的旁边就有参考位线。因此,即使要读取的存储单元受到了噪声影响,由于参考电位也会受到同样影响,所以误读的危险性较小。但在开放式位线结构的DRAM里,参考位线离要读取的存储单元较远,所以受到的影响不一样。

而现在,开放式位线结构的存储单元之所以能够进入实际应用,是因为DRAM内部电路的抗噪能力较强。而且,由于存储单元面积的缩小,存储单元的寄生电阻也明显降低,电容上部电极导入了金属材料,读取时的阻抗值也有所降低,所以读取电流增加,噪音的影响也相对减小

4F2 存储单元还处于讨论中

6F2 存储单元之后应该就是面积为4F2的存储单元。目前尚未有生产商提到能够实现其实际应用,该技术仍然属于正在讨论中的候选技术。要实现4F2存储单元,需要引入多种新技术。最大的DRAM厂商三星公司寄望于使用纵向晶体管,以及在1 块硅晶圆上层叠存储单元的技术。

|

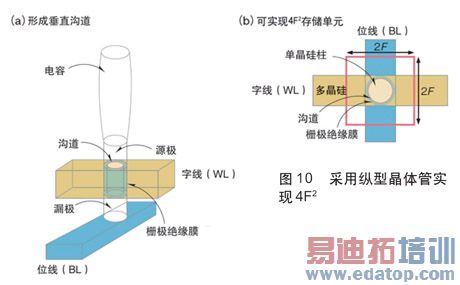

| 图4 采用纵型晶体管实现4F2 |

在纵向晶体管中,存储单元和晶体管沟道是相互垂直的(见图4)。字线与位线交叉的部分形成垂直沟道,外围是栅极绝缘膜(见图4a)。沟道正上方是电容,存储单元面积可压缩为4F2(见图4b)。

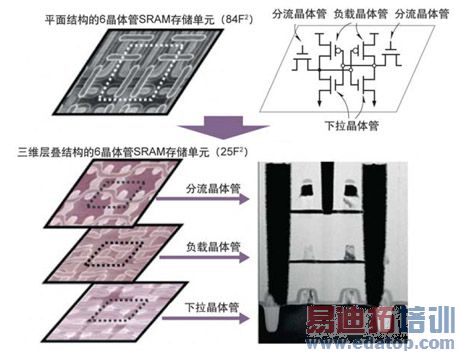

存储单元层叠技术是指,将目前的8F2存储单元层叠放置2个,就能达到4F2的效果。虽然三星公司已发布了 NAND 闪存和SRAM 等非DRAM 存储单元的晶体管层叠成果,但在DRAM存储单元的层叠方面,包括三星公司在内,尚未有公司在知名学术会议上发表过相关研究。目前正在研究之中的是SRAM,已经试产了存储阵列。现在,手机等设备中使用的SRAM存储单元面积较大,达到84F2。三星公司曾将原来在同一平面内的晶体管在三维空间内进行层叠,结果就将6晶体管存储单元的面积缩小到了25F2(见图5)。

|

| 图5 将晶体管进行3维层叠 |

与SRAM相比,DRAM存储单元的层叠技术具有较大的障碍。因为在DRAM中,除了晶体管之外,还需要将电容进行层叠。

重新考虑多值技术

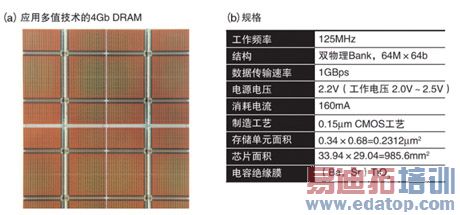

也有意见认为,要想实现4F2存储单元,就应该讨论怎样应用多值技术,也就是在一个存储单元内存储多位数据。NAND 闪存中已经开始应用多值技术,但在DRAM中,从NEC在1997年的ISSCC上发表相关文章之后,到如今近10年时间内,在国际学会上都没有相关报道。见图5)。

|

| 图6 需讨论是否引入多值技术 |

NEC 当时发布的是应用了2位/ 存储单元多值技术的4 G bDRAM(见图6)。该试制芯片的物理存储单元面积大约是10F2,因此,每位的实际存储单元面积只有5F2。但是,当时DRAM制造工艺的发展较为顺利,所以业界并未关注多值技术的开发。

|

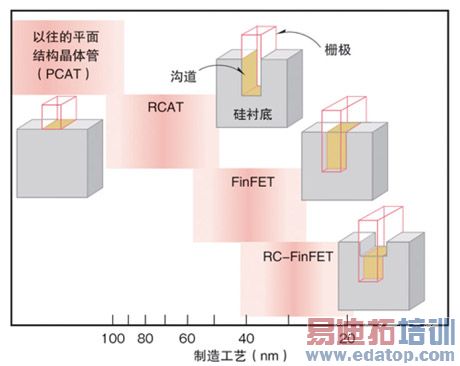

| 图7 存储单元晶体管向三维化推进 |

最近,重新关注多值技术的DRAM开发工程师开始增加。某生产厂商的DRAM工程师表示:“现有技术已经陷入瓶颈,所以,以往曾昙花一现的技术,需要重新加以讨论。过去,采用开放式位线结构的6F2 存储单元,也被认为抗噪性能差,难以进入实际应用。但事实证明,经过开发之后,该技术颇为成功。”

制造工艺发展缓慢

推动DRAM低成本化的另一项主要技术就是制造工艺的进步,到目前为止,都是它在维持着DRAM低成本化的速度。DRAM生产厂商仍在一点一点地缩小最小特征尺寸,今后仍将继续进行相关开发。例如,在2006 年版的ITRS 里, DRAM的最小特征尺寸在2007年为65nm,但到2008年就变为57nm,以后也将持续缩小,到2013年将达到32nm。据该路线图描述,制造工艺将以每年7.13% 的速度递减。

制造工艺发展速度之所以较为缓慢,其中一个原因就是,目前在尽可能地不使用价格高昂的光刻设备,而继续使用现有的光刻设备。尔必达公司认为:“我们之所以用65nm 工艺生产6F2 存储单元,也是希望尽可能地使用现有的ArF 光刻设备。引入4F2存储单元也是出于同样的理由。采用3Xnm进行量产时,就需要使用EUV 光刻设备,这在2012 年~2013 年是否能符合经济效益,现在还不能肯定。如果要将4F2存储单元实用化,则可以使用面向40nm 的浸液式ArF 等光刻设备。”

改进晶体管结构

要继续使用更先进的制造工艺,除了光刻设备的价格问题,还需要对存储单元的晶体管技术加以改进。采用更先进的工艺时,存储单元晶体管的沟道会不断变短,沟道变短后所带来的直接问题就是截止电流增大。这样,刷新周期必须小于现在的64ms,容易增加用户负担。

截止电流直接关系到DRAM的性能,因此,为了将截止电流维持在一定范围以内,各DRAM厂商开始从根本上改变存储单元晶体管的结构。以前,是在与硅衬底相同的平面上设置沟道,现在开始引入三维技术。三星电子公司从90nm 和80nm 的 DRAM 开始引入被称为RCAT(recess channel array transistor,凹道排列晶体管)的技术(见图7)。

该技术在硅衬底上设计了一个凹槽,沿着该凹槽形成栅极绝缘膜,然后用多晶硅填满凹槽。由于沟道可以沿着凹槽形成,所以不光缩小了二维方向上的尺寸,而且延长了沟道,从而达到控制截止电流的目的。

三星公司表示,如果要支持70nm以下的工艺,还需要对RCAT进行改良。如果光是缩小RCAT 结构,那么凹槽尖端部分的曲率半径就会变小,栅压的加压效率会变差。

为了提高栅压的加压效率,该公司开发了S-RCAT(球状凹道排列晶体管)技术,也就是将凹槽做成了球状。该公司计划将此技术应用于部分80nm 工艺中,并将正式引入70nm DRAM 中。

三星公司正在重新讨论怎样改进RCAT,以应用到60nm 工艺中。如果直接将S-RCAT 技术用于更先进的工艺,那么球状顶部比较容易聚集电场,从而影响栅极绝缘膜的可靠性。该公司又开发了新的URCAT(U 型凹道排列晶体管)结构来避免这一问题。U-RCAT 就是将凹槽顶端做成U 字形状。将球状变为U 状,就可以缓解电场聚集,从而提高栅极绝缘膜的可靠性。(全文完,记者:大石基之,本文中文翻译稿由《电子设计应用》特别提供)

上一篇:如何保护便携应用的高速数据线路

下一篇:液晶电视电源的最新发展趋势探析