- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

模拟电路设计(十七)非线形电路Converter

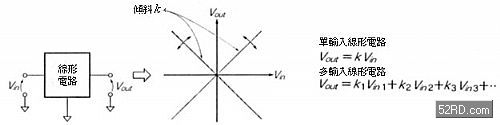

在OP增幅电路经常可以发现非线形电路的踪影,由于非线形电路涉及范围非常广泛,所以本文以常用的电压比较器(Comparator)为主轴,探讨非线形电路的动作特性与使用技巧。 模拟电路可分成线形电路与非线形电路两种。如图1所示输出、入两者呈直线关系的电路,就是一般所谓线形电路。输出、入两者的关系通常是以传达关数G(jω)表示,由于G(jω) 的分子与分母两者都是使用jω的高次多项式,或许读者会认为这样的电路无法变成直线性,不过若将jω固定(亦即频率维持一定)并改变输入振幅,输出、入两者就会变成直线状,由此可知输入的一次关数电路等同于输出的线形电路,由于线形电路本身具备所谓的「重叠要素」,而非线形电路的输入并不是一次关数的电路,所以不符合上述的基本要素。

|

图1 线形电路的输出入关系

非线形电路

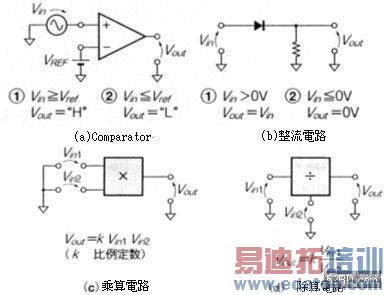

图2是典型的非线形电路;图2(a)是电压比较器(comparator),它的动作原理与OP增幅电路相同,都是利用大gain将非反相端子与反相端子之间的差动电压增幅输出。图2(b)~(f)为演算电路,这些电路都是利用数字作演算,因此具有速度上的优点。

|

|

图2 各种非线形电路

有关无效时间电路,具体而言例如将输入信号转换成A-D进行数位演算,接着再作D-A转换输出的非线形电路,就属于无效时间电路。一般延迟电路输出step应答时,通常输出Level会逐渐增,相较之下无效时间电路即使输入信号,在一定时间内几乎不会进行任何输出,之后输出Level会突然变大,出现这种现象的电路就是所谓的「无效时间电路」。由于数位演算具备高精度低成本等优点,因此目前广泛应用在类比电路,不过这类电路的演算时间,与模拟/数字转换时间隐藏着「无效时间」等问题,尤其是负归返回路(return loop)一旦出现无效时间时,即使变更输入也无法改变电路的输出特性。由于负归返会持续改变输出,结果反而造成电路出现over shoot现象,因此负归返回路内如果含有非线形电路的话,一般而言比较不易获得稳定的动作。

电压比较IC

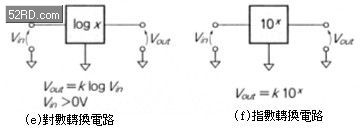

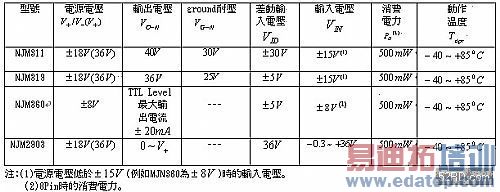

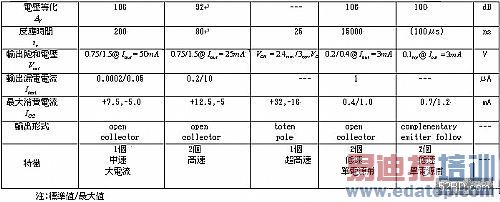

表1是典型的电压比较(comparator)IC与OP增幅IC NJM2904的规格;图3是各电压比较器IC的脚架(pin)连接方法。根据表1的记载可知电压比较器都是利用 电压驱动。

|

图3 各种电压比较器IC的脚架连接方法

|

(a)绝对最大设计值(Ta=250C)

|

(b)电气特性(Ta=250C,R1=2kΩ )

表1 常用电压比较器IC与OP增幅器IC的规格

如图2(a)所示虽然电压比较器的符号与动作几乎与OP增幅器完全相同,不过使用方法却截然不同,其中最大差异是电压比较器不需施加负归返(return),而是利用两输入之间的电位差,使输出自动饱和并依附至L或是H其中一方,一般user使用电压比较器时会根据上述特性,先将输出Level与逻辑IC的输入Level作匹配,接着才输入至数位电路内部。

最近大部分的电压比较IC都是由低电压、省能源CMOS IC所构成,这类IC包含低速、高速,以及open drain输出段与CMOS输出等各种type。

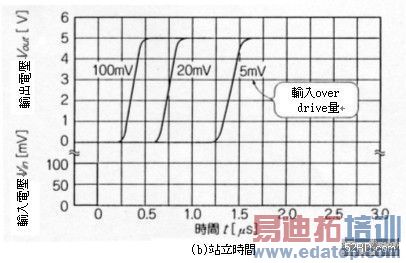

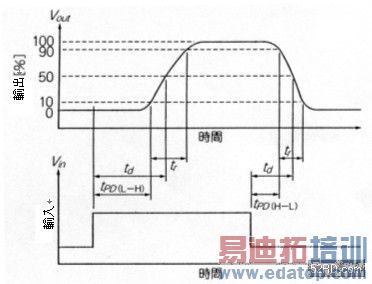

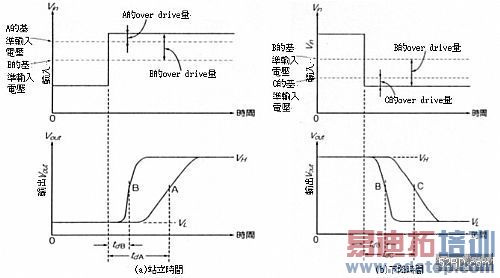

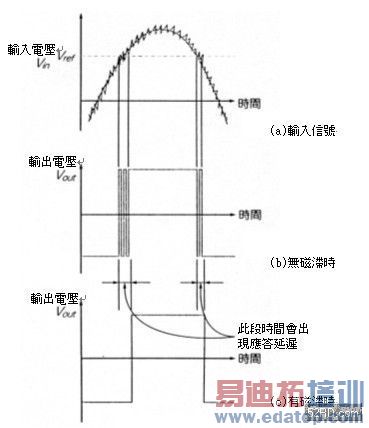

如上所述OP增幅器必需施加负归返才可当作电压比较器使用,OP增幅器与电压比较器两者最大差异是应答速度。图4是NJM2903的应答特性摘要;图5是有关应答时间的定义,图中的td表示应答时间。此外一般所谓的电压比较器应答速度是指输出依附至正或负的任一方,而且可使两输入端子的差动电压反相,并通过中点所需的时间而言。

|

|

图4 NJM2903 IC电压比较器的输出入应答特性

|

图5 电压比较器的输出入应答波形

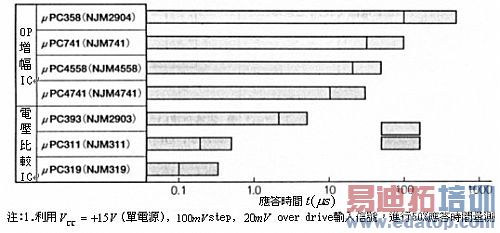

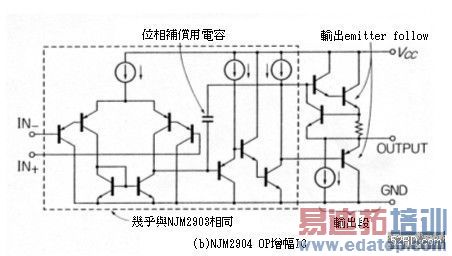

如图6所示输出呈反相状态,而且输入比输入电压更大电压时称为「over drive」,一般而言over drive的应答速度都会变快(图4)。图7是OP增幅IC与电压比较IC,实际应答速度比较结果,由图可知电压比较IC的应答速度比OP增幅IC更快,此外根据照片2的NJM2904与NJM2903应答波形显示,电压比较IC的应答速度几乎是OP增幅IC的100倍以上。

OP增幅IC未施加负归返,输出不论是正或是负饱和依附状态,两输入端子的差动电压一旦反相的话,内部电路从饱和状态回復到开始动作为止所需要的时间,会比电压比较IC更花时间,如图5所示它的延迟时间tPD比利用through rate计算的tr或是tf更大,值得一提的是此处所谓的「through rate」,是指施加负归返时线形动作的速度而言。

图8是单电源增幅IC NJM2904与电压比较IC NJM2903的内部等价电路,两者最大差异是输出段的电路结构,与位相补偿用电容器的有无而已。由表1(b)可知应答速度除外,上述两IC的电气特性非常类似。两IC的应答速度会出现差异,主要原因是受到位相补偿用电容器的影响所致(8(b)),不过输出段的emitter follow应答速度却无延迟现象。电压比较器若无位相补偿用电容器的话,一旦施加负归返电压比较器就会产生波动,因此电压比较器通常会设置位相补偿用电容器,藉此防止电路产生波动现象。

|

图6 电压比较器的输入信号与输出应答波形

|

图7 电压比较IC与OP增幅IC的应答速度比较

|

|

图8 电压比较IC与OP增幅IC的内部等价电路

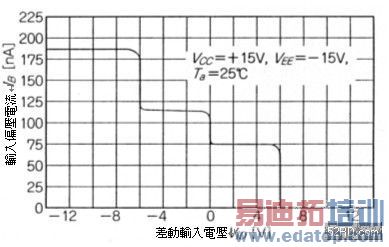

一般而言汎用OP增幅IC的输入偏压电流,与offset电压有偏低的倾向,相较之下电压比较IC的差动电压范围有一定的限制。如图9所示电压比较IC的输入偏压电流,会随着差动输入电压产生大幅变动。虽然电压比较IC的速度往往是主要设计项目,然而实际上应答越快,输入偏压电流就越大,因此它的输入特性不如OP增幅IC。

OP增幅IC即使在差动输入电压绝对最大定格值范围内动作,经常无法当作电压比较IC使用,例如NJM4580与NJM072B的输入电压,若低于负电源电压 以下的话,理论输出就会反相。此外汎用类比IC的规格书中若未记载特性时,就必需参考原始型录的说明。表1记载的IC资料为国际半导体公司提供的数据摘要,若欲获得更完整的资料就必需参考该公司的型录。

如果gain很大的话,反相端子与非反相端子的输入电压就可以作微量差异比较,进而提高直流精度,然而实际上为了提高应答速度,却必需抑制IC内部电路各增幅段的gain,例如gain 110dB的NJM4580 OP增幅IC,它的动作速度相当迟缓,而NJM319电压比较IC的gain只有92dB,因此应答速度比NJM4580快,由此可知低速电压比较IC的gain通常都比较大。

|

图9 电压比较IC NJM311的输入偏压电流

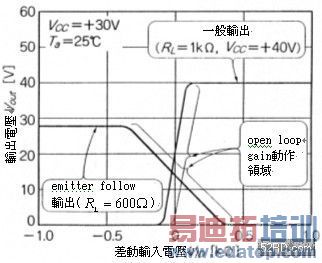

图10是电压比较IC NJM311的输出电压对差动输入电压的特性与内部等价电路;图10(a)是分别从第7pin emitter共通端子与第1pin emitter follow端子,取出输出时的open

loop gain的差异特性;图10(b)是emitter共通时,电压比较IC NJM311的电压等化特性。

OP增幅IC的open loop gain频率特性是以-6dB/oct.一次延迟特性逐渐递减,相较之电压比较IC则以二次甚至二次以上延迟特性递减,此外若对电压比较IC施加负归返的话电压比较I器就会产生波动现象。

|

|

图10 电压比较IC NJM311的输出入特性与内部等价电路

应答速度与输出电压是表示电压比较器输出性能重要的参数。虽然有许多OP增幅IC的输出段是属于补偿式(complimentary)的emitter follow,不过电压比较IC几乎都是open collector(open drain)或是totem pole结构,因此电压比较IC能够轻易与其它逻辑IC相互连接。

有关输出段的结构,一般而言中等程度以下的应答速度,大部份是採用open collector输出;超高速应答则需搭配高速逻辑IC的输出Level才能获得预期的高速输出效果。

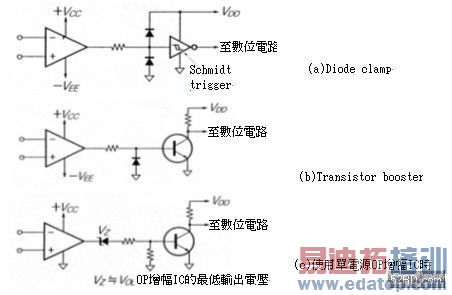

必需注意的是OP增幅器当作电压比较器使用时,该OP增幅器若与逻辑IC连接的场合,必需考虑逻辑IC的输入电压规格匹配性,例如两电源的OP增幅器输出有正、负波动之虞时,就不可以直接与逻辑IC连接。此外具有站立、下降时间上限值限制的逻辑IC与输出连接时,若直接将Schmidt trigger输入的gate IC构成的buffer插入OP增幅IC内,却未将站立或是下降时间进行高速化处理的话,该逻辑IC就会产生波动,这种振盪现象称为「metastable状态」,尤其是逻辑IC的输入电压若游走于”H”与”L”之间时,它的输出就会在”H”与”L”之间波动形成发振状态。

各种电压比较器电路(Competitor)

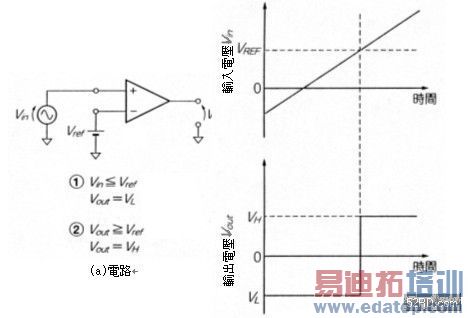

基本电路

图11是电压比较电路的基本结构,若依照图12的指示连线的话,电压比较电路就成为正基准电压的单电源型电压比较器。此外抑制输入阻抗(impedance)乃是设计上必需注意的重要事项,尤其是输出变成反相的迁移时段内,若是以open loop gain方式动作,必需防止噪讯(noise)混入,因为一旦混入噪讯的话电路会出现误动作等困扰,所以layout封装时必需设法杜绝噪讯混入。

虽然图11与图12的电路,都是将基准电压连接至反相输入端,并将信号电压连接至非反相输入端,然而实际上电压比较器却是利用两输入端子之间的差动输入电压动作,因此信号电压与基准电压即使任意互换,除了输出的动作会反相之外,对电路并不会造成任何问题。

|

图11 电压比较IC的动作特性

|

图12 正基准电压的单电源型电压比较器

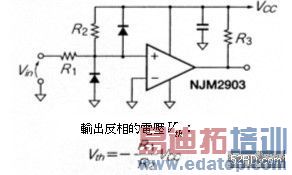

电流输入型电压比较电路

图13是电流输入型的电压比较电路,基本上它是利用电阻(R2,R3)将电压转换成电流进行比较,若依照图14指示连接的话,本电流输入型电压比较器就会变成负基准电压单电源电压比较器,这种电路最大缺点是与IC输入端连接的阻抗会变得非常大。类似NJM2903反相输入端子与输出端子非常贴近的电压比较IC,如果反相输入端子的阻抗很大的话,由于端子之间的浮游容量会形成负归返进而产生波动现象,为防止电路产生波动现象,因此在图13的非反相输入端子与输出端子之间设置电容器,藉此消除负归返。

|

图13 电流输入型型电压比较器

|

图14 负基准电压电流输入型电压比较器

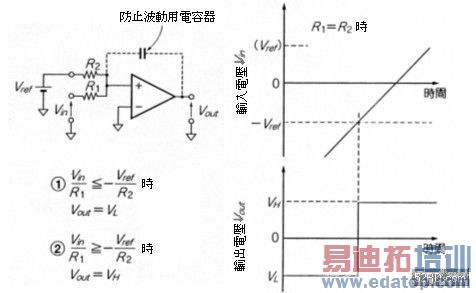

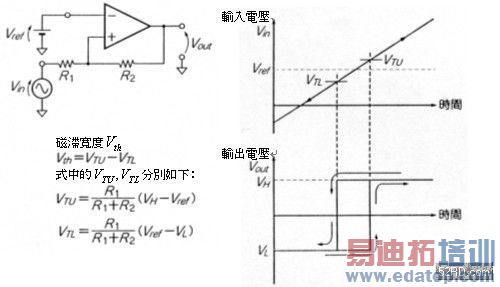

磁滞型电压比较电路(Hysteresis Competitor)

如图15所示,若对电压比较器施加正归返的话,电压比较器就会出现磁滞(hysteresis)特性,具备这种特性的电路称为Schmidt电路,或是史密特触发(Schmidt trigger)电路。

|

图15 磁滞型电压比较电路

如图16所示即使重叠噪讯(noise)混入电路,该噪讯Level若未超越磁滞宽度的话,输出就不会产生multi pull trigger误动作,只会出现与磁滞宽度相同的应答延迟。

|

图16 磁滞效应

介面电路

相较于电压比较用IC,OP增幅IC与数位电路连接时,必需设置如图17所示的介面电路,如此一来类似74HC系列具有输入信号站立、下降时间上限的逻辑IC(例如tr,tf≤500 ns,VDD=4.5V)就不会产生波动现象。此外逻辑IC的输出如果长时间处于非 与非 状态,一旦陷入metastable的话,逻辑IC的输出会在"H"与"L"之间出现类似multi pull trigger波动,尤其是flip flop IC与counter IC的clock输入会成为metastable状,进而产生极大的输出。

|

图17 OP增幅器构成的电压比较电路与逻辑IC的介面电路

测试各种电压比较电路

磁滞型电压比较电路

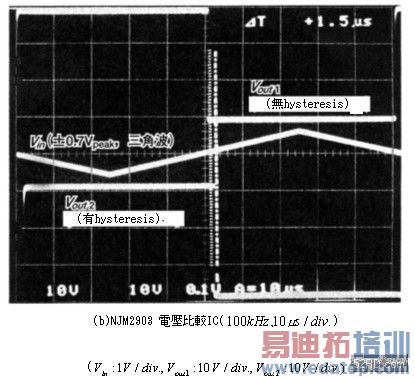

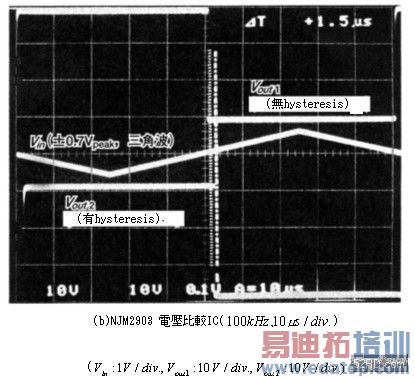

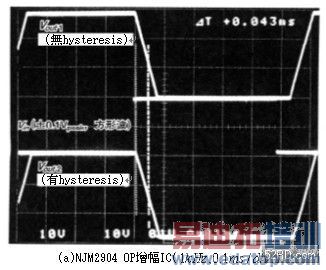

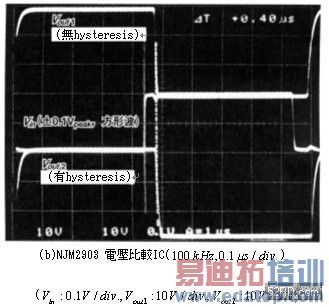

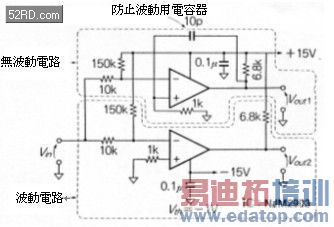

本实验使用NJM2904 OP增幅IC与NJM2903电压比较IC,制作如图18所示基准电压为 的zero cross电压比较器,接着再分别输入三角波与方形波。图18上方的电压比较器无磁滞,下方的电压比较器则具有 的磁滞;照片1是输入电压为±0.7Vpeak的应答波形,照片2是输入电压为±0.1Vpeak的应答波形。

根据测试结果显示,电压比较IC的动作速度比OP增幅IC快100倍以上,此外由照片1可知磁滞宽度即使只有60mVp-p,而且Vout2 比Vout1慢;相较之下若输入±0.1Vpeak的方形波,就不会受到磁滞宽度的影响,Vout2与Vout1两者的动作速度几乎完全相同(照片2)。

|

|

照片1 实验电路Ⅰ,输入站立缓慢的信号

|

|

照片2 实验电路Ⅰ,输入站立极快的信号

电流输入型电压比较电路

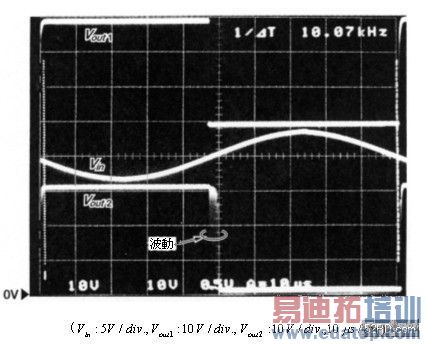

首先制作电流输入型电压比较电路(图19),接着进行电路特性实验;照片3是测试结果,根据实验显示未设置可以消除负归返专门电容器的Vout2会出现波动现象,不过只要追加10pF的电容器,Vout1就不会产生波动。

|

图19 实验电路Ⅱ电流输入型电压比较电路

|

照片3 实验电路Ⅱ,电流输入型电压比较电路的输出入应达波形

OP增幅电压比较器构成的介面电路

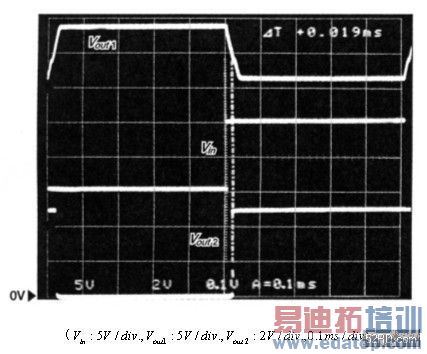

最后进行介面电路(图20)电路特性实验。由于电压比较器只要能够输出由电晶体Tr1产生的booster动作电压,因此本实验将Zener diode插入limiter,根据测试结果显示Zener diode导通期间,NJM2904 OP增幅IC内部不但无法饱和,而且还出现100%的负归返(return),其结果造成tpd对应答时间不但没有受到任何影响,应答时间反而变快,根据照片1与照片2的波形可知,应答时间从43µs 变成19µs,大约缩短一半左右。

|

图20 实验电路Ⅲ,介面电路

如何防止噪讯造成误动作

一般工程师都认为电压比较电路非常容易设计,所以忽略噪讯问题的重要性,然而事实上电压比较器的输出处于迁移状态时,是以open loop gain方式动作,此时电路对噪讯非常脆弱,因此工程师经常被噪讯问题围困,有鑑于此接着要介绍几种杜绝噪讯造成误动作的方法。

(一).设置电源pass control

简单的说就是不能因为电压比较电路容易设计,所以忽略设置电源pass control的重要性,具体方法是充分利用电压比较电路器周围「via接地」结构,可以有效杜绝噪讯造成误动作。

(二).使电路具备磁滞(hysteresis)特性

磁滞宽度会对噪讯产生不感带效应。不过输入的噪讯若超过磁滞宽度的话,仍然会引发电路动作。此外zero cross电压比较器的zero cross点,会有timing偏离的困扰(照片1)。

具备二次延迟特性的负归返很容易产生波动,这意味着磁滞(hysteresis)可以利用正归返获得。磁滞回路如果出现二次以上延迟特性时,上述正归返就会变成负归返。电压比较IC如果无内部回路位相补偿设计,却施加负归返的话就会出现波动现象,因此设计磁滞回路时必需设法防止二次以上的延迟特性。

(三).信号输入至电压比较器之前先增幅

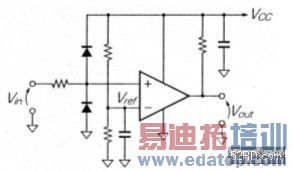

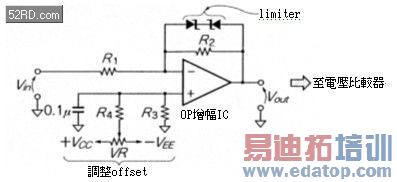

如图21所示若将附有limiter的增幅器,装在zero cross电压比较器前段的话,除了可以强化信号的抗噪讯能力之外,上述的的timing偏离误差也可以降至几乎忽略的程度,而且对over drive的高速化也有正面的助益。

必需注意的是除了limiter的设置之外, Vout不可以超越电压比较器的容许差动输入电压范围。根据图21的电路显示,由于limiter动作时仍然施加负归返,因此OP增幅器的内部无法获得饱和,此外它的应答速度取决于through rate,所以应答速度比无limiter,而且是内部饱和的OP增幅器更快(照片4)。

|

图21 电压比较器前段设置limiter会强化噪音

|

照片4 OP增幅IC构成的介面电路电压比较器的输出入波型

(四).使用滤波器

无论如何都无法迴避噪讯引发误动作的场合,建议读者不妨考虑使用滤波器。虽然滤波器会招致各种副作用,不过只要充分掌握信号、噪讯与副作用的特性,事先备妥副作用抑制措施,滤波器对减少噪讯造成的误动作具有很好效果。

(五).应答速度控制在最小范围内

一般而言OP增幅IC的动作特性比低速电压比较器更另人放心,即使是操作电压比较器IC,也需具备超高速电压比较器IC使用经验,因此最简单的方法就是根据应答速度的需求,选择最小范围的电压比较器IC,同时在电路中设置可以消除负归返的电容器。

上一篇:IC设计面临三重挑战 EDA工具随需应变

下一篇:关于旁路电容的深度研讨(三)