- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

实现高速PCB之布线问题探讨

虽然印刷电路板(PCB)布线在高速电路中具有关键的作用,但它往往只是电路设计过程的最后几个步骤之一。高速PCB布线有很多方面的问题,关于这个主题已有大量的文献可供参考。本文主要从实践的角度来探讨高速电路的布线问题,主要目的在于帮助新用户当进行设计高速电路PCB布线时,能注意到需要考虑的多种不同问题。另一个目的是为已经有一段时间没接触PCB布线的客户提供一种复习资料。受限于文章版面,本文不可能详细地论述所有的问题,但是文中将讨论对提高电路性能、缩短设计时间与节省修改时间等具有最大成效的关键部分。

虽然本文主要针对与高速运算放大器有关的电路,但是文中所讨论的问题和方法对用于大多数其他高速模拟电路的布线是普遍适用 的。当运算放大器工作在很高的射频(RF)频段时,电路的性能很大程度上取决于PCB布线。图纸上看起来很好的高性能电路设计,如果由于布线时粗心马虎受到影响,最后只能得到普通的性能。因此在整个佈线过程中预先考虑并注意重要的细节会有助于确保预期的电路性能。

原理图

尽管良好的原理图不能保证有好的布线,但是好的布线却是始于良好的原理图。在绘制原理图时要深思熟虑,并且必须考虑整个电路的信号走向。如果在原理图中从左到右具有正常稳定的信号流,那么在PCB上也应具有同样好的信号流。在原理图上尽可能多给出有用的资讯。如此就算有些问题电路设计工程师无法解决,客户也可以寻求其他管道帮助解决电路的问题。

除了普通的参考识别字、功耗和误差容许范围外,原理图中还应该给出哪些资讯呢?下文将提供一些建议,可以将普通的原理图变成最佳的原理图。加入波形、有关外壳的机械资讯、印制线长度、空白区;标明哪些元件需要置于PCB上面;给出调整资讯、元件取值范围、散热资讯、控制阻抗印制线、注释、扼要的电路动作描述以及其他资讯等。

谁都别信

如果不是自行设计布线,一定要留出充裕的时间仔细检查布线人的设计。很小的预防可以抵得上一百倍的补救。不要指望布线的人能理解设计者的想法。在布线设计过程的初期意见和指导是最重要的。能提供的资讯越多,并且整个布线过程中介入的越多,结果得到的PCB就会越好。给布线设计工程师设置一个暂定的完成点,按照所想要的布线进展报告快速检查。这种闭合环路方法可以防止佈线误入歧途,进而让重新设计的可能性降至最低。

需要给布线工程师的指示包括:电路功能的简短描述,标明输入和输出位置的PCB略图,PCB层叠资讯(例如,板子有多厚,有多少层,各信号层和接地平面的详细资讯:功耗、地线、模拟信号、数字信号和RF信号等);各层需要那些信号;要求重要元件的放置位置;旁路元件的确切位置;哪些印制线很重要;哪些线路需要控制阻抗印制线;哪些线路需要匹配长度;元件的尺寸;哪些印制线需要彼此远离(或靠近);哪些线路需要彼此远离(或靠近);哪些元件需要彼此远离(或靠近);哪些元件要放在PCB的上面,哪些放在下面。佈线设计工程师永远不能抱怨需要给出的资讯太多。资讯永远不嫌多。

接着将分享一项学习经验:大约10年前进行一块多层表面贴电路板的设计案,该电路板的板子两面都有元件。用很多螺钉将板子固定在一个镀金的铝制外壳中(因为有很严格的防震标准)。提供偏置馈通(feedthrough)的引脚穿过板子。该引脚是通过焊接线连接到PCB上的。这是一个很复杂的装置。板子上的一些元件是用于测试设定(SAT)的。但是工程师已经明确规定了这些元件的位置。这些元件都安装在什么地方呢?就在板子的下面。当产品工程师和技术员不得不将整个装置拆开,完成设定后再将它们重新组装的时候,此一手续便显得很复杂。因此必须尽可能减少这样的错误。

位置

正像在PCB中,位置决定一切。将一个电路放在PCB上的什么位置,将其具体的电路元件安装在什么位置,以及其相邻的其他电路是什么,这一切都非常重要。

通常,输入、输出和电源的位置是预先确定好的,但是它们之间的电路就需要发挥各自的创造性了。这就是为什么注意佈线细节将对后续制造产生重大影响的原因。从关键元件的位置入手,根据具体电路和整个PCB来考虑。从一开始就规定关键元件的位置以及讯号的路径有助于确保设计达到预期的工作目标。一次就得到正确的设计可以降低成本和压力,更可因此缩短开发周期。

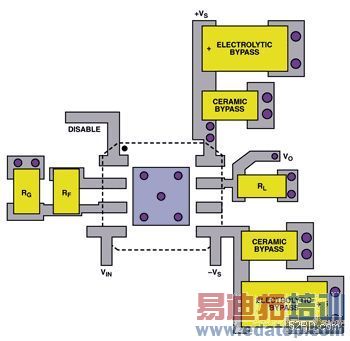

旁路电源

在放大器的电源端设置旁路电源以便降低杂讯是PCB设计过程中一个很重要的方向,包括对高速运算放大器以及其他的高速电路。旁路高速运算放大器有两种常用的配置方法。

■电源端接地

这种方法在大多数情况下都是最有效的,採用多个并联电容器将运算放大器的电源引脚直接接地。一般说来两个并联电容就足够了,但是增加并联电容器可能给某些电路带来益处。

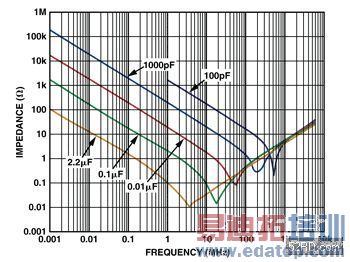

并联不同电容值的电容器有助于确保电源引脚在很宽的频带上出现很低的交流(AC)阻抗。这对于在运算放大器电源抑制比(PSR)衰减频率处尤其重要。该电容器有助于补偿放大器降低的PSR。在许多十倍频程范围内保持低阻抗的接地通路将有助于确保有害的杂讯不能进入运算放大器。(图一)显示採用多个并联电容器的优点。在低频段,大的电容器提供低阻抗的接地通路。但是一旦频率达到了它们自身的谐振频率,电容器的相容性就会减弱,并且逐渐呈现出电感性。这就是为什么採用多个电容器是很重要的原因:当一个电容器的频率回应开始下降时,另一个电容器的频率回应开始其作用,所以能在许多十倍频程范围内保持很低的AC阻抗。

(图一) 电容器的阻抗与频率的关系

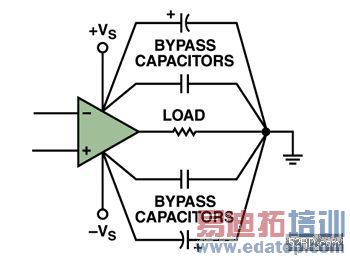

直接从运算放大器的电源引脚入手;具有最小电容值和最小物理尺寸的电容器应当与运算放大器置于PCB的同一面,并且尽可能靠近放大器。电容器的接地端应该用最短的引脚或印制线直接连至接地平面。上述的接地连接应该尽可能靠近放大器的负载端以便减小电源端和接地端之间的干扰。(图二)便显示了这种连接方法。

(图二) 旁路电源端和地的并联电容器

对于次大电容值的电容器应该重复这个过程。最好从0.01μF最小电容值开始放置,并且靠近放置一个2.2μF(或大一点儿)的具有低等效串联电阻(ESR)的电解电容器。採用0508外壳尺寸的0.01μF电容器具有很低的串联电感和优良的高频性能。

■电源端到电源端

另外一种配置方法为採用一个或多个旁路电容跨接在运算放大器的正电源端和负电源端之间。当在电路中配置四个电容器很困难的情况下通常便採用这种方法。它的缺点是电容器的外壳尺寸可能增大,因为电容器两端的电压是单电源旁路方法中电压值的两倍。增大电压就需要提高元件的额定击穿电压,也就是要增大外壳尺寸。但是,这种方法可以改进PSR和失真性能。

因为每种电路和佈线都是不同的,所以电容器的配置、数量和电容值都要根据实际电路的要求而定。

寄生效应

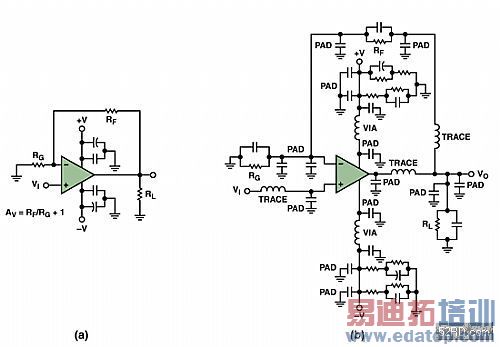

所谓寄生效应,按照字面意思就是那些出现在PCB板中并在电路中大施破坏、令人头痛且原因不明的小故障。它们就是渗入高速电路中隐藏的寄生电容和寄生电感。其中包括由封装引脚和印制线过长所形成的寄生电感;焊盘(pad)到地、焊盘到电源平面和焊盘到印制线之间形成的寄生电容;通孔之间的相互影响,以及许多其他可能的寄生效应。(图三)(a)显示一个典型的同相运算放大器原理图。但是,如果考虑寄生效应的话,同样的电路可能会变成图三(b)那样。

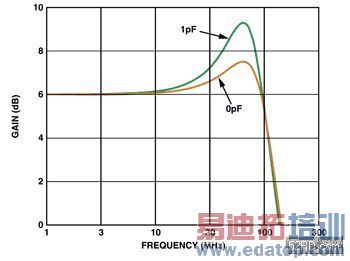

在高速电路中,很小的值就会影响电路的性能。有时候电容值几十个pF的电容就足够了。相关实例:如果在反相输入端仅有1pF的附加寄生电容,它在频率域可以引起差不多2dB的尖脉冲,如(图四)。如果寄生电容足够大的话,它会引起电路的不稳定和震盪。

(图三) 典型的运算放大器电路(a)原设计图与(b)考虑寄生效应后的图

(图四) 由寄生电容引起的附加尖脉冲

当寻找有问题的寄生源时,可能用得着几个计算上述那些寄生电容尺寸的基本公式。(公式一)是计算平行极板电容器的公式,如(图五)。

(公式一)

(1)C表示电容值;

(2)A表示以cm2为单位的极板面积;

(3)k表示PCB材料的相对介电常数;

(4)d表示以cm为单位的极板间距离。

(图五) 两极板间的电容

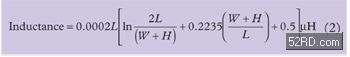

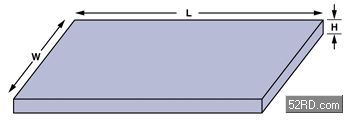

带状电感是另外一种需要考虑的寄生效应,它是由于印制线过长或缺乏接地平面引起的。(公式二)显示出计算印制线电感(Inductance)的公式。可参考(图六)。

(公式二)

(1)W表示印制线宽度;

(2)L表示印制线长度;

(3)H表示印制线的厚度;

(4)全部尺寸都以mm为单位。

(图六) 印制线电感

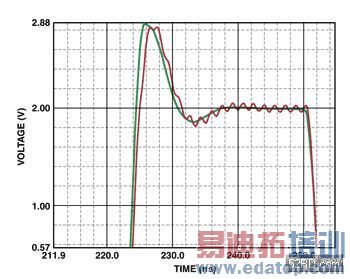

(图七)中的震盪显示高速运算放大器同相输入端长度为2.54cm的印制线的影响。其等效寄生电感为29nH(10-9H),足以造成持续的低压振荡,会持续到整个瞬态回应周期。图七还显示了如何利用接地平面来减小寄生电感的影响。

(图七) 有接地平面和没有接地平面的脉冲回应

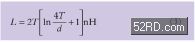

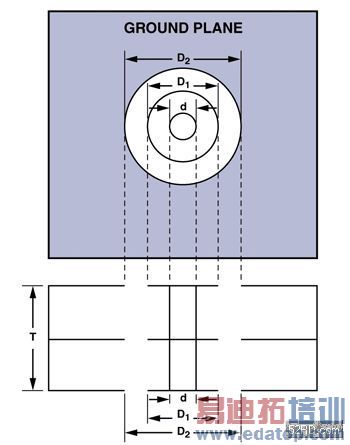

通孔是另外一种寄生源;它们能引起寄生电感和寄生电容。(公式三)是计算寄生电感的公式,请参考(图八)。

(公式三)

(1)T表示PCB的厚度;

(2)d表示以cm为单位的通孔直径。

(图八) 通孔尺寸

(公式四)示出了如何计算图八中通孔引起的寄生电容值。

(公式四)

εr表示PCB材料的相对磁导率。T表示PCB的厚度。D1表示环绕通孔的焊盘直径。D2表示接地平面中隔离孔的直径。所有尺寸均以cm为单位。在一块0.157 cm厚的PCB上一个通孔就可以增加1.2nH的寄生电感和0.5pF的寄生电容;这就是为什么在给PCB佈线时一定要时刻保持警觉的原因,要将寄生效应的影响降至最小。

接地平面

实际上需要讨论的内容远不止这些,但是本文会重点强调一些关键特性并鼓励工程师进一步探讨这些问题。本文文末并将列出相关的参考资料。

接地平面可担负起公共基准电压的作用,提供遮罩、能够散热和减小寄生电感(但它也会增加寄生电容)的功能。虽然使用接地平面有许多好处,但是在实现时也必须小心,因为它对能够做的和不能够做的都有一些限制。

理想情况下,PCB有一层应该专门用作接地平面。这样当整个平面不被破坏时才会产生最好的结果。千万不要挪用此专用层中接地平面的区域用于连接其他信号。由于接地平面可以消除导体和接地平面之间的磁场,所以可以减小印制线电感。如果破坏接地平面的某个区域,会为接地平面上面或下面的印制线带来意想不到的寄生电感。

因为接地平面通常具有很大的表面积和横截面积,所以使接地平面的电阻保持最小值。在低频段,电流会选择电阻最小的路径,但是在高频段,电流会选择阻抗最小的路径。

然而也有例外,有时候小的接地平面会更好。如果将接地平面从输入或者输出焊盘下挪开,高速运算放大器将会更顺利地工作。因为在输入端的接地平面引入的寄生电容,增加了运算放大器的输入电容,减小了相位裕量,因而造成不稳定性。正如在上文寄生效应讨论中所看到的,运算放大器输入端1pF的电容能引起很明显的尖脉冲。输出端的容性负载,包括寄生的容性负载,造成了反馈环路中的极点。这会降低相位裕量并造成电路变得不稳定。

如果有可能的话,模拟电路和数字电路,包括各自的接地平面应该分开。快速的上升会造成电流毛刺流入接地平面。这些快速的电流毛刺引起的杂讯会破坏模拟性能。模拟接地和数字接地(以及电源)应该被连接到一个共用的接地点以便降低迴圈流动的数字和模拟接地电流和噪音。

在高频段,必须考虑一种称为趋肤效应的现象。趋肤效应会引起电流流向导线的外表面,结果会使得导线的横截面变窄,因此使直流(DC)电阻增大。虽然趋肤效应超出了本文讨论的范围,这里还是给出铜线中趋肤深度(Skin Depth)的一个很好的近似公式(以cm为单位):

(公式五)

低灵敏度的电镀金属有助于减小趋肤效应。

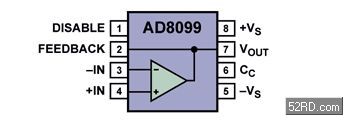

封装

运算放大器通常採用不同的封装形式。所选的封装会影响放大器的高频性能。主要的影响包括寄生效应(前面提到的)和信号路径。本文接着将集中讨论放大器的路径输入、输出和电源。

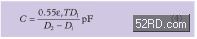

(图九)显示採用SOIC封装图九(a)和SOT-23封装图九(b)的运算放大器之间的佈线区别。每种封装都有它自身的一些问题。重点看(图九a),仔细观察反馈路径就发现有多种方法连接反馈。最重要的是保证印制线长度最短。反馈路径中的寄生电感会引起振铃和过冲。在图九(a)和图九(b)中,环绕放大器连接反馈路径。图九(c)显示了另外一种方法,在SOIC封装下面连接反馈路径,这样就减小了反馈路径的长度。每种方法都有细微的差别。第一种方法会导致印制线过长,会增大串联电感。第二种方法採用了通孔,会引起寄生电容和寄生电感。在给PCB佈线时必须要考虑这些寄生效应的影响及其隐含的问题。SOT-23佈线差几乎是最理想的:反馈印制线长度最短,而且很少利用通孔;负载和旁路电容从很短的路径返回到相同的地线连接;正电源端的电容(图九(b)中未示出)直接放在PCB的背面的负电源电容的下面。

(图九) 同一运算放大器电路的佈线区别:(a)SOIC封装;(b)SOT-23封装;(c)在PCB下面採用RF的SOIC封装

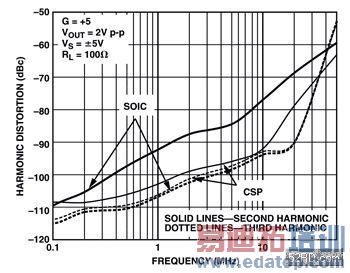

■低失真放大器的引脚排列

採用低失真引脚排列的一些运算放大器,有助于消除上面提及的两个问题;而且它还提高了其他两个重要方面的性能。LFCSP的低失真引脚排列,如(图十)所示,将传统运算放大器的引脚排列按着逆时针方向移动一个引脚,并且增加了一个输出引脚作为专用的反馈引脚。

(图十) 採用低失真引脚排列的运算放大器

低失真引脚排列允许输出引脚(专用反馈引脚)和反相输入引脚之间可以靠近连接,如(图十一)所示。这样极大地简化和改善了佈线。

(图十一) AD8045低失真运算放大器的PCB佈线

这种引脚排列还有一个好处就是降低了二次谐波失真。传统运算放大器的引脚配置中引起二次谐波失真的一个原因是同相输入和负电源引脚之间的耦合作用。LFCSP封装的低失真引脚排列消除了这种耦合所以大大地降低了二次谐波失真;在有些情况下最多可降低14dB。(图十二)显示了採用SOIC封装和LFCSP封装失真性能的差别。

这种封装还有一个好处:功耗低。LFCSP封装有一个裸露的焊盘,它降低了封装的热阻,进而改善θJA值约40%。因为降低了热阻,所以降低了元件的工作温度,也就相当于提高可靠性。

(图十二) 不同封装失真性能对比:相同的运算放大器採用SOIC和LFCSP封装

佈线和遮罩

PCB上存在各种各样的类比和数字信号,包括从高到低的电压或电流,从DC到GHz频率范围。想保证这些讯号不相互干扰是非常困难的。

回顾前文「谁都别信」部分的建议,最关键的是预先思考并且为了如何处理PCB上的信号而拟定出一个计划。重要的是注意哪些信号是敏感信号并且确定必须採取何种措施来保证讯号的完整性。接地平面为电信号提供一个公共参考点,也可以用于遮罩。如果需要进行信号隔离,首先应该在讯号印制线之间留出物理距离。下面是一些值得借镜的实做经验:

●减小同一PCB中长并联线的长度和讯号印制线间的接近程度,可以降低电感耦合;

●减小相邻层的长印制线长度可以防止电容耦合;

●需要高隔离度的信号印制线应该走不同的层,而且如果它们无法完全隔离的话,应该走正交印制线,并且将接地平面置于它们之间。正交佈线可以将电容耦合减至最小,而且地线会形成一种电遮罩。在构成控制阻抗印制线时可以採用这种方法。

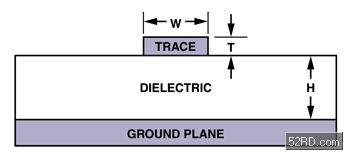

高频(RF)信号通常在控制阻抗印制线上流动。就是说,该印制线保持一种特征阻抗,例如50Ω(RF应用中的典型值)。两种最常见的控制阻抗印制线、微带线和带状线都可以达到类似的效果,但是实现的方法不同。

微带控制阻抗印制线,如(图十三)所示,可以用在PCB的任意一面;它直接採用其下面的接地平面作为其参考平面。

(图十三) 微带传输线

(公式六)可以用于计算一块FR4板的特徵阻抗。

(公式六)

(1)H表示从接地平面到信号印制线之间的距离;

(2)W表示印制线宽度;

(3)T表示印制线厚度;

(4)全部尺寸均以密耳(mils)(10-3英寸)为单位;

(5)εr表示PCB材料的介电常数。

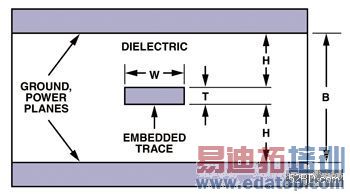

带状控制阻抗印制线(图十四)採用了两层接地平面,信号印制线夹在其中。这种方法使用了较多的印制线,需要的PCB层数更多,对电介质厚度变化敏感,而且成本更高,所以通常只用于要求严格的应用中。

(图十四) 带状控制阻抗印制线

用于带状线的特征阻抗计算公式如(公式七)所示:

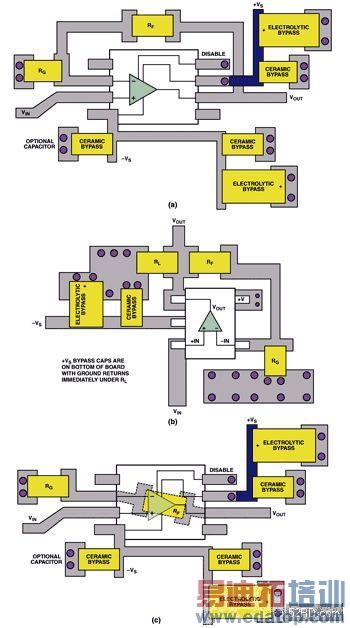

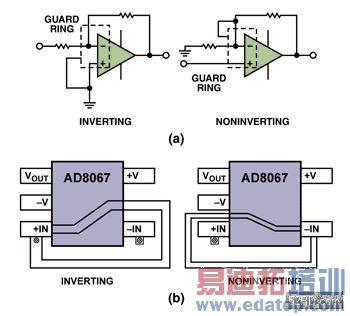

(公式七)保护环,或者称隔离环,是运算放大器常用的另一种遮罩方法,它用于防止寄生电流进入敏感结点。其基本原理很简单,用一条保护导线将敏感结点完全包围起来,导线保持或者迫使它保持(低阻抗)与敏感结点相同的电势,因此使吸收的寄生电流远离了敏感结点。(图十五)(a)显示了用于运算放大器反相配置和同相配置中保护环的原理图。图十五(b)则显示用于SOT-23-5封装中两种保护环的典型佈线方法。

(图十五) 保护环。(a)反相和同相工作;(b)SOT-23-5封装。

还有很多其他的遮罩和佈线方法。欲获得有关这个问题和上述其他题目的更多资讯,建议读者可阅读下列参考文献。

结论

高水准的PCB布线对成功的运算放大器电路设计是很重要的,尤其是对高速电路。一个良好的原理图是成功佈线的基础;电路设计工程师和佈线设计工程师之间的紧密配合是根本,尤其是关于元件和接线的位置问题。需要考虑的问题包括旁路电源,减小寄生效应、采用接地平面、运算放大器封装的影响,以及布线和遮罩的方法。