- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

通电即用PLD对系统设计的影响

系统设计的发展趋势

随着系统越来越复杂,降低成本和缩短设计周期的压力使得系统设计向着高效率、模组化和简洁的方向发展。当需要在应用中实现某项功能时,设计人员通常会察看市场有否适合的解决方案,能满足其系统需要。在筛选出几个能满足其设计需要的解决方案后,设计人员便会根据方案的成本和设计的简洁性选行选择。

讲求缩短初始化时间的电路和应用

一般系统在通电后,系统元件必需进行初始化并执行系统的监管任务,例如设置微处理器环境、进行关键的系统啓动任务,以及在通电电压攀升过程中控制运行,直到系统电压达到稳定。在复杂的系统中,系统的监管任务可能包括配置存储器块;系统初始化任务可能包括微控制器位址匯流排解码、针对多系统元件的各种时钟进行合成和分配、分配重定或使能信号、管理匯流排活动传输以防止资料错误,以及完成时序关键的任务,将处理器的初始化时间减至最少。

有些应用要求系统能快速完成初始化,以便即时进入操作状态。这类应用包括执行关键操作的医疗和工业应用,如生命救助设备。採用电池供电且经常要通电和关电的可携带型设备也需要缩短初始化时间,这样才能提高产品的可用性。其他要求在通电后即时进入运行状态的关键应用还包括汽车引擎啓动控制及军事应用如导弹发射啓动控制。

通电即用元件

系统往往由多个相互关联的元件组成,而设计人员的任务就是要确保所有这些元件能一起协同工作。在系统的关键环节上选择通电即用元件,对实现高效的系统操作非常重要。如图 1 所示,通电即用元件在系统电压达到其额定工作电压的最低水平前 (称为通电阶段) 已能工作;相反其他元件只可在通电完成后才能工作。举例说,选择带有综合锁相环 (PLL) 电路的通电即行元件来进行时钟分配任务,不但能减少整体系统啓动时间,还无需採用独立的 PLL 来进行这个任务。在关键系统的啓动环节上选择通电即行元件能大幅减少整体应用系统的啓动时间、成本、尺寸及设计复杂性。

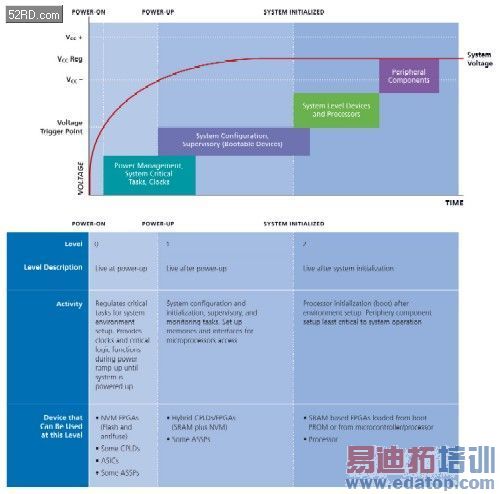

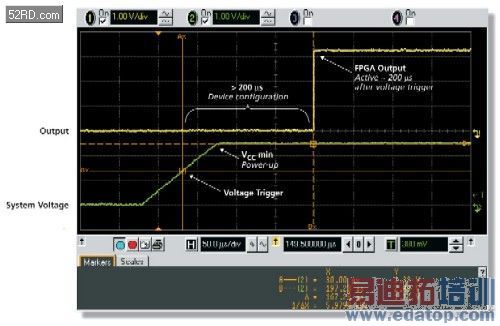

图1 所示为典型的系统通电运行过程,由加上电压 (打开电源开关) 的瞬间到电压升到系统工作电压的下限,

直到最终完成初始化。为了简单起见,这分类採用了单一系统电压来反映系统运作状况。

在加上电压后 (即系统首次接通电源),电压开始攀升。

可编程逻辑元件选择

可编程逻辑元件由于具有设计时间短、系统内编程 (ISP) 功能、使用方便和快速构建原型等优势,因此其应用经歷了大幅增长。转用较先进的科技可以大幅削减可编程逻辑元件的成本,而可编程逻辑元件已在系统设计中开始逐步取代通电即行的 ASIC 元件。

若系统需要採用可编程逻辑元件,设计人员不应忽略所选可编程逻辑元件的通电即行功能,这个决定可能会无谓地增加系统的尺寸和成本。可编程逻辑元件需要配置存储器来啓动元件的工作。市面上现有不同的技术可以配置可编程逻辑元件解决方案。以非挥发性存储器技术为基础的可编程逻辑元件如 Flash、EEPROM 和反熔丝,会将其配置存储于晶片中。这样便无需下载配置,使到可编程逻辑元件可以好像 ASSP (专用标准产品) 和 ASIC 那样直接工作。

其他技术如以 SRAM 为基础的可编程逻辑元件,在每次上电时都会从睡眠状态中被唤醒,并需要从外部的非挥发性存储器元件中下载配置。此外,还有一些混合式 SRAM 元件採用 SRAM FPGA 结构及非挥发性的晶片配置存储器,这些混合式 FPGA 必须在每次通电时于内部完成配置载入。只有在配置载入完成后,才能根据客户的应用程式进行工作。而在每次关电或意外断电后,混合式元件会丢失配置,需要在下次通电时再重新载入。

通电即用可编程逻辑元件能简化设计,有利于完成系统初始化、设置系统环境及执行微控制器及其他系统操作的准备工作,因此能够缩短系统的初始化时间。这些可编程逻辑元件还能完成其他设置工作,如配置系统存储器、为系统板卡上的部件提供稳定可靠的通电顺序、向各元件分配时钟,以及管理介面和匯流排;使到系统的设计更加有效、使用的元件数目更少及功耗更低。

通电即行元件分类

以Actel判别系统中半导体元件通电行为的元件分类系统为例,这个分类系统可协助设计人员选择合适的可编程逻辑元件,并以系统在通电阶段的运行情况和功能性作为考虑根据。

触发电压较低的系统元件能较快地开始工作,并有助于完成系统的初始化、功率管理和关键系统任务,以及提供时钟和重定信号。能在系统加上电压到完成上电 (电压已达到系统工作电压的下限及变稳定) 期间工作的元件被视为 0 级通电即用 (LAPU) 元件。满足 0 级 LAPU 的元件包括非挥发性记忆体 (NVM) PLD、ASIC 和一些 ASSP。需要下载配置或更高的系统电压下限才能工作的元件被划分为 1 级 LAPU 元件,只可在通电阶段完成后才能工作。

这些元件一般是 ASSP 或其他,能协助完成存储器配置或与主处理器介面。系统环境一旦完成初始化,而且时钟、重定、介面和记忆体都准备就绪,处理器(MCU/CPU) 便会开始工作并存取所需的外设。这类元件支援 2 级 LAPU,因为它们仅在系统初始化之后才能工作,即系统元件已经工作及处理器开始运行时。

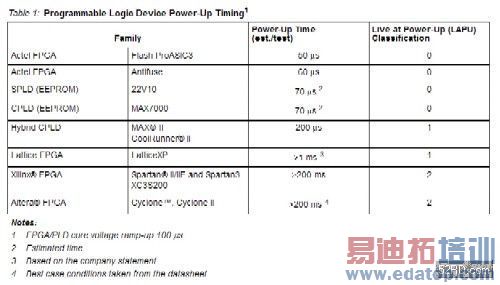

表 1 所示为针对几种可编程逻辑元件进行的实验室测试结果和产品指标资料分析,

以确定产品的实际上电时序。所获得的资料支援不同技术的 LAPU 分类。

注意只有 Flash 和反熔丝非挥发性 FPGA 以及拥有 EEPROM 技术的 SPLD,才是唯一获配为 0 级 LAPU。

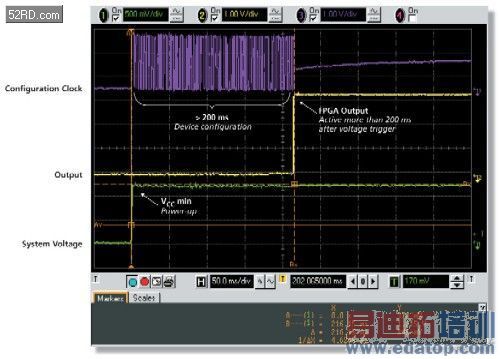

图 2 所示为 NVM (反熔丝) FPGA AX250 (Actel 的 Axcelerator®) 在系统加电前的 I/O 运行。

SRAM FPGA XC3S200 (Xilinx Spartan-3) 需要 200 ms 以上才能载入配置及开始 I/O 操作。

NVM FPGA 被配分为 0 级 LAPU,比较被配分为 2 级 LAPU 的 SRAM FPGA 速度通常快达 4000 倍。

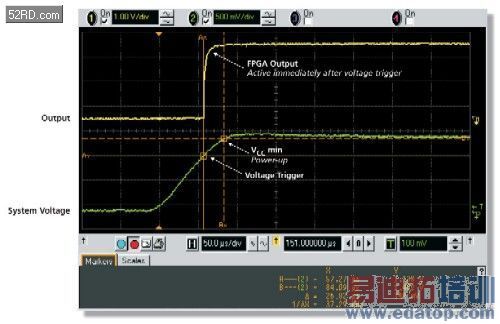

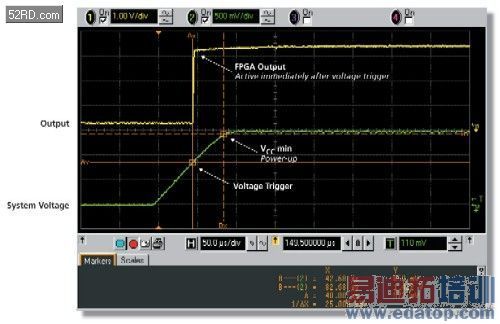

图 3 所示为 NVM (Flash) FPGA A3PE600 (Actel 的 ProASIC3/E) 在系统上电前的 I/O 运行。

混合式 SRAM FPGA EPM1270 (Altera 的 MAX-II) 需要 200 µs 以上才能载入配置及开始工作。

混合式 (SRAM 加 NVM) FPGA 在每次上电时都必须进行配置,并在上电后达 1 级 LAPU。Flash FPGA

能达到 0 级 LAPU 要求,虽然升压时间稍长,但一般也比混合式 SRAM FPGA 快 20 到 40 倍。

在不同的升压时间下比较 NVM FPGA 和 SRAM FPGA 进入工作状态所需的时间,发现 NVM FPGA 在所有升压速率下都明显较 SRAM FPGA 优胜。在不同的升压时间下比较 NVM FPGA 和 SRAM 混合式 FPGA 进入工作状态对升压时间的比率,发现 NVM FPGA 在所有升压速率下都明显比 SRAM FPGA 更快进入工作状态。

所测试的非挥发性 FPGA 始终都能够在上电前工作,而且从加电到工作所需的时间与元件的逻辑尺寸无关。另一方面,SRAM 和混合式元件从加电到工作所需的时间较长,因为元件配置的大小与元件的逻辑密度相关。因此,NVM 和 SRAM 之间的分别在高密度的元件中更为明显。根据所定义的 LAPU 分类和测试的元件,0 级 LAPU NVM FPGA 的上电速度比 SRAM FPGA 快 4000 倍,以及比混合式 FPGA 快 20 到 40 倍。

系统功能差别

可编程逻辑元件所支援的 LAPU 级别会影响系统的构架,在需要从外部 Flash 载入配置的 SRAM FPGA 设备中,系统要等数百毫秒才能进入工作状态,因为SRAM 元件需要花一定时间来载入配置及啓动操作。採用 NVM FPGA 的系统意味着在 50 µs (不是数百毫秒) 后就可开始工作,因为 NVM FPGA 在通电时无需进行配置。

0 级 LAPU 节省成本

除了能简化系统设计外,LAPU 功能还有助于减少板卡上的元件数目、降低功耗、减少系统整体成本及提高系统可靠性。若採用以 SRAM 为基础的 FPGA,可能需要增加不少额外的电路。除导引PROM 和/或用于存放不安全配置代码的额外存储器外,还需要通电即行 CPLD 以便进行系统配置和执行监管工作。系统上电后也需要产生时钟和重定信号,以协助完成板卡上的部件初始化。这些问题将会增加系统设计的复杂性和成本,同时拖慢产品的开发进度。

採用非挥发性 FPGA 便能简化板卡和系统设计,并且降低成本 (见表 2)。採用 2 级 LAPU SRAM FPGA 的平均系统成本可能是採用 0 级 LAPU 非挥发性 FPGA 的 3 倍。

结论

0 级 LAPU 的 FPGA 能够满足那些要求初始化时间短、终端用户在通电后即能享用产品功能的应用设计需求。这类 FPGA 使到系统在通电时就能存取微控制器。非挥发性 FPGA 能执行微处理器位址解码,而 FPGA 中的 PLL 能立即进入操作状态。此举能省去外部 CPLD 及额外的晶振和重定处理电路,令到系统设计更加简化、效率更高。0 级 LAPU 的 FPGA 同时能通过减少元件数来降低整体拥有成本,使到库存下降和最终产品的可靠性提高,因为印刷电路板上少一些部件,故障出错的机会也会减少。