- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

可携式电脑之耳机驱动电路改进

使用者对可携式电脑的高品质音频愈来愈要求,对音频电路的设计者来说,主要的挑战是设计出能够与ASIC、处理器以及直流直流转换器等共存的高效能、低噪音模拟线路,而在声音播放结构中的关键,即是耳机驱动电路,本文将提出此一电路的改进之道。

不管是以笔记型电脑或PDA形式表现,可携式电脑基本上提供给实现高品质噪音的环境是相当严苛的,不管是高噪音的电源、有限的空间或者是与数字电路共用的电源与接地点,都对提供音乐播放、语音录制以及其他相关功能的模拟与混合信号电路带来相当严格的要求,同时使用者对高品质音频的期待也与希望拥有最长电池使用时间相冲突,因为它需要将没有在使用中的电路电源暂时移除。

对音频电路的设计者来说,主要的挑战是设计出能够与ASIC、处理器以及直流直流转换器等共存的高效能、低噪音模拟线路,而在传统的声音播放结构中这些问题只会影响一个元件,它就是耳机驱动电路。

耳机驱动电路之瓶颈与改进

笔记型电脑的耳机输出必须要能够推动一个低阻抗的负载(通常为32Ω,有时可能低到16Ω),信号位准则大约在1Vrms,同时还要维持音源的动态范围,乍看之下好像是个简单的工作,但仔细思考后会发现有几个困难需要解决:

● 耳机输出必须要能够在单一电源的情况下维持相同的动态范围,而电源通常是透过一个经直流直流转换器(DC/DC Converter),同时与高速数字电路共用的电源来取得。

● 以这些电路中的信号位准与负载阻抗考虑,由电源所抽取的最高电流可能高达90mA。

● 当关闭电源或者是耳机驱动电路时,必须要避免卡嗒声或转换所造成的声响。

■电源噪音的抑制

要达到合理的信号噪音比(SNR),我们必须抑制耳机放大器输出端的电源噪音效应,而耳机驱动电路的电源拒斥设计则是达成这个目标的基本要求,例如CD或DVD之类的动态范围可能会超过90dB,假设有在音频电路电源上有一个100mV的噪音,而且大部份的频谱都存在音频频带上,那么我们就必须将这个噪音在耳机输出端降低到30μV以维持90dB的动态范围,也就是说,耳机驱动电路的PSRR必须在目标频率上要超过70dB。

要在整个音频频带上达成这样的电源拒斥效果,我们就必须採用精心设计的作法,特别是放大器在目标频率范围内对电源噪音的抑制,由于在大部份运算放大器的资料规格书中,我们可以看到PSRR通常在直流时相当高,但是会随着频率的增加大幅滑落,大约在-20dB/decade,在20KHz时,某些元件的PSRR甚至还会低于40dB。

有些直流直流转换器会在音频频谱的顶端产生较高的噪音,虽然位在这些频率的噪音比较不会被听到,但是在耳机输出端所造成的噪音还是达到可以测量出来的程度。请注意大部份音频DAC或CODEC的规格书中都会有使用者较少注意的PSRR规格相关的内建耳机驱动电路,通常如果提供的话,它会列在电源特性底下的一个单一项目,而不是一个PSRR相对于频率的曲线。

由于大部份的耳机放大器缺乏足够的PSRR,因此我们可以加入一个低压降稳压器(LDO, Low-dropout)来维持耳机放大器电源的稳定,例如我们要在笔记型电脑音频输出端达到足够的电源杂讯抑制效果的话,由于+5V还是音频电路最常见的电源,因此部份的连接点还是会调节到4.7V左右。

■喀撘声与爆裂声的抑制

喀撘声与爆裂声的抑制通常是用来描述晶片能够在静音或者是开关机时发生的突然间或不连续转变所造成的杂音降到最低,这个动作基本上不容易由输出驱动电路达成,因为没有下一级电路可以被静音来遮蔽快速发生的异常状况,如果耳机是插入时,那么不管是採用什么样的驱动电路,都会造成或改变音频系统转换效能的转变。

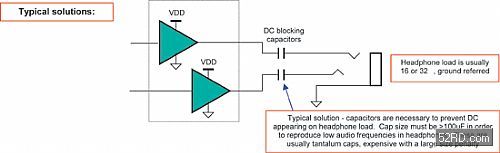

耳机驱动线路通常是由单电源所驱动,同时透过一个大电容将输出交流偶合到耳机插座上,请见(图一),这样的安排可以避免在耳机上产生直流电压,造成耳机驱动电路的损坏。在运作时,这个遮蔽电容上会有一个电压,原因是电容器的耳机端是在地电位,而放大器输出端则会被偏压到大约是电源的一半,在电源加入时,这个电容必须要已经充电到它的工作电压,但是它所允许进入的电流必须要流经负载,也就是耳机内的声音线圈,那么要如何才能避免这个电流产生的有声信号呢?

图一 包含了一个串连电容的耳机驱动电路

有些设计在放大器输出採用JFET与离散元件来抑制这个充电电流,其他还有利用RC电路的时间常数来延缓启动转换,因而可以透过降低这些干扰杂音的频率来去除杂音,而市面上也有产品採用了背对背(back-to-back)的指数型升压(S-形)来进一步抑制由电源启动造成的爆裂音,和RC指数型方式不同,这样的做法不会造成电压改变(dv/dt)的瞬间中断。

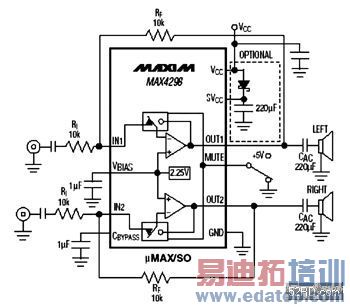

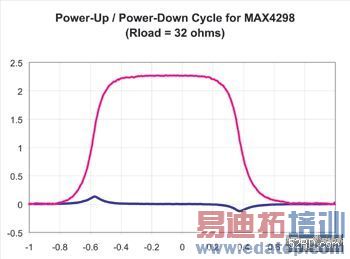

事实上在电源关闭过程中的转换问题更多,在没有电源的情况下,放大器如何控制输出电容的放电功能呢?一个可行的做法是提供给耳机放大器一个会在运作时利用电源充电的电容做为备份电源,可以在主电源移除后提供给耳机放大器足够的能量以便能够平顺地处理电源关闭的过程,这项技术(图二)的整合应用产生了如(图三)的波形。

图二 典型耳机放大器应用

图三 提供耳机放大器备份电源电容之波形效应

註:这个波形描绘了图一电路加上VCC(t = -1s)与移除VCC(t = 0s)时的效应,请注意耳机放大器输出(图中上方波形)的S型转换会在负载上(图中下方波形)产生平顺且有限干扰的输出,这个可控制的输出限制了启动转换到低音频的情况,比较不会被耳朵所察觉。

从图三中我们可以清楚地看出,只要加入一些简单的元件就可以让放大器达到一个与平顺启动过程相同的可控制平顺电源关闭转换,这项技术使用了第二个VCC接脚(SVCC),在主VCC电源存在时,外部的肖特基二极管会对存储电容充电,而在电源移除后,放大器则会依以下的程序动作:

● 将音频输出静音。

● 立体声放大器转变成低静态电流模式,并由SVCC接脚取得电源。

● 输出偏压逐渐缓慢回到地电位,透过一个可以镜射电源启动波形静射的S型设计来消除电压变动(dV/dt)杂音。

● 存储电容接着将逐渐放电,但是输出电压已达地电位,因此当SVCC电源逐渐消失时输出转变就可以被忽略。

■另一种解决方式

以上的解决方案努力地解决了一个行销部门可能不太重视的无形功能,因此一个比较理想的作法是完全省去输出电容,因此能够完全不需考虑耳机声音线圈上的充放电效应,例如这个电容可以透过将耳机驱动电路以直流偶合的方式去除,拥有零电压输出偏压,同时提供给放大器双极性的电源。由于大部份採用电池作为主要电源的设计都有单电源的限制,因此设计者可以有几种选择,其中一种作法是使用第三个放大器来将耳机偏压回復到电源中间点,因此就可以产生一个虚拟的0V输出偏压。由于主立体声放大器也偏压到电压中间点,可以省去直流偶合电容,因此,第三个放大器必须要能够由两个主放大器吸取或提供电流,同时要能够承受由接入耳机插座所带来的ESD放电效应(耳机接头必须要和机壳隔离)。

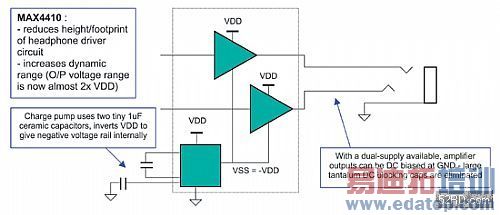

另一种选择则是由所提供的正电源产生专用的负电源,或者採用能够方便地产生负电源的独立元件,请见(图四),这样的作法可以让ESD与接地不再造成问题,同时所得到的额外电压范围也可以让输出电压的峰对峰(peak-to-peak)范围几乎倍增,这是在3V或更低电源运作下相当有用的功能。

图四 由正电源产生专用的负电源来让ESD与接地不成问题

註:为了让放大器能够使用双电源,内建的充电泵会将正电源电压反向,因此再也不需串连电容,但却必须提供充电泵小型陶瓷电容以便将电路板面积缩到最小。

■进一步的限制

在产品推出之前,设计的电路通常需要经过不断的折冲,例如因为要达成ESD的要求可能会在在耳机驱动电路与耳机插座之间加上铁氧磁芯或其他EMC测量,由于这些元件可能会对音频造成重大影响,带来串音干扰问题以及输出功率的损失,不过透过仔细的设计以及Kelvin感测(Kelvin-sensing)技术,将能够重新取得相当好的音讯效能。

由耳机所送回的电流也应该加以考量,在电源接近100mA时,地接面或PCB板上铜线的有限阻抗也会造成大幅的IR压降,同样地,在与直流直流转换器共用接地点时也会造成SNR的损失,在这方面我们可以透过加入专用的回返路径或者是铜填充(copper fill)可以帮助解决这个问题。

数字化的未来?

除非数字化耳机开始大量生产,否则推动耳机插座的电路还是必须为採用模拟设计,这个现象是否会持续?Class D形式的设计会在放大器的输出维持一个数字音频通道,虽然必须加入滤波元件以维护效率并降低EMI,PSRR以及喀撘与爆裂声抑制还是会造成效能的损失,因此基本上在可见的未来类比硬件设计工程师还是相当地重要。

上一篇:量测基础篇-频宽、取样速率及奈奎斯特定理

下一篇:可延长电池动作时间的电源电路