- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB导线设计技术(中)

本文将接续介绍电源与功率电路基板,以及数字电路基板导线设计。

宽频与高频电路基板导线设计

a.输入阻抗1MHz,平滑性(flatness)50MHz的OP增幅器电路基板

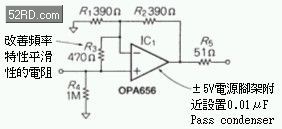

图26是由FET输入的高速OP增幅器OPA656构成的高输入阻抗OP增幅电路,它的gain取决于R1、R2,本电路图的电路定数为2倍。

此外为改善平滑性特别追加设置可以加大噪音gain,抑制gain-频率特性高频领域时峰值的R3。

图26 高输入阻抗的宽频OP增幅电路

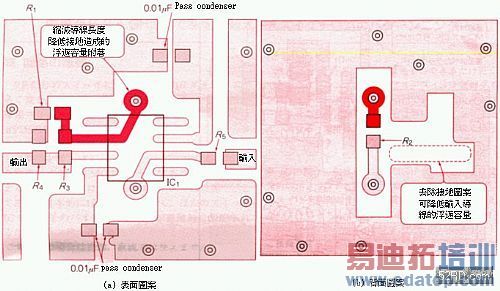

图27是高输入阻抗OP增幅器的电路基板图案。降低高速OP增幅器反相输入端子与接地之间的浮游容量非常重要,所以本电路的浮游容量设计目标低于0.5pF。

如果上述部位附着大浮游容量的话,会成为高频领域的频率特性产生峰值的原因,严重时频率甚至会因为feedback阻抗与浮游容量,造成feedback信号的位相延迟,最后导致频率特性产生波动现象。

此外高输入阻抗OP增幅器输入部位的浮游容量也逐渐成为问题,图27的电路基板图案的非反相输入端子部位无full ground设计,如果有外部噪音干扰之虞时,接地可设计成网格状(mesh)。

图28是根据图26制成的OP增幅器Gain-频率特性测试结果,由图可知即使接近50MHz频率特性非常平滑,-3dB cutoff频率大约是133MHz。

图27 高输出入阻抗OP增幅器的电路基板图案

图28 根据图26制成的OP增幅器Gain-频率

b. 可发挥50MH z~6GHz宽频增幅特性的电路基板图案

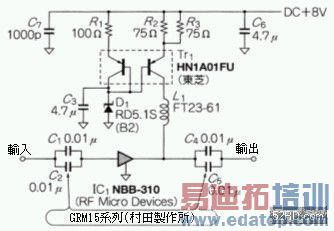

图29是由单晶片微波(MMIC: Monolithic Micro wave device)积体电路NBB-310(RFMicro Devices)构成的频宽50MHz~6GHz宽频高频增幅器,NBB-310高频元件采用AlGaAs HBT制程制作,因此可靠性相当高。

使用MMIC的增幅器时,必需搭配适合的电路基板图案阻抗与元件,例如耦合电容、高频扼流圈(choke)、线圈(coil)(以下简称为RFC)时,才能发挥元件具有的功能。如NBB-310技术资料的记载,偏压(bias)电流只需利用电阻与RFC即可,不过本电路使用复合型电晶体构成的current mirror电路,加上 NBB-310输出脚架的直流电压Level,会随着高频输入电力Level的变化,使用上述电阻与RFC简易偏压电路的话,输入电力变时输出脚架的直流电压会降低,NBB-310可能会有过电流流动之虞,所以偏压电路使用current mirror电路,藉此防止发生过电流现象。

图29 频宽50MHz~6GHz宽频高频增幅器的电路

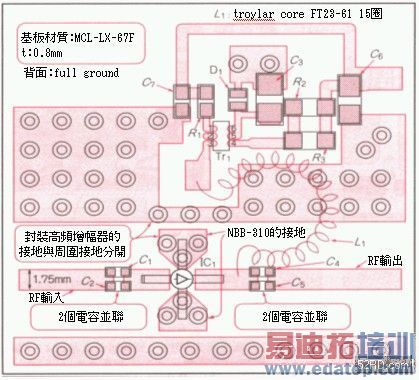

频率超过2~3GHz必需谨慎选择印刷电路基板的材质,基本上不可使用传统FR4玻璃环氧树脂,因此无铅且高频特性与FR4玻璃环氧树脂相同的高Tg玻璃环氧树脂使用可能性大幅增加。一般而言高频电路通常会选用高频用低tan的基板材质,此外为抑制周围温湿度造成高频特性变动,因此必需将基板的温湿度一併列入考虑。图30是频宽50MHz~6GHz宽频高频增幅器的电路基板图案,如图所示micro strip line上方的2个耦合电容C1、C2与C4、C5, 并联设在线路端缘(edge)可以改善insertion loss与return loss等高频特性。

图30 频宽50MHz~6GHz宽频高频增幅器的电路基板图案

频率超过GHz等级时,电容器的高频特性随着厂牌出现极大差异,虽然指定厂牌对资材采购单位相当困扰,不过它是OP增幅性能上重要元件之一,重视应用性能时就不应该妥协让步。

封装NBB-310的接地面必需与周围接地面分离,如此才能够防止在NBB-310接地面流动的接地电流迷走在full ground面上,这种技巧经常被应用在改善OP增幅器的绝缘特性。

自制线圈时使用FT23-61 type的troy dull core,与直径ψ0.3polyurethane,靠近NBB-310端紧密绕卷5圈,接着均匀粗绕卷10圈;如果使用市售的线圈必需透过测试寻找特性符合要求的产品,笔者认为若使用WD0200A(冈谷电机)可以充分发挥NBB-310的性能。

c. 可以从直流切换成2.5GHz的RF切换电路

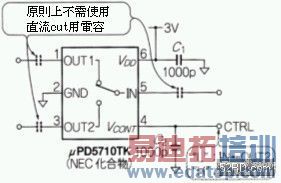

以往RF信号切换开关大多使用PIN二极管(diode),目前GaAs与CMOS专用IC已经成为市场主流,此处以μPD5710TK为例,介绍可以切换直流~2.5GHz的宽频切换电路(图31)。

图31 可从直流切换成2.5GHz的RF切换电路

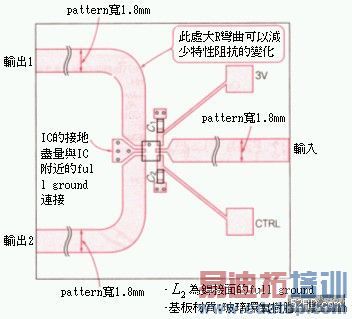

图中的μPD5710TK采用CMOS制程制作,点线表示直流cut用电容,其它切换IC的端子偏压(bias)Level是以直流性定义,所以几乎都是用电容直流cut,不过本电路无法使用直流电。图32是RF切换电路基板图案,图案宽度为1.8mm如此便可以成为Z0=50Ω的micro strip line的传输线路,电路基板厚度t=1.0mm。Layout基板时尽量让切换IC的的接地在附近流入背面的端子接地,如此切换控制线在端子附近强制性控制阻抗(impedance),所以没有长度与宽度等限制。

图32 可从直流切换成2.5GHz的RF切换电路基板图案

为避免切换控制端子影响IC的动作,因此作业上必需谨慎处理。图31的电容C1、C2与接地作交流性连接,可以降低电容对连接控制电路与电源图案的影响(图案成为等价性线圈,图案长度与频率关系的阻抗,从0到无限大巨大变动)。此外电容本身具备共振频率,所以本电路采用高自我共振频率与高定数电容,晶片电容一般都在100pF~1000pF左右。

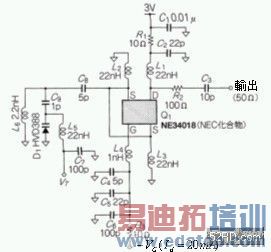

d. 4GHz VCO的电路基板图案

图33是4GHz为中心可作500MHz宽频振荡的VCO(Voltage Controlled Oscillator)电路,外观上看似可洱必兹基本电路,不过却无可洱必兹电路必要的C-C-L结构,然而本电路却显示负性阻抗而且还可以作振荡动作,一般的VCO为了要减轻负载,通常都会设置缓冲器(buffer),不过本电路50Ω负载时仍拥有良好的负性阻抗,所以直接连接至50Ω传输线路。

图33 4GHz为中心可作500MHz宽频振荡的VCO电路

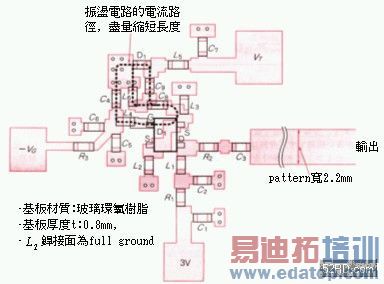

图34是电路基板图案。VCO的基板图案重点必需考虑决定振荡频率的元件,以及振荡电晶体的电流流动特性,依此才能设计最短的图案长度。如上所述电路50Ω负载时显示良好的负性阻抗,所以输出直接连接至Z0=50Ω的micro strip line的传输线路,此外控制电压端子Vr利用外部PLL电路以模拟电压控制,所以用C7作高频性降至ground,避免受到电路基板布线的影响。

图34 4GHz为中心可作500MHz宽频振荡的VCO电路基板图案

Q1、L6、L4、D1决定振荡频率,所以设计图案时必需考虑贯穿这些元件的电路电流路径。图34中的虚线表示电路电流路径。

接地采用via hole连接到L2,虽然这种连接方式属于full ground不过路径却非常短,此外via hole设计必需避免产生额外的阻抗。

4GHz的频率在真空中的1个波长为75mm,在印刷电路板上的波长比真空中更短,会有所谓的电路板上缩短率,加上电气上的长度只有该波长的1/2,几乎是可以忽略的长度,结果造成图案之间的距离变得非常短,所以必需尽量选用小型元件,设计电路基板图案时必需动作频率列为最优先考虑。

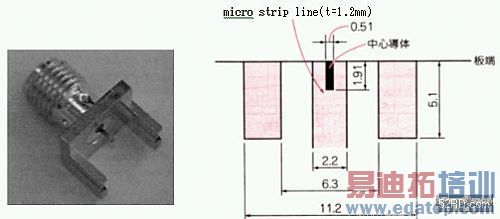

照片2是本电路使用的SAM连接器外观,它是Johnson components公司开发的End launch connector。对micro strip line而言,SAM的中心导体尺寸非常小,因此可以达成无阻抗暴增之虞的传输特性。图35是SAM连接器的电路基板图案,以及中心导体尺寸与基板厚度为1.2mm时的micro strip line宽度。

照片2 SAM连接器的外观 图35 照片2 SAM连接器的foot pattern

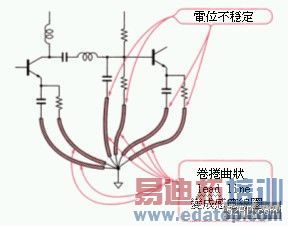

Audio电路大多采用单点接地(图36),类似RF电路的单点接地导线会成为电感器(inductance),使得各元件的接地端子之间电位变得非常不稳定,所以基板图案采用full ground设计,利用基板的背面与内层形成所谓的传输线路ground plain结构,此外与ground 连接的via hole会成为无法忽视的阻抗,设计上必需特别注意。

图36 Audio电路常见的单点接地

电源与功率电路基板导线设计

a.面封装型线性调整器的散热图案

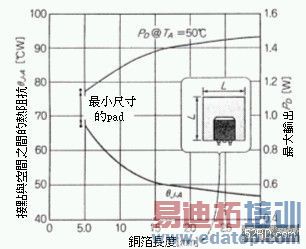

接着介绍输出电流1.0A低饱和型线性调整器(linear regulator)散热图案设计技巧。三端子调整器构成元件非常少因此广被使用,图37是由面封装型线性调整器NCP1117构成的降压电路;图38是降压电路基板图案。

图37 线性调节器构成的降压电路 图37 线性调节器构成的降压电路

旁通电容器(bypass condenser) C1、C3封装在半导体的输出入端子附近,NCP1117为面封装型半导体,使用电路基板图案作散热。图39是NCP1117的散热pattern大小与容许电力-热阻抗的关系,例如输入8V,输出5V,输出电流400mA时,半导体的损失利用输出、入的电压差(8V-5V=3V),乘上输出电流后等于3V×0.4A=1.2W,根据图39可知NCP1117需要7mm正方以上的散热pad。直接与散热pad连接时,如果输出平滑电解电容C4的电路基板图案太宽时,热量会经由图案传导至电容器造成电解电容温度上升,所以散热pad与C4的基板图案必需案配合输出电流,尽量降低导线图案的宽度。

图39 NCP1117的散热pattern大小与容许电力-热阻抗的关系

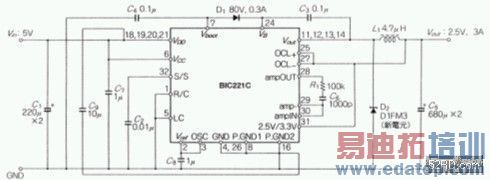

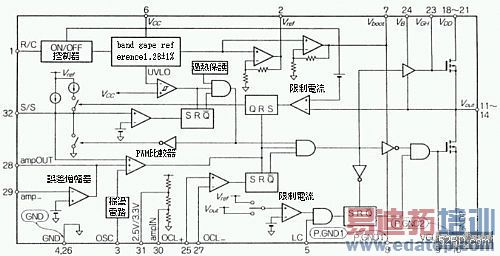

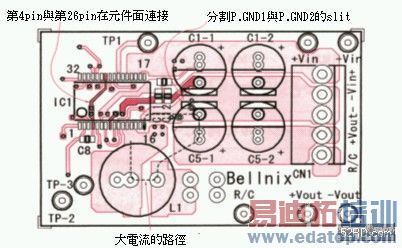

同步整流step down converter BIC221C与控制电路,以及MOSFET驱动电路三者同时封装成一体,本电路的动作频率为300kHz,输入5V,输出2.5V/3A。图40(a)是step down converter电路图;图40(b)是BIC221C的内部方块图;图41(a)是电路基板元件面图案。

如图40(b)所示,BIC221C内部方块图所示第4,6号脚架的GND,与第8号脚架的P.GND1、第16号脚架的P.GND2明确分隔,如果按照图40(a)电路图指示,直接描绘含盖上述脚架配线图案的话,可能会造成误动作与噪音增加等后果,因此设计电路基板图案时,必需将第8号脚架的P.GND1、第16号脚架的P,GND2分开,避免第4,6号脚架GND大电流流动。具体方法如图41所示,GND的第4,6号脚架在元件面连接,P.GND1的第8号脚架再与銲接面连接,大电流从C5通过P.GND2的第16号脚架,再从Vout(11,12,13,14pin)通过L1流入C5,P.GND1的第8号脚架从C1设置slit作连接,因此连接与第4,6号脚架的GND的图案不会有大电流流动。

(a)电路图

(b)BIC221C的内部方块图

图40 同步整流式step down converter BIC221C构成的step down converter

(a)元件面

(b)銲接图

图41 2.5V/3.3A输出的DC-DC converter电路基板图案

b. 光学耦合器构成的gate驱动电路基板图案

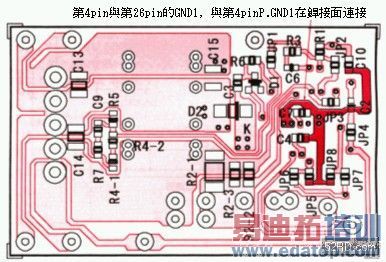

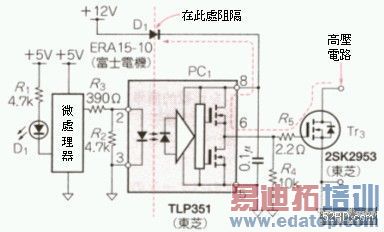

为避免控制电路遭受破坏,因此图42将光学耦合器TLP351与二极管构成的控制电路,以及功率MOSFET分离。

图42 photo coupler构成的gate驱动电路

图43 gate驱动电路的基板图案,光学耦合器的光学二极管单元属于电流驱动,光学电晶体与功率MOSFET等gate驱动单元则是电压驱动,所以光学耦合器封装在功率MOSFET附近,此时必需避免光学二极管的正、负极的平行导线Ⓐ部位面积变大。

图43 gate驱动电路的基板图案

c. 专用IC构成的gate驱动电路基板图案

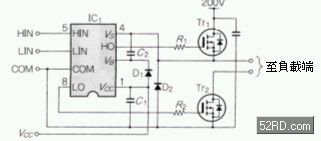

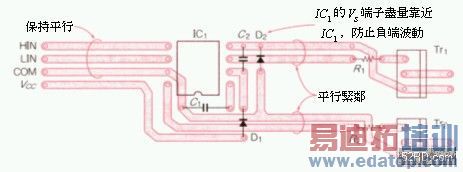

IR2011 8pin驱动IC内嵌high side与low side的gate驱动电路,属于D级audio增幅器与DC-DC converter的gate驱动器。

图44是专用IC的构成的gate驱动器电路;图45是驱动电路的基板图案。

虽然设计上要求gate驱动IC尽量靠近功率MOSFET设置,远离功率MOSFET设置的场合,为避免high side的source电位波动,造成IC1第4脚架V5的负电位波动,所以需将二极管D2设在gate驱动IC附近。

此外为防止Tr1、Tr2误动作,因此source与gate的导线尽量邻接,此外控制信号的输入图案与COM图案两者必需平行设置。

图44 专用IC的构成的gate驱动电路

图45 专用IC的构成的gate驱动电路的基板图案

数位电路基板导线设计

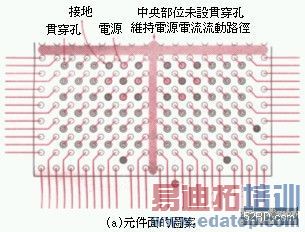

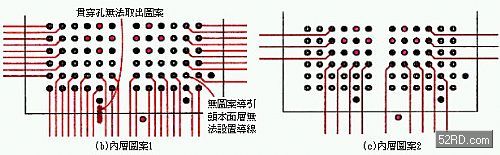

a.从BGA抽出图案、层数的估算技巧

图46的电路基板图案是以三孔方式作间距1.27mm,256pin full grid BGA佈线。此处假设BGA外侧5列需抽出信号线并留下电源与接地,如图46所示基板若有三层的话就能够达成以上要求;如果加上銲接面上的平滑电容等小型元件、电源层、接地层,电路基板总共需要6层。

导线抽出用贯穿孔(through hole)从BGA的中心点观之,它的外侧并未设置任何图案,BGA的中心十字上也未设置任何贯穿孔,如此设计主要目的是为确保BGA中心的电源电流流入路径。

有关电源阻抗的降低,建议读者尽量利用贯穿孔将电源连接至接地层,而且理论上最好每根脚架都拥有一个贯穿孔,此外平滑电阻则尽量设在电源贯穿孔附近。使用FPGA等可程式元件基板作高密度封装时,配合基板图案的布线进行脚架排列设计,可以缩减信号佈线层,尤其是考虑量产时的制作成本上述方法非常有效。

表2是BGA封装时抽出图案的列数与层数的估算结果,所谓抽出列数是指BGA要求的信号布线图,也就是说BGA外围的球(ball)列。通常电源脚架与内层连接无法抽出导线,所以无法列入计算范围,如果第2球列设有电源脚架时,电源的贯穿孔会影响导线的抽出,此时必需增加布线层数。表3是pin之间3条与5条贯穿孔的最小加工尺寸一览。

最低导线层数

pin之间

3条

pin之间

5条

(a)间距1.27mm的BGA

3条pin之间

5条2列以下1层1层3列2层4~6列---2层4~6列3层4~6列4层4~6列5层

表2 从BGA拉出的信号线列数与印刷电路板必要的层数

3条pin之间

5条pattern宽度0.150.1pattern间隔0.150.125land间隔(外层)0.250.15land间隔(内层)0.200.15pattern-land间隔0.150.125land-pad间隔0.2250.225pattern-pad间隔0.1750.125through hole直径0.350.25land直径(外层)0.650.4land直径(内层)0.750.4

表3 pin之间3条与5条贯穿孔的最小加工尺寸一览

b.存储器周边布线图案最小化技术

电路基板双面封装存储器时只要周详的事前规划,一般都可以缩减基板的布线图案。基本手法是不改变动作的前提下,掌握信号特性使用替代功能性的电路连接,如此一来电路图设计阶段,替代布线就可以大幅缩减基板正、背面的布线图案,例如资料与位址信号使用替代性布线设计,通常动作功能不会受到影响。

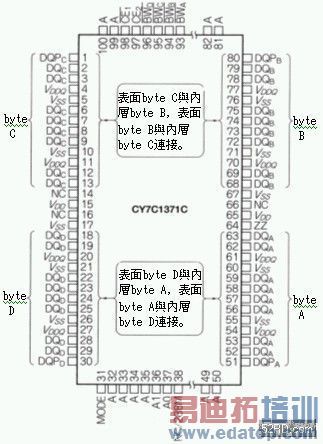

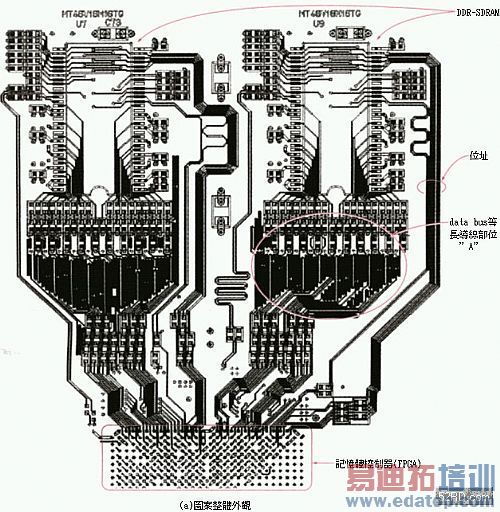

图47是data bus宽32位元的SSRAM CY7C1371C-100AC,封装于基板正、背面的的布线实例。虽然图48的构想可以获得高效率的布线图案,不过元件封装时的电路基板热传导极易恶化,而且还会有銲接不良、电路基板翻翘之虞,因此设计基板布线图案时,必需与封装业者沟通调整温度profile,同时确认可替代与不无法替代的脚架,依此数据利用CAD进行各种佈线组合的检讨,例如data bus与byte enable等信号,虽然无法单独替代基板布线,不过若是set状态时就能够作替代布线设计。

此外基板正、背面的分岐后的佈线佈线长度,如果是等长而且是最短化时,它还能抑制反射的影响。一般常用的存储器,可以依照下列基准选择替代信号:

▶SDRAM

Data:可替代(以DQM与set替代)

DQM:可替代(以DATA与set替代)

Address:不可替代(因为设定mode resistor必需使用位址)

BA:可替代

控制线:不可替代

▶SSRAM(Synchronous SRAM)

Data:可替代(以BWE与set替代)

BWE:可替代(以DATA与set替代)

Address:部份无法替代(已经使用ADV信号作burst access时,下方2位元无法替代)

控制线:不可替代

图47 可封装32位元data bus的SSRAM多层基板图案

图48 CY7C1371C SSRAM的脚架定义

c. 消除DDR-SDRAM资料bus timing误差的佈线图案

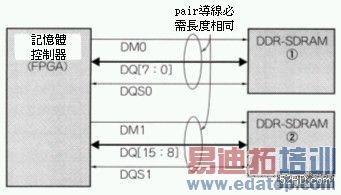

如图49所示DDR-SDRAM的资料信号DQ[0:7]与master信号DM,具有strobe信号DQS,DQ[0:7]与DM则latch DQS信号的站立、下降的端缘,例如以400MHz动作时资料会以2.5ns切换。

存储器的输出随着各位元会有所谓的固体差,根据Micron公司提供的DDR-SDRAM MT46V16M16-5B技术资料显示,最恶值的8位元有效资料期间有1.35ns的固体差,若加上基板上布线图案长度差的话,有效资料期间更加缩减。

图49 存储器控制器与存储器之间要求导线长度必需相同的信号

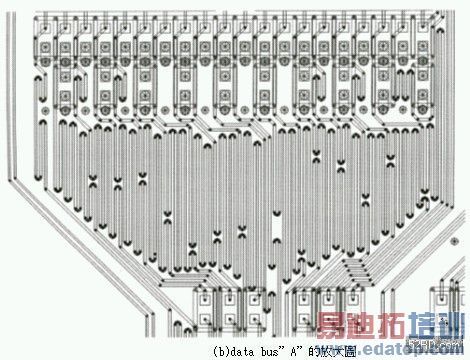

为获得1.3ns以上有效资料期间(亦即0.05ns),导线长度误差在7.5mm以内必需等长度布匹线,不过实际设计电路基板图案基于严谨考量,通常会作导线长度误差2.54mm以内的等长布线指示(图50);表4是图50电路基板图案的导线长度误差一览。

由于信号Level会变成SSTL2,因此导线阻抗设为50Ω,此外Altera公司的Stratix系列的DQS是在元件内部执行,因此电路基板图案必需作等长布线设计,不过进行位相控制的场合,必需采用其它类型的图案设计。

等长

group①

﹝13﹞65.11DDR0_D﹝12﹞65.176DDR0_D﹝11﹞65.179DDR0_DQ﹝10﹞65.013DDR0_DQ﹝9﹞65.046DDR0_DQ﹝8﹞65.113DDR0_DQS165.149DDR0_DM167.24等长导线误差2.227

等长

group②

表4 导线(图50)的长度误差

图50 DDR-SDRAM与存储器控制器的电路基板图案

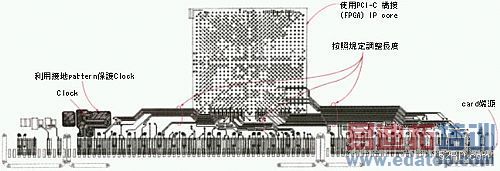

d. PCI/PCI-X的bus电路图案

表5是有关PCI/PCI-X电路图案的长度与阻抗规范。由于PCI-X bus主要是规范PCI元件至card edge的电路图案长度最大与最小值,因此电路图案必需类似图51的设计作绕道layout。利用FPGA构成PCI device的场合,为符合上述布线长度的规范,必需注意脚架的设置。

使用标准PCI-IP时,可以根据IP厂商提供的constrain filer(脚架规范)进行脚架设置Layout,除此之外图案阻抗也有标准规范,此时必需配合基板的层结构决定图案的宽度,clock pattern通常利用接地作保护(guard)。表6是图51电路基板图案的长度规范摘要。

项目

PCI-XPCI最小最大最小最大CLK信号导线长度60.9666.0460.9666.0432位元bus信号导线长度19.0538.1---38.1扩充64位元bus信号导线长度44.4569.85---50.8RST信号导线长度19.0576.2------board阻抗特性(0Ω无负载时)57±10%60~100信号传输延迟(ps/mm)5.91~7.485.91~7.48

表5 PCI bus与PCI-X的advertising card导线长度规范

图51 PCI元件至card端源基板图案

表6 图51的pattern长度

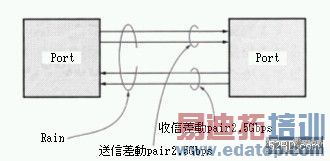

e. 可传输2.5Gbps差动信号的PCI-Express电路基板图案

虽然PCI bus为32位元或是64位元宽的parallel bus,然而PCI-Express却是由serial bus构成,接着再用一对的差动信号,以2.5Gbps速度进行通信(图52)。差动信号的送信与收信为set时称为Lane。由于PCI-Express的信号传输规范是以1/4/8/16/32的Lane数作定义,因此设计上必需考虑传输频宽才能选择Lane数。

图52 PCI-Express的rain结构

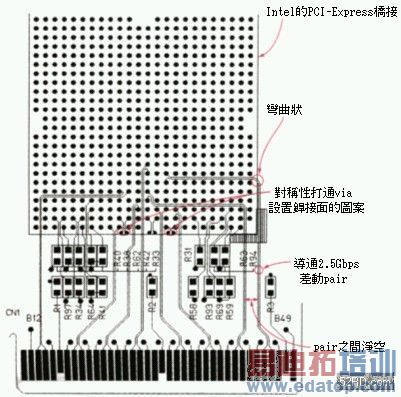

此处假设PCI Express/PCI-X桥接(bridge)41210(Intel)可以支援1/4/8的Lane,依此介绍PCI-Express 8 Lane高速差动信号的电路基板图案设计技巧。

图53是利用8 Lain连接PCI-Express与PCI-Express桥接时的基板图案,如图所示它是利用图案之间的间隔与宽度,调整差动pair与构成pair的一条Line的阻抗,藉此维持信号品质(Signal Integrity)。

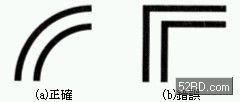

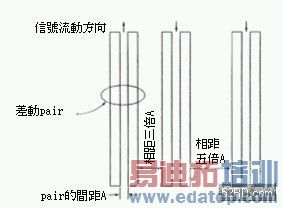

表7是PCI-Express的差动收信端输入阻抗规范,PCI-Express必需根据上述规范差动pair内作等长佈线设计;表8是PCI-Express的阻抗规范,PCI-Express用电路基板图案弯曲的场合必需作R角折弯设计,因为差动pair维持等距间隔,可以有效抑制阻抗变动(图54)。Layout时图案尽量在基板表层环绕。此外每个via会使信号衰减0.5~1.0dB,为防止信号劣化设计上via的数量越少越好。使用复数Lane时差动pair必需邻接设计,pair与pair之间呈间隔状区隔。相差动pair之间的场合,pair与pair之间的间隔是差动之间5倍距离;非同相差动时pair与pair之间的间隔是差动之间3倍距离(图55)。

图53 利用8 Lain连接PCI-Express与PCI-Express桥接时的基板图

表7 PCI-Express的差动收信端输入阻抗规范(单位:Ω)

(a)PCI-Express收信端的导线长度(容许误差以0.127mm作指示)

(b)PCI-Express送信端的导线长度(容许误差以0.127mm作指示)

表8 PCI-Express的差动收信端输入阻抗规范(单位Ω)

图54 pattern不可作直角弯曲

图55 差动pair邻接时,pair之间的间距

上一篇:串行/解串器与铜质千兆连接:串行/解串器如何通过铜质千兆连接技术取代光学数据连接(

下一篇:将 PWM 信号更改为 DC(英)