- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

运用FPGA架构可配置处理器建立高效能伺服器平台

在资料中心这个应用领域中,正发生着基础架构移转的现象,同时为资讯科技(IT)的专业人士建立了新的机会与挑战,其中有许多因素导致这种移转现象的发生,首先,运用网页技术的应用已经居于主导的地位,带来了新的能力并巨大的增进了生产力,建立了具有高度分散式处理能力,且具备透通性的架构;其次,事业的持续运作与灾害的復原准备的重要性逐渐提高,对于网路与资料的可存取性、可靠性与完整性的需求也日益提高;第三,多用途与尖端的运算应用也对资源最佳化的需求不断地增加;最后,也是最重要的是更高速度网路的佈建与十亿位元乙太网路与百亿位元乙太网路的传输流量,已经造成在容量、效能与利用率等因素上必需进行复杂的折衷处理,以便推动运算效能使其能够超越它的极限。

在现今的商业环境下,伺服器必须能够在商业上的关键性应用与功能中,满足在可预测性、效能与效率上逐渐上升的需求。传输控制协议(TCP)技术具有其与生俱来的复杂性,并受到高度的分散式处理,以及新式资料中心模式中以效能来驱动的本质所影响,在复杂度上更为提升,也因此造成网路超载、延迟与效能的减低,而应用本身具有各种不同的特性,也对TCP技术造成巨大的冲击,例如配合应用处理工作时,无论是网页存取还是具安全性的网页存取,都须同时进行TCP连接、密集的联接设定与分解,以及安全的交易,换言之,对电子邮件、资料库存取、丛集式服务与档案传输等都会造成延迟,并对I/O需求更为密切,事实上,这也代表着在伺服器端需要更高速的互联架构。

什么是解决这些问题的最好方式呢?便是为最高端的伺服器跨越整个应用传输链来进行加速与资源最佳化,建立一个可以进行减轻、控制与局部化网路层负担的平台(参见图1),这样的平台需要採用硬体式架构才能够支援上百万次的同时TCP连接,每秒有数百万次的连接,以及结合每秒几十万次交易、数十亿位元的第七层(应用层)处理量,使用RDMA技术的快速互联架构能力来全力运用伺服器到伺服器之间的通讯,以及传输超过1 Gbps的GZIP/Deflate压缩来启动商业上的关键性应用。

图1 – 当今最现代化的资料中心环境需要一个可以进行减轻、控制与局部化网路负担的平台。

过去也曾经有一些作法在开发像这样的平台,通常是使用微处理器、特定应用积体电路(ASIC)或特定应用特殊产品(ASSP)来处理,然而,微处理器缺乏能够处理数十亿位元交易的能力,ASIC则是在对产品的成本与及时上市压力下根本就可以不去考虑,ASSP则缺乏在实行这种平台时的弹性需求,只有採用FPGA架构的可配置处理器才能达到同时满足效能、弹性、成本与产品及时上市的需求,才能在这种具有挑战性的应用中得到成功。

这篇文章将描述上述这类由Crescendo网路公司所开发的平台。在这个系统中採用的FPGA架构处理器是用于解析与建立档头、封包区隔、交换控制、复杂记忆体管理计算与TCP参数计算。这个平台称之为Maestro平台,运用处理器的弹性来做为核心的TCP卸载引擎,以及更复杂的系统层级功能,当FPGA资源还游刃有余之时,包括晶片上记忆体、锁相迴路与高速介面,都可用于支援其他的功能,如此一来,这个平台将打破一般常发生在前端与后端应用伺服器与资料中心的应用网路中,在应用开发上所发生的障碍。

Maestro平台使用了Crescendo的Short Life Transaction(SLT™)伺服器效能增进技术,能够提供完整的TCP终止、SSL卸载与外部资料压缩,它也可透过RDMA互联架构提供高速后端服务传递,来在乙太网路上支援RDMA,此外还可控制容量的需求与局部化需求来最佳化网路的运作能力与频宽,如此一来,企业可以从增加伺服器的运算资源、减少外部频宽需求、缩减应用程式延迟,以及较低的投入资金与运作成本上得到效益。直到此时,因为有了这个平台,资讯专业人士们可以透过高速互联的优势,来跨越完整的传输链,启动具商业关键性的应用,并将延迟从数毫秒缩减为数微秒。

Maestro平台变成一个基本系统,并具有三个可选择的模组。基本系统包含Crescendo CN5000E系列,包括应用前端的功能与Maestro管理模组,这是一个嵌入式的单元管理系统,用来加速与简化供应、启动与监控工作。选择性的模组包括Maestro安全(SSL、DDoS)、Maestro压缩与Maestro后端加速模组,这个平台是由Crescendo网路公司以超过60个特定应用引擎为基础的FreeFlow™架构所构成,这个架构可提供一个快速、强而有力与具延展性的基础,以对未来的系统成长提供足够的弹性与效能。

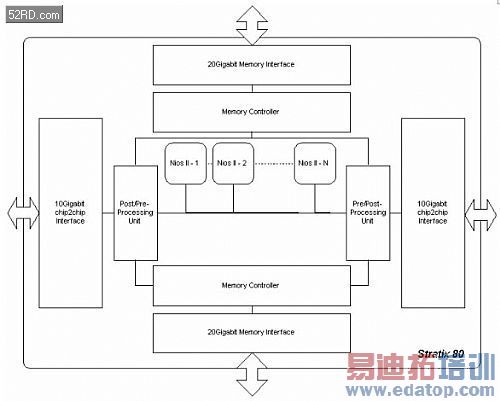

共有八个Altera的Nios处理器嵌入在Altera的Stratix FPGA中,用于执行在Maestro平台上的核心功能,其中包括TCP加速功能、复杂记忆体管理功能、档头压缩闸口与档头解析,其他在Stratix FPGA中的晶片资源则用于针对高速记忆体介面与控制,以及搭配百亿位元网路媒体独立介面(XGMII)用于晶片与晶片之间的通讯,与做为系统封包介面第四层级(SPI 4)元件。图2展示了在Maestro平台上其中一个Stratix FPGA的方块图。

图2 – 这个方块图展示了在Maestro平台上其中一个Stratix FPGA的内部架构,其中Nios II处理器执行核心的功能,包括TCP加速功能、档头解析与复杂记忆体管理功能。

当在设计Maestro平台时,Crescendo考虑了许多种选项,其中包括微处理器、ASIC、ASSP与其他的可编程逻辑,就如前文所述,ASIC的产品开发成本太高,且易造成产品上市时间的延误,ASSP则缺乏足够的弹性,现成的微处理器则功能太简单,无法支援数十亿位元的频宽需求来满足效能上的规格,最后,当在比较其他的可编程逻辑解决方案时,Altera的可配置软式处理器/高效能的FPGA架构解决方案能够提供更好的效能、更多更有弹性的PLL、更多为数众多且易于配置的记忆体模块,以及拥有最佳的FPGA架构。

Crescendo使用第一代的Nios处理器来开发Maestro平台,但它于最近转换到新推出的第二代Nios II处理器来获取更佳的效能与更多可利用的逻辑空间。从Nios处理器转移到Nios II处理器加倍了系统的效能,并增加了平台可以控管的交易量,从每秒处理数十万的交易变成可达到更快速的每秒处理数百万的交易量。能够同时支援每秒处理数百万个http交易量的能力,是Maestro平台的关键需求。

除了在效能、弹性与产品及时上市的优势之外,Nios II处理器搭配在Stratix FPGA中,让Crescendo能够轻易地增加新的功能来升级它的Maestro平台,尽管Nios II软式处理器拥有高效能,但它所佔的面积仍然很小,释放出了FPGA中多余的空间来嵌入其他的功能,如此一来,便可以极具成本效益的方式来执行系统升级,而不需要大幅地进行系统重新设计。Crescendo也打算在未来的产品开发上使用Stratix II FPGA,将可提供更多效能上的提升。

增加伺服器的能力与提升IT系统的需求,以及採用TCP架构的网路来控管数十亿位元的资料,将可以拓展企业资料中心的能力,现今的伺服器必须能够满足可预测性、效能与效率需求的成长,以支援至关重要的应用。Crescendo的Maestro平台 透过採用Altera的Nios II可配置软式处理器与Stratix FPGA,来提升弹性、效能、成本、产品及时上市与延展性上的优势,用伺服器加速与资源最佳化来让企业网路效能达到极限。(Steve Elston为美国Crescendo网路公司总裁,Martin S. Won则任职于Altera公司)

上一篇:新型负载管理元件优势概论

下一篇:交错式功率级:不再仅适用于降压转换器